Изобретение относится к телевидению и может быть использовано для цифровой передачи изображений методом дифференциальной имиульено-ко- довон модуляции.

Цель изобретения - повышение помехоустойчивости

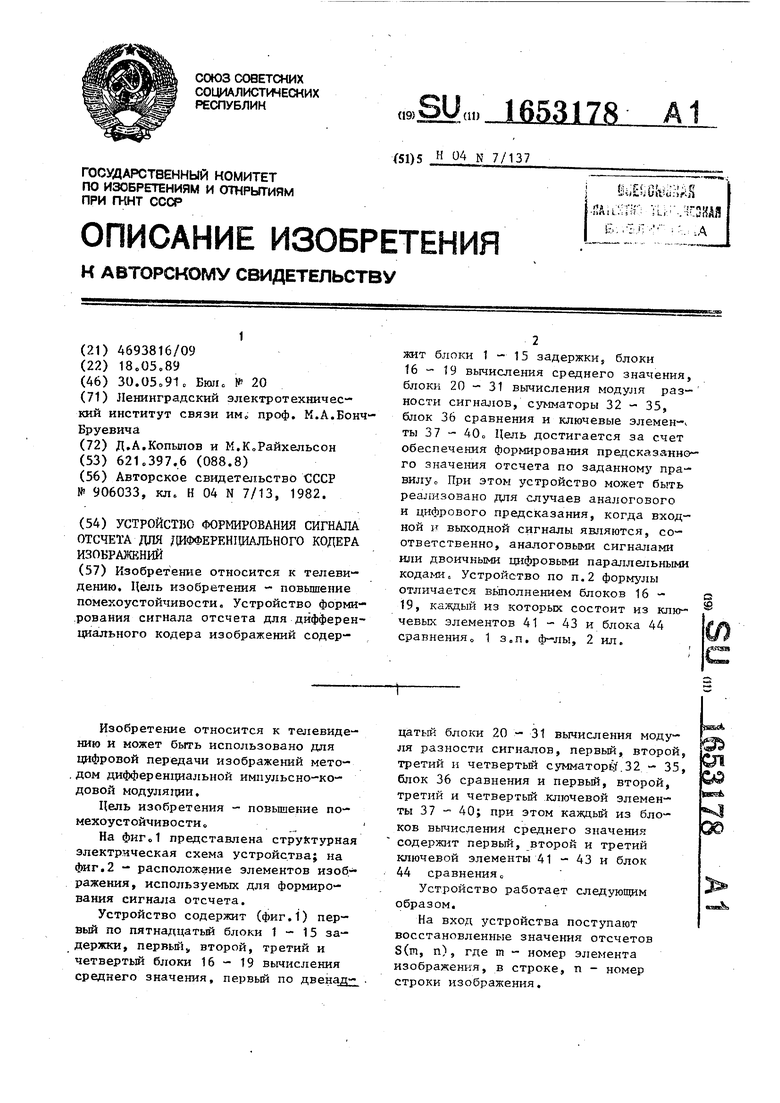

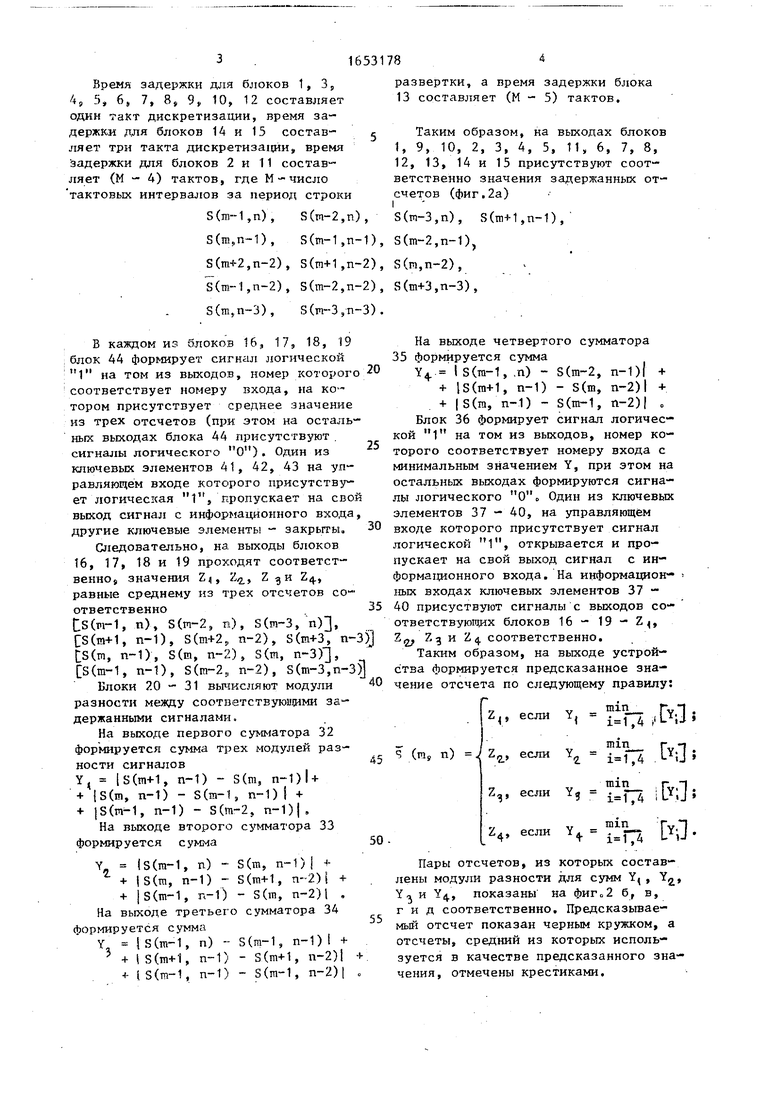

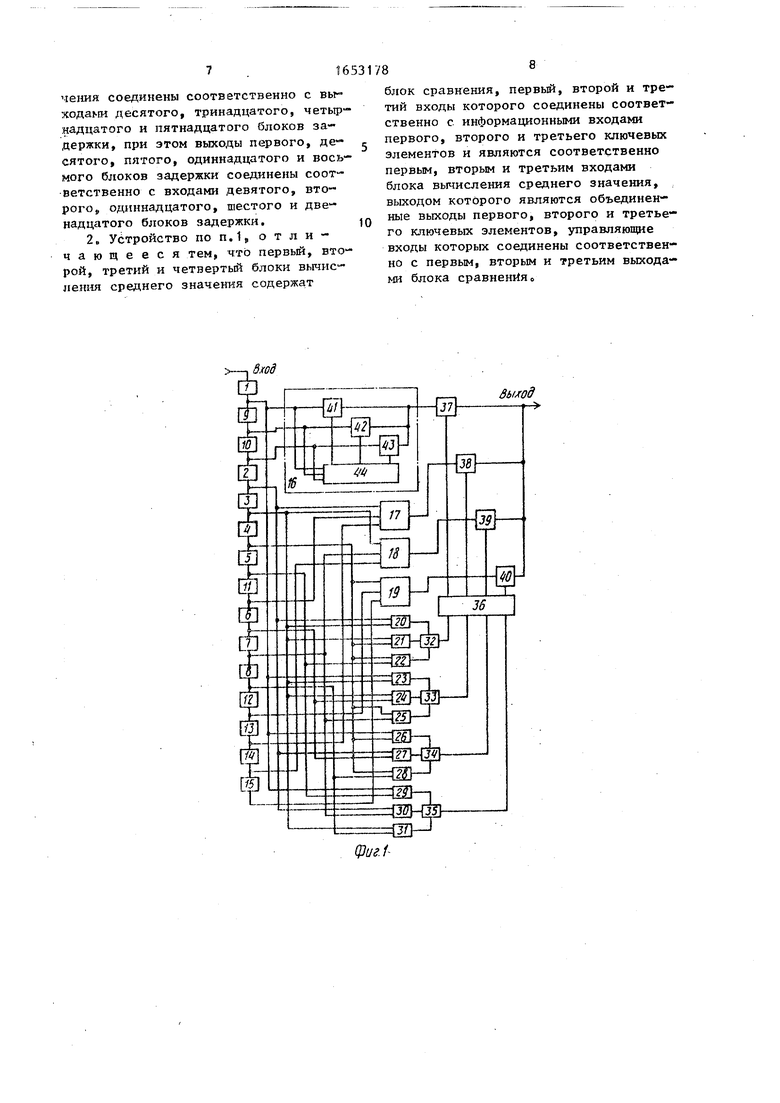

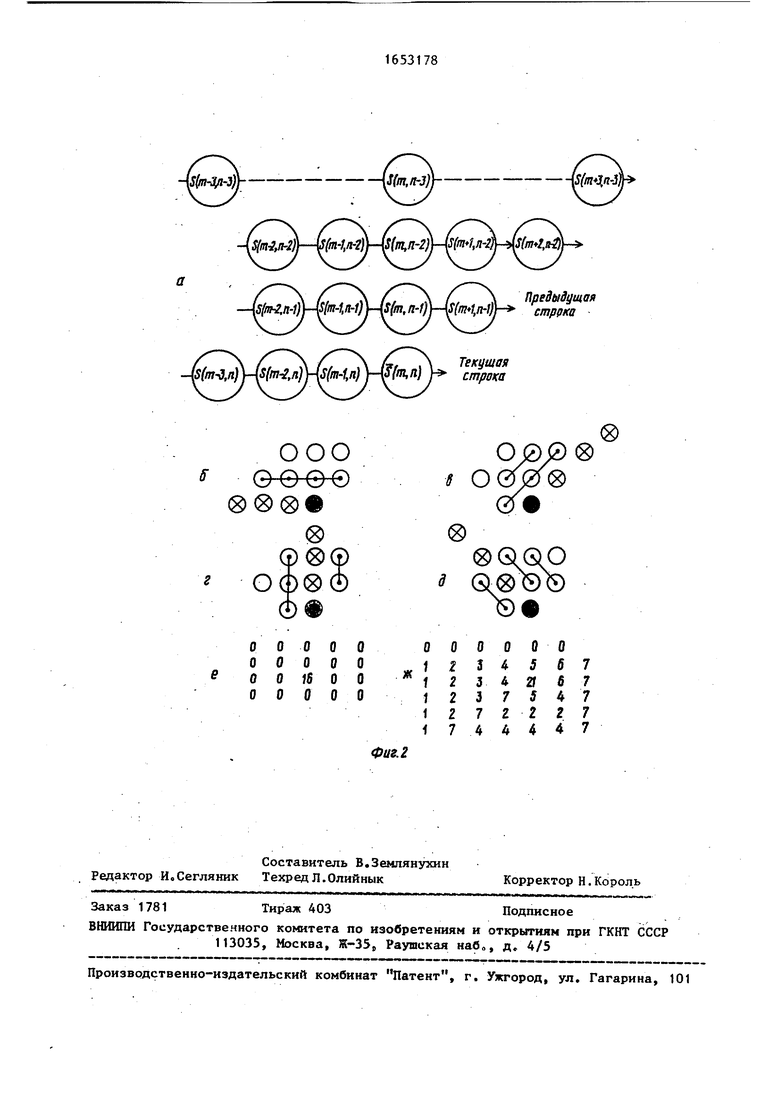

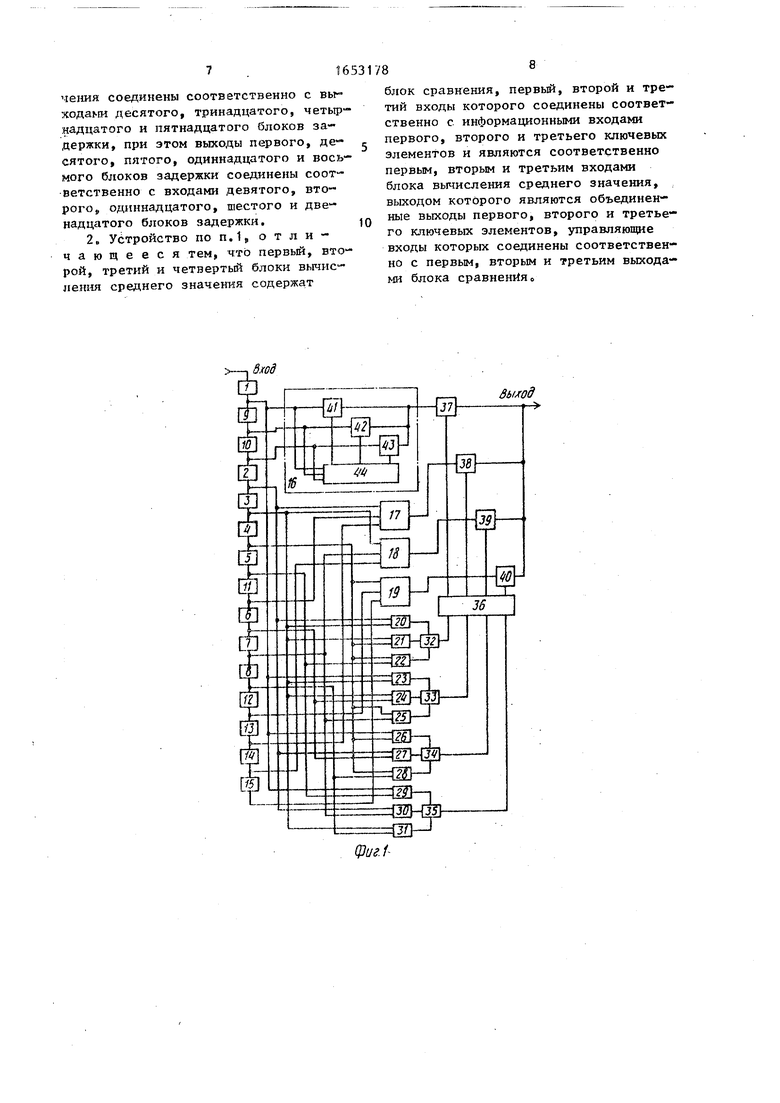

На фиг.1 представлена структурная электрическая схема устройства; на фиг.2 - расположение элементов изображения, используемых для формирования сигнала отсчета.

Устройство содержит (фиг.1) первый по пятнадцатый блоки 1-15 задержки, первый второй, третий и четвертый блоки 16-19 вычисления среднего значения, первый по двенад,цатмй блоки 20-31 вычисления модуля разности сигналов, первый, второй, третий и четвертый сумматору .32 - 35, блок 36 сравнения и первый, второй, третий и четвертый ключевой элементы 37 - 40; при этом каждый из блоков вычисления среднего значения содержит первый, второй и третий ключевой элементы 41 - 43 и блок 44 сравнения,.

Устройство работает следующим образом.

На вход устройства поступают восстановленные значения отсчетов S(m, n), где m - номер элемента изображения, в строке, n - номер строки изображения.

ив.

сл

0$

00

31b53

Время задержки для блоков 1, 3, 4, 5, 6, 7, 8, 9, 10, 12 составляет один такт дискретизации, время задержки для блоков 14 и 15 состав- 5 ляет три такта дискретизации, время задержки для блоков 2 и 11 составляет (М - 4) тактов, где М - число тактовых интервалов за период строки

S(m-1,n), S(rn-2,n), S(m,n-1), S(m-1,n-1) S(m+2,n-2), S(tn+1,n-2) S(m-1,n-2), S(m-2,n-2) S(m,n-3), S(n-3,n-3)

В каждом из блоков 16, 17, 18, 19 блок 44 формирует сигнал логической 1 на том из выходов, номер которого 20 соответствует номеру входа, на котором присутствует среднее значение из трех отсчетов (при этом на остальных выходах блока 44 присутствуют сигналы логического О). Один из ключевых элементов 41, 42, 43 на управляющем входе которого присутствует логическая 1, пропускает на свой выход сигнал с информационного входа, другие ключевые элементы - закрыты. 30

Следовательно, на выходы блоков 16, 17, 18 и 19 проходят соответственно, значения Z, Z, Z эи Z, равные среднему из трех отсчетов соответственно35Јs(n-1, n), S(n-2, n), S(tn-3, л), ЈS(m+1, n-1), S(m+2, n-2), S(n+3, n-3)J ЈS(m, n-1), S(n, n-2), S(m, n-3), S(m-1, n-1), S(m-2, n-2), S(m-3,n-3)

Блоки 20 - 31 вычисляют модули 40 разности между соответствующими задержанными сигналами.

На выходе первого сумматора 32 формируется сумма трех модулей разности сигналов45 Y, |S(m+1, n-1) - S(m, n-1) 14- + |S(m, n-1) - S(m-1, n-1) | + + |S(m-1, n-1) - S(m-2, n-1)|.

На выходе второго сумматора 33 формируется сумма50

Y IS(m-1, n) - S(m, n-1)| + |S(m, n-1) - S(tn+1, n-2) | + + |S(m-1, n-1) - S(m, n-2)| .

На выходе третьего сумматора 34

55

формируется сумма

Y I S(m-1, n) -S(m-1, n-1) I +

+ I S(m-H, n-1)- Sdn-t-1, n-2)| +

+ IS(n-1, n-1)- S(m-1, n-2)| .

78

развертки, а время задержки блока 13 составляет (М - 5) тактов.

Таким образом, на выходах блоков 1, 9, 10, 2, 3, 4, 5, 11, 6, 7, 8, 12, 13, 14 и 15 присутствуют соответственно значения задержанных отсчетов (фиг.2а) i

S(m-3,n), S(m-H,n-1), S(m-2,n-1)

S(n,n-2), S(m+3,n-3),

На выходе четвертого сумматора 35 формируется сумма

Yf IS(ra-1, n) - S(m-2, n-1)| + + |S(ro+1, n-1) - S(m, n-2) I 4- + S(n, n-1) - S(m-1, n-2)| о

Блок 36 формирует сигнал логической 1 на том из выходов, номер которого соответствует номеру входа с минимальным значением Y, при этом на остальных выходах формируются сигналы логического О. Один из ключевых элементов 37-40, на управляющем входе которого присутствует сигнал логической 1, открывается и пропускает на свой выход сигнал с информационного входа. На информацион- ных входах ключевых элементов 37 - 40 присуствуют сигналы с выходов соответствующих блоков 16 - 19 - Z, iqj , и Z 4 соответственно.

Таким образом, на выходе устройства формируется предсказанное значение отсчета по следующему правилу:

Ч (т, n) J

Пары отсчетов, из которых составлены модули разности для сумм Y, , Y, Y, и Y., показаны на фиг„2 б, в, гид соответственно. Предсказываемый отсчет показан черным кружком, а отсчеты, средний из которых используется в качестве предсказанного значения, отмечены крестиками.

51

Устройство может быть реализовано как для случая аналогового предсказания, когда входной и выходной сигналы являются аналоговыми, так и для случая цифрового предсказания, когда входной и выходной сигналы представ- ляют собой двоичные цифровые парал- лельные коды.

Формула изобретения

1. Устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее первый блок задержки, вход которого является входом для восстановленного значения цифрового отсчета текущего элемента изображения, последовательно соединенные второй, третий, четвертый и пятый блоки задержки, последовательно соединенные шестой, седьмой и восьмой блоки задержки, двенадцать блоков вычисления модуля разности сигналов, первый, второй, третий и четвертый сумматоры, выходы которых соединены соответственно с первым, вторым,третьим и четвертым входами блока сравнения, первый, второй, третий и четвертый выходы которого соединены соответственно с управляющими входами первого, второго, третьего и четвертого ключевых элементов, выходы которых объединены и являются выходом сформированного значения сигнала текущего отсчета, при этом выход первого блока задержки соединен с объединенными первыми входами четвертого, седьмого и десятого бло- ков вычисления модуля разности сигналов, выход второго блока задержки соединен с объединенными первыми входами первого, восьмого и одиннадцатого блоков вычисления модуля разности сигналов, выход третьего блока задержки соединен с объединенными вторыми входами первого и четвертого блоков вычисления модуля разности сигналов и с объединенными первыми входами второго, пятого и двенадцатого блоков вычисления модуля разности сигналов, выход четвертого блока задержки соединен с объединенными вторыми входами второго и седьмого блоков вычисления модуля разности сигналов и с объединенными первыми входами третьего, шестого и девятого блоков вычисления модуля разности сигналов, выход пятого блока задержки соединен с объединенными вто5

0

1

0

5

0

5

0

5

0

5

786

pbff.ci входами третьего я десятого блоков вычисления модуля разности сигналов, выход шестого блока задержки соединен с объединенными вторыми входами пятого и восьмого блоков вычисления модуля разности сигналов, выход седьмого блока задержки соединен с объединенными вторыми входами шестого и одиннадцатого блоков вычисления модуля разности сигналов, выход восьмого блока задержки соединен с вторыми входами девятого и двенадцатого блоков вычисления модуля разности сигналов, выходы первого, второго и третьего блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами первого сумматора, выходы четвертого, пятого и шестого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами второго сумматора, выходы седьмого, восьмого и девятого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами третьего сумматора, а выходы десятого, одиннадцатого и двенадцатого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами четвертого сумматора, отличающееся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные девятый и десятый блоки задержки, одиннадцатый блок задержки, последова- ч тельно соединенные двенадцатый, тринадцатый, четырнадцатый и пятнадцатый блоки задержки, а. также первый, второй, третий и четвертый блоки вычисления среднего значения, выходы которых соединены соответственно с : информационными входами первого, второго, третьего и четвертого ключевых элементов, первые входы первого, второго, третьего и четвертого блоков вычисления среднего значения соединены соответственно с выходами первого, второго, третьего и четвертого блоков задержки, вторые входы первого, второго, третьего и-четвертого блоков вычисления среднего значения соединены соответственно с выходами девятого, одиннадцатого, седьмого и двенадцатого блоков задержки, третьи входы первого, второго, третьего и четвертого блоков вычисления среднего значекия соединены соответственно с вы- ходами десятого, тринадцатого, четырнадцатого и пятнадцатого блоков задержки, при этом выходы первого, десятого, пятого, одиннадцатого и восьмого блоков задержки соединены соответственно с входами девятого, второго, одиннадцатого, шестого и двенадцатого блоков задержки.

2, Устройство поп.1, отличающееся тем, что первый, второй, третий и четвертый блоки вычисления среднего значения содержат

блок сравнения, первый, второй и третий входы которого соединены соответственно с информационными входами первого, второго и третьего ключевых элементов и являются соответственно первым, вторым и третьим входами блока вычисления среднего значения, выходом которого являются объединенные выходы первого, второго и третьего ключевых элементов, управляющие входы которых соединены соответственно с первым, вторым и третьим выходами блока сравнения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала отсчета для дифференциального кодера изображений | 1979 |

|

SU906033A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство распознавания одиночных и групповых составных импульсных сигналов | 1984 |

|

SU1247775A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2009 |

|

RU2420005C1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

Изобретение относится к телевидению. Цель изобретения - повышение помехоустойчивости. Устройство формирования сигнала отсчета для дифференциального кодера изображений содержит блоки 1-15 задержки, блоки 16 - 19 вычисления среднего значения, блоки 20-31 вычисления модуля разности сигналов, сумматоры 32 - 35, блок 36 сравнения и ключевые элемен-- ты 37 - 400 Цель достигается за счет обеспечения формирования предсказанного значения отсчета по заданному пра- вилус При этом устройство может быть реализовано для случаев аналогового и цифрового предсказания, когда входной и выходной сигналы являются, соответственно, аналоговыми сигналами или двоичными цифровыми параллельными кодами. Устройство по п.2 формулы отличается выполнением блоков 16 - 19, каждый из которых состоит из ключевых элементов 41 - 43 и блока 44 сравнения,, 1 з.п. ф-лы, 2 ил. # (Л Ј«ЯЛ1

,6ход

выход

{sfa-fy-S))

ооо э-&©

ОС)®

00000

ооооо

О 0 16 О О

ооооо

f Л Предыдущая S(,n-l)) строка

Текущая строка

О

ж

| Устройство формирования сигнала отсчета для дифференциального кодера изображений | 1979 |

|

SU906033A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-30—Публикация

1989-05-18—Подача