I

Изобретение относится к вычислительной технике и может быть использовано при построении устройств переработки дискретной информации на цилиндрических магнитных доменах (ЦМД).

По основному авт. ев, № 690629 известен комбинационный двоичный сумматор , содержащий в каждом разряде логический элемент И-ИСКШЧАОДЕЕ ИЛИ, динамическую ловушку и аннигилятор ЦМД, выполненные из пермаллоевых аппликаций и расположенные на поверхности магнитоодноосной пленки с ЦМД, причем первый вход каждого логического элемента И-ИСКЛЮЧАЩЕЕ ИЛИ, кроме первого, соединен с первым выходом предыдущего логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые вход и выход каждого логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом и входом соответствующей динамической ловушки, а ,

.третий выход каждого логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с аннигилятором ЦНД С .

Недостатком такого сумматора является невысокое быстродействие, составляющее (п + 2,5) такта при сложении двух п-разрядных операндов и (п + 1) такт при сложении синхронно поступающих на его входы пар п-разрядных операндов.

10

Цель изобретения - повышение быстродействия комбинационного двоичного сумматора.

Поставленная цель достигается тем,

IS что устройство содержит токопроводящую аппликацию в форме петли, расположенную на поверхности магнитоодноосной пленки с ЦМД и магнитно связанную с двинамической ловушкой ЦМД

20 младшего разряда сумматора.

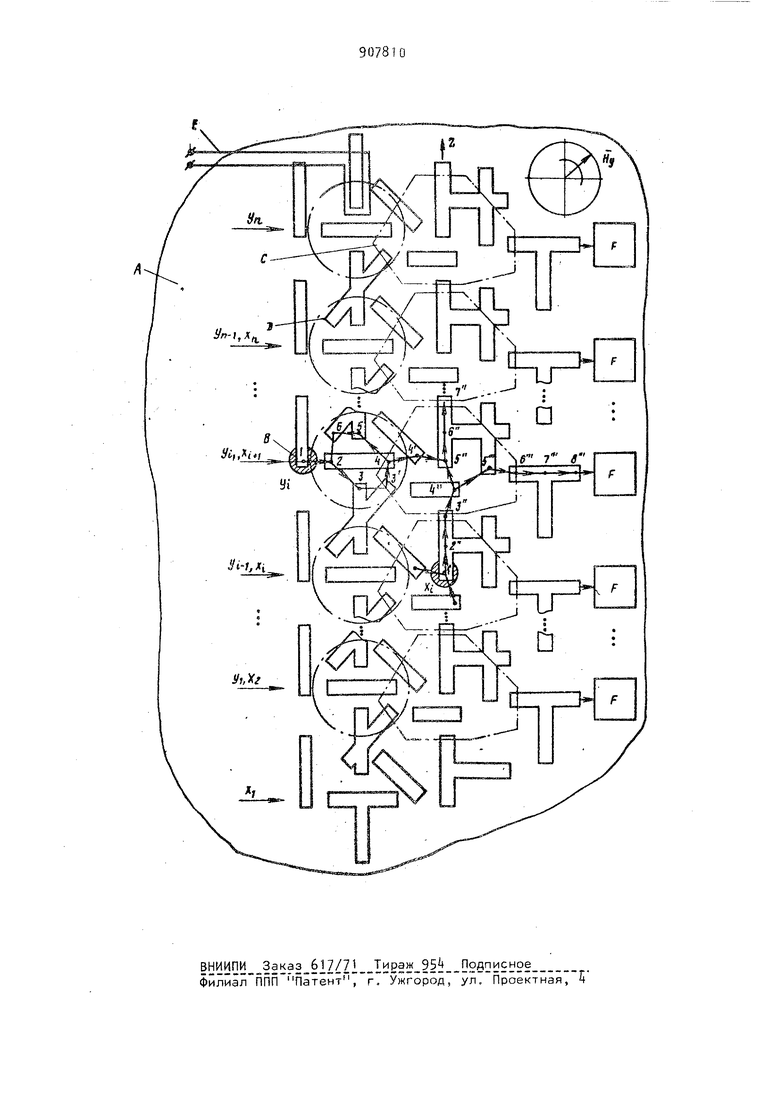

На чертеже изображена принципиальная схема комбинационного двоичного | сумматора.

39

Устройство содержит мэгнитоодноосную пленку А с ЦМД В, на поверхности которой расположены логические элементы И-ИСКЛЮЧАЮЩЕЕ ИЛИ С с двумя входами и тремя выходами, динамические ловушки Д, токопроводящая аппликация в форме петли Е и аннигиляторы ЦМД F.

Цифрами 1-8 обозначены позиции, записанные ЦМД во время их продвижеиия в сумматоре.

Цифрами 1,2,3,3 j, обозначены канал ввода j-ro разряда второго операнда и (i + 1)-го разряда первого операнда в i-тый разряд сумматора Цифрами 1 , 2 , З , обозначены канал ввода {-го разряда первого операнда и канал вывода результата порязрядного суммирования по

mod 2 с предыдущего. ( - 1)-го, разряда сумматора. Цифрами 2,3,3, 4,5,6 обозначена динамическая ловушка Д. Цифрами 5 . б . 7 обозначен канал вывода результата поразрядного суммирования по mod 2

Hi 1тго разряда сумматора. Цифрами 5

, , 8

обозначен канал вывода лишних доменов в аннигилятор ЦМД F. На первом выходе логического элемента в позиции 7 реализуется

функция Неравнозначность, а на втоf- / ром и третьем в позициях 5 и 6 ,

соответственно, .функция И..

Устройство работает следующим образом.

По параллельным входным каналам

Х ;У ) Х2 iVf сумматор поступает первый операнд, с

задержкой на 1 такт по параллельными входным каналам У ,,)и Xj , лц. Уу1 в сумматор поступает второй операнд, причем старшие разряды первого и второго операндов поступают, соответственно, по каналам Х( и У ,Х,. За два такта с момента появления первого операнда на входах суматора оба слагаемых сводятся разряд к разряду на расстояние, достаточное для взаимодействия ЦМД в одноименных разрядах. В течение первого такта в результате взаимодействия доменов на месте первого операнда остается результат поразрядного суммирования операндов по mod 2, но сдвинутый на один разряд в сторону младших разрядов по отношению к начальному положению второго операнда, от которого к этому времени в динамических

О4

ловушках Д остаются только переносы в старшие разряды. В течение второго такта сложения результат первого поразрядного суммирования по mod 2, взаимодействия с ЦМД переносов на выходах динамических ловушек, образует результат второго суммирования по mod 2, который при этом сдвигается еще на один разряд в сторону младших разрядов по отношению к начальному положению второго операнда, от которого к этому моменту времени остаются переносы в старшие разряды, образующиеся в результате этого суммирования по mod 2, и так далее до мо мента времени, когда в динамических ловушках не останется ЦМД-переносов, что говорит об окончании процесса сложения.

. Процесс образования результата слжения и переноса в старший разряд рассмотрим более подробно на примере i-ых разрядов операндов. В момент времени, когда ЦМД, соответствующий i-му разряду второго операнда, поступает на вход I-го разряда ра (позиция 1), ЦМД, ссютветствуииций i-му разряду первого операнда, поступает в позицию 1 на Н-аппликации , Отслеживая полюса аппликаций, еозникающие под действием вращаю14егося магнитного поля управления И. помянутые ЦМД перемещаются по траекториям 1-2-3-3 и 1 -2 3 , соответственно, и достигают позиций k и , из которых за счет взаимного отталкивания переходят на полюса 5 динамической ловушки и 5 Н-аппликации, соответственно, реализуя тем самым перенос в старший разряд и ноль на выходе i-ro разряда сумматора, так как ЦМД из позиции 5 поступает к аннигилятору доменов F. Если в одном из двух i-тых разрядов операндов ЦМД отсутствует, то присутствующий в .-том разряде другого операнда ЦМД, не испытывая отталкивающего воздействия, из позиции k (или 4 ) через четверть такта поступает в позицию 5 , откуда через половину периода появляется на выходе f-ro разряда сумматора в позиции 7 , реализуя тем самым единицу на выходе этого разряда. Случай с двумя нулями в i-тых разрядах операндов тривиален и поэтому не рассматривается.

В известном сумматоре младший разряд суммы операндов появляется на выходе сумматора z lepes два с половиной такта после поступления первого операнда на его входы, а старший разряд - еще через (п - 1) такт. Один такт также необходит для вывода из сумматора возможного переполнения старшего разряда. Быстродействие Сумматора при сложении двух п-разрядных операндов составляет (И+ 2,5) такта. Если же сумматор работает в синхронном режиме, т,е, очередная пара операндов на входы сумматора поступает через (п + 1} такт после поступления предыдущей пары операндов, то быстродействие схемы возрастает до (п + 1) такта на операцию о

Введение в схему известного сумматора токопроводящей аппликации в форме петли, предназначенной для уничтожения домена - переполнения старшего разряда суммы операндов, по зволяет на такт раньше вводить в сумматор следующую пару операндов, вследствие чего быстродействие выполнения операции сложения двух п-разрядных операндов возросло до (п 1 ,5) тактов, а при сложении синхронно поступакщих на его входы пар п-разряднцх операндов - до п тактов на операцию.

Формула изобретения

Комбинационный двоичный сумматор по авт. св. № 690629, о т л и чающийся тем, что, с целью повышения быстродействия сумматора, он содержит токопроводящую аппликацию в форме петли, расположенную на поверхности маГнитоодноосной пленки с цилиндрическими магнитимой доменами и магнитно связанную с динамической ловушкой цилиндрических магнитных доменов мпадашго разряда сумматора.

HcTO4HVKH информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 690629 (заявка № 2 490279/18-2, кл. Н 03 К 23/01, 27.05.77) (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор | 1977 |

|

SU690629A1 |

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU951710A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Накапливающий двоичный сумматор | 1981 |

|

SU991611A2 |

| Комбинационный двоичный сумматор | 1979 |

|

SU959281A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU744993A1 |

Авторы

Даты

1982-02-23—Публикация

1978-03-20—Подача