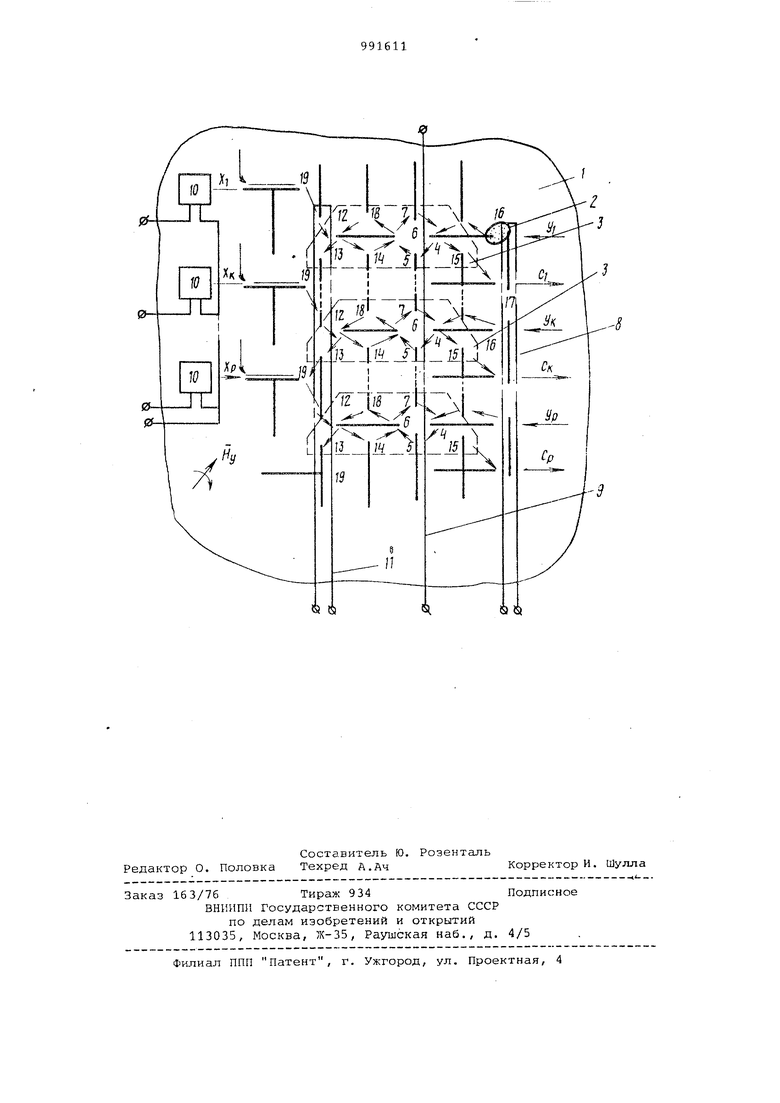

Изобретение относится к вычислительной технике и может быть использовано при построении устройства переработки дискретной информации на цилиндрических магнитных доменах (ЦМД По основному авт. св. № 766017 известен накапливающий двоичный сумматор, содержащий магнитоодноосную пленку с ЦМД, на поверхности которой расположены логические элементы И-ИСКЛЮЧАЮЩЕЕ ИЛИ по числу разрядов операндов, соединенные с Ди намическими ловушками НМД, проводниковый аннигилятор ЦМД, основная токо вая аппликация, магнитосвязанная о логическими элементами И-ИСКЛЮЧАКМЦЕЕ ИЛИ и динамическими ловушками ЦМД всех разрядов сумматора, первый и второй входы каждого логического эле мента И-ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с соответствующими входами cyfiMaTopa первый и второй выход - соответствен но с вторым входом предыдущего логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ и .с входом соответствующей динамичес кой ловушки ЦМД, выход которой соеди иеп с первым входом того же логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ,а третиЯ Еыход каждого логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с соответствующим выходом сумг/iaTopa L.--l- Недостатком известного сумпатора являются ограниченные функциональные возможности, заключающиеся в выполнении то.г1ько операций суммирования и хранения результата. Целью изобретения является расширение функциональных возможностей сумматора путем реализации логических операций. Поставлен,ная цель достигается тем, что накапливающий двоичный сумматор содержит генераторы ЦДЦ по числу разрядов операндов, взаимосвязанные с вторыми входами логических элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ, И дополнительную токовую аппликацию, магнитосвязанную с первыми выходами логических элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ. На чертеже изображена принципиальная схема предложенного сумматора. Накапливающий двоичный сумматор содержит магнитоодноосную пленку 1 с ЦМД 2, на поверхности которой расположены логические элементы И-ИСКЛЮЧАЮЩЕЕ ИЛИ 3 по числу разрядов операндов, соединенные с динамическими лoвyшкa ш 4-7 ЦМД, проводниковый аннигилятор 1лМД 8, основнуЕо токовую аппликацию 9, магнитосвязанную с логическими элементами и дина мическими ловушками ЦМД, генераторы доменов 10, взаимосвязанные с вторыми входами логических элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ, дополнительную токовую аппликацию 11, магиитосвяза кую с перв1:1ми выходами логических элементов М-ИСКЛЮЧЛЮЩЕЕ ИЛИ, входы и У -Ур сумматора (каналы ввода соответствующих разрядов первого и второго операндов ) , выходы сумматора (каналы вывода соот ветствующих разрядов резуль-:5ата сум Цифрами 12-19 обозначе мирования ). зaнимae a e ЦМД при их ны позиции, продвижении в сумматоре. Сумматор работает следующим образом. -Ур сумматора На входы подаются операнды, причем старшие разряды продвигаются по каналам Оба слагаед1ых сводятся разря.и к 1;азряду на расстояние, достаточное для взаиг-юдействия ,., в одно именных разрядах (позиции 12 и 4). В результате в позиции 6 динамически ловушек образуется результат поразрядного суммирования по модулю два, а в позициях 13 и 15 - конъюнкция содержимого одноиг-тенных разрядов, причем в позициях 17 неиспользуемые ЦМД перемосов уничтожаются при возбуждении аннигилятора 8 и не проход на выходы С, Ср суг5матора, а из пози ции 13 1,;Щ licneHocoB К-х разрядов сумматор 1 , 2 ..., р по каналам 13-19 поступают на первые входы (К-1)-х элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ где в течег-пю следующего такта сложе ния )1ствуют с результатом первого поразрядного сум-мирования по модулю два, находящимся в динамических ловумках 4-7, и образуют в ни результат второго ,иpoвaния по мо дулю два, а в позициях 13 и 15 - переносы в более старшие разряды. Процесс суммирования закапчивается в момент времени, когда в выходных каналах 13 - 19 не остается ЦГ-Щ-переносов.---При этом результат сложения хранится в динамических ловушках, откуда он может быть считан из позиции 4 при возбуждении основной токовой аппликации 9. ЦМД результата сложения продвигаются по выходным каналам 4,15, 17 и поступают на выходы Q -Ср сумматора. Процесс образования результата сложения и переноса в старший разряд рассмотрим более подробно на примере сумглирования К-х разрядов операндов В момент времени, когда ЦМД, соот ветствующий К-му разряду первого опе ранда, поступает на первый вход К-го разряда сумматора (позиции 12 ), соответствующий разряду второго операнда, поступает в позицию 4, из которых за счет взаимного отталкивания переходят в выходные каналы 13-19 и 4-15, реализуя тем самым 1 переноса в старший разряд и О в динамической ловушке 6, 7, 4, 5. Если в одном из двух К-ЫХ разрядов операндов ЦМД отсутствует, то присутствующий в К-ом разряде другого операнда ЦМД, не испы -ывая отталкивающего воздействия, из позиции 4 (или 12) через половину такта поступит в позицию б динамической ловушки, реализуя тем 1 п разрядной сумглы по модулю два и О переноса в старший разряд. Случай с двумя нулями в К-ых разрядах операндов тривиален, вследствие чего не рассматривается. Предложенный cyMjviaTop- может работать в режимах как арифметической, так и логической обработки информации . В режиме логической обработки быть ресип-13ованы логические функции II, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИЛИ и НЕ. В ре;киме арифметической обработки NioryT быть выполнены арифметические операции сложение и вычитание. Рассмотрим работу cyMj-.iaTopa в режиме логической обработки информации. Логические операции И и ИСКЛЮЧАЮЩЕЙ ИЛИ выполняются следующим образом. Разряды операндов X и У по канала -1 ввода поступают на вход1-л элементов И-ИСКЛЮЧАЮЦЕЕ ИЛИ в позиции 1.2 и 4 соответственно. Ь результате взаимодействия в элементах И--ИСЮ1ЮЧАЮЩЕЕ ИЛИ через 0,25 такта, считая от момента поступлен) О ;ерандов в позиции 12 и 4, в позициях 13 появляются ЦКД результата выполнения функции И, где они уничтоя аются при токовой аппликации 11, возбуждении и в позициях 15, откуда они либо поступают через 0,75 такта на выходил сумматора (если реализуется функ:1,ия и), либо уничто;::аю7:ся в позици-ях 17 каналов вывода результата (если реализуется функция ИСЮ1ЮЧА10ЩЕЕ ИЛИ ) при возбуждении проводникового аннигилятора 8. Через 0„5 такта в позициях 6 динамических ловушек ЦМД появляется результат выполнения функции ИС1О1ЮЧАЮ ;1ЕЕ ИЛИ, который сохраняется в динамической ловушке и может быть выведен из нее через 1,25 такта в позиции 15 при возбуждении основной токовой аппликации 9, а затем либо поступает через 1,75 такта на выходы cyf-татора (если реализуется функция ИСКЛЮЧАЮЩЕЕ ИЛИ ), либо уничтожается в позициях 17 каналов вывода результата (если реализуется функция И ) при возбуждении проводникового аннигилятора 8, При выполнении функции ИЛИ разряды операндов X и У по каналам ввода одновременно поступают в позиции 12 и 4 на входы элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ. Затем возбуждается дополнительная токовая аппликация 11 и через 0,25 такта, считая от момента поступления опера дов в позиции 12 и 4, разряды опера да X поступают в позиции 14 вторых выходных каналов логических элементов, а через 0,5 такта в позиции 7 динамических ловушек илд, куда поступает также результат выполнения функции ИСКЛЮЧАЮЩЕЕ ИЛИ. Таким обра зом, через О,5 такта в позициях 7 динамических ловуиюк реализуется функция ИЛИ. ЦМД, вышедшие в результате взаимодействия из логических элементов И-ИС1СЛЮЧАЮЩЕЕ ИЛИ по третим выходным каналам, уничтожаются в позициях 17 каналов вывода результата при возбуждении проводни кового аннигилятора 8. Результат функции ИЛИ хранится и может быть выведен через 1,75 такта на выходе сумматора при возбуждении основной токовой аппликации 9. Функция НЕ выполняется в суг-шато ре с использованием генераторов щад При выполнении функции НЕ разряды инвертируемого операнда поступают в позиции 4 на первые входы элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ, причем разряды операнда У поступают в пози ции 4 непосредственно по каналам ввода, а разряды операнда X вначале по каналам ввода поступают в позиции 12, а затем по вторьо,1 выходныгл каналам 12, 14, б, 7 элементов И-ИС КЛЮЧАЮЩЕЕ ИЛИ передаются к позициям 4. Одновременно с поступлением инвертируемого операнда в позиции 4 по каналам ввода 10, 19, 12 в позиции 12 каждого разряда сумматора по тупают щед от генераторов ЦМД 10. В результате взаимодействия в элементах И-ИСКЛЮЧАЮЩЕЕ ИЛИ, через 0,5 так та, считая от момента поступления операнда в позиции 4, в позициях 7 динамических ловушек ЦМД появляется инверсное значение операнда, которое сохраняется в динамических ловушках ЦМД и может быть выведено через 1,7 такта на выходы сумглатора при возбуждении основной токовой аппликации 9. ЦМД, вышедшие в результате взаимодействия в элементы И-ИСКЛЮЧАКЩЕЕ ИЛИ по первым и третьим выходным каналам, уничтожаются при возбуждении соответственно дополнительной токовой аппликации 11 и проводникового аннигилятора 8. Рассмотрим работу суг матора в режиме арифметической обработки информации . При выполнении функции вычитания ЦМД, вычитаемого поступают в позиции 4 и над ними выполняется описанная логи:еская функция НЕ. В первом случае, когда вычитаемым .является операнд У, одновременно с поступлением инверсии вычитаемого в позиции 4, в позиции 12 по каналам ввода поступают разряды уменьшаемого X. Во втором случае, когда вычитаемым является операнд X, одновременно с поступлением инверсии вычитаемого в позиции 7 динa IИчecкиx ловушек ЦМД, в позиции 16 каналов ввода поступает уменьшаемое У, причем, если одноименные разряды уменьшаемого и инверсии вычитаемого представлены ЦМД, то в результате их взаимодействия ЦВД разрядов уменьшаемого поступают в позиции 4 динамических ловушек ЦМД, а ЦМД разрядов инверсии вычитаемого по отводным каналам 7, 18, 12 в позиции 12 на вторые входы элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ. После этого сумматор функционирует также, как и при суммировании операндов, в первом случае с момента поступления уменьшаемого в позиции 12, а во втором - в позиции 4. Отличие заключается в том, что после первого такта сумглирования в позицию 12 шaдшeгo разряда сумматора от генератора ЦМД, взаимосвязанного с вторыг.1 входом элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ младшего разряда сумматора, поступает ЦМД. После окончания процесса вычитания в динамических ловушках ЦМД образуется разность операндов X и У,которая может быть выведена на выходы сумглатора при возбуждении основной токовой аппликации 9. Таким образом, в предложенном сумматоре за счет введения генераторов ЦМД и дополнительной токовой аппликации может быть реализован ряд новых арифметических и логических функций. Формула изобретения Накапливающий двоичный сумматор по авт. св. № 766017, отличающийся тем, что, с целью расширения функциональных возможностей путем реализации логических функций, он содержит генераторы цилиндрических агнитных доменов по числу разрядов перандов, взаимосвязанные с вторыг.от входами логических элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ, и дополнительную оковую аппликацию, магнитосвязанную первыми выходами логических элементов И-ИСКЛЮЧАЮЩЕЕ ИЛИ. Источйики информации, ринятые во внимание при экспертизе 1. Авторское свидетельство СССР № 766017, .кл. Н 03 К 19/00, 1978 (прототип ).

Xj

XK,

XpJ

I

дЩи

3

S Q

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU907810A2 |

| Устройство для обработки информации | 1979 |

|

SU809190A1 |

| Комбинационный двоичный сумматор | 1979 |

|

SU959281A2 |

| Комбинационный двоичный сумматор | 1977 |

|

SU690629A1 |

| Комбинационный двоичный сумматор | 1978 |

|

SU951710A2 |

Авторы

Даты

1983-01-23—Публикация

1981-06-19—Подача