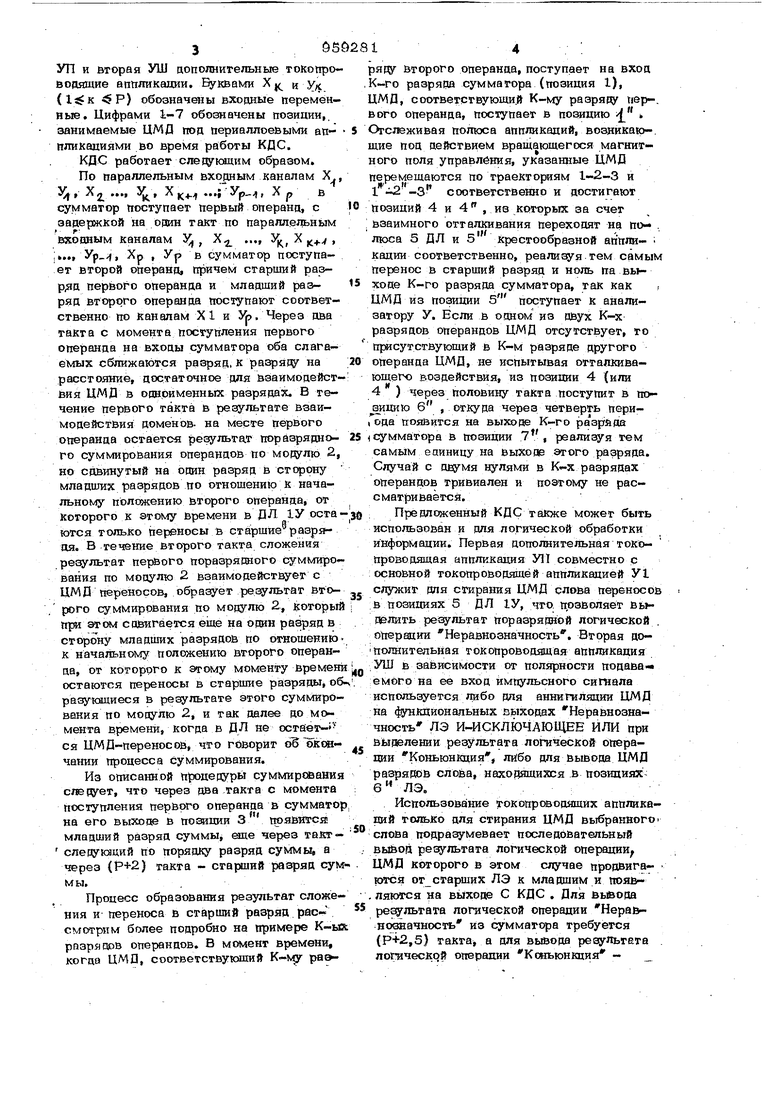

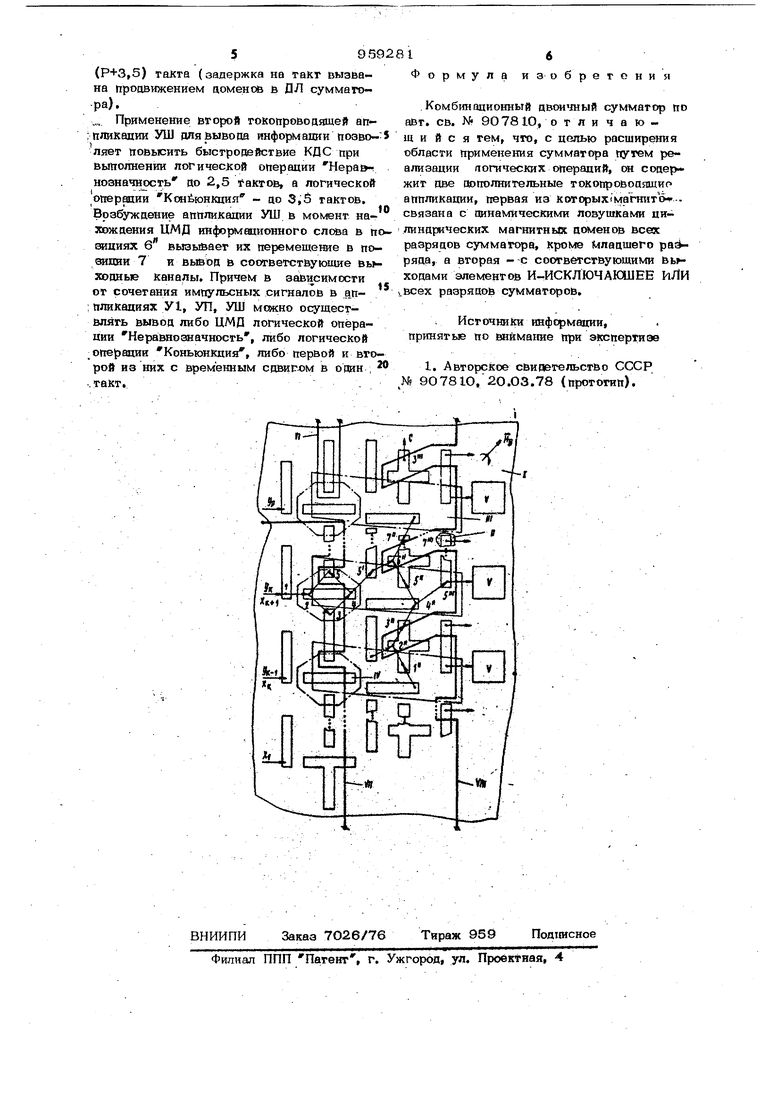

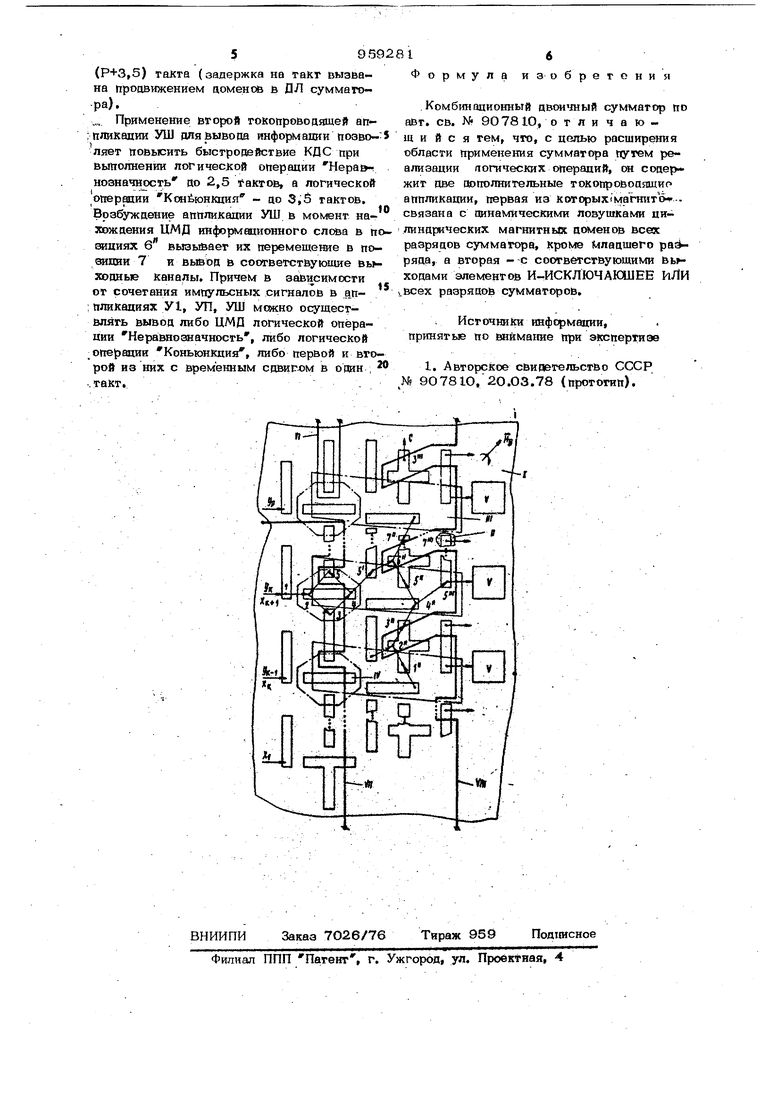

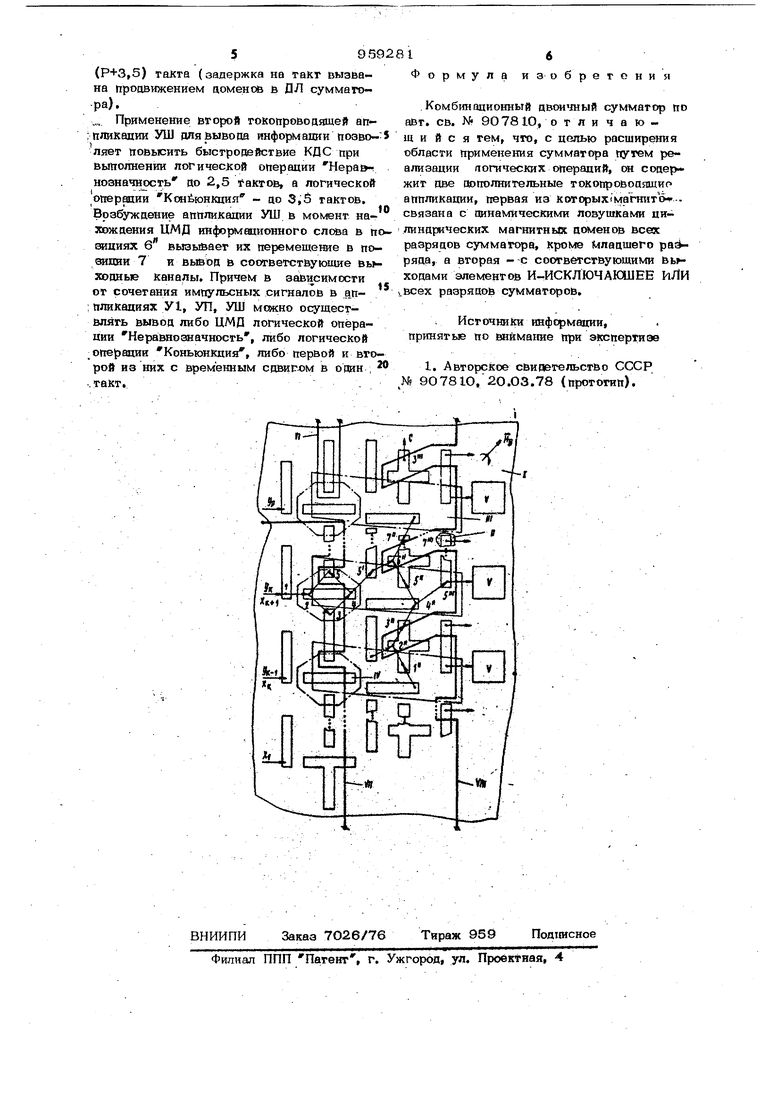

Изобретение относигся к вычислитель- рой тезшиКе и может найти применение при пострдении операционных устройств а базе орноосных материалов с цилиндрическими магеитными доменами (НМД), предназначенных как для арифметической, так и для логической обработки информации. По основному авт. св. М 9О7810 известен Комбинационный двоичный сумматор (КДС), который содержит как и предложенный слой ооноосного материала с ЦМД, на новерзшости которого расположены взаимосвязанные с Р по числу раа рядо операндов логическими элементами (ЛЭ) И-ИСКЛЮЧАЮЦЕЕ ИЛИ динамические лоЕушки (ДЛ) ЦМД и аннигалятррь ЦМД, причем ДЛ младшего разряда сумматора магнитосвязана с основной токопроводящей аппликацией flj. . . . Недостатками такого КДС являются ограниченные фу1В Кциспальные возможноо ти:вспеаствие выполнения только операции суммирования - КДС не в состояний осуществить логическую обработку информации, а также невысокое быстродействие, обусловленное последовательным Вьй водом результатов операций. Целью изобретения является расшире ние области применения известного КДС путем реализации логических операций. Поставленная цель достигается путем того, что №1 содержит две дополнигельные токопровод$вдие аппликации, первая из которых магнитосвязана с.ДЛ ЦМД всех разрядов сумматора, кроме .младшего , разряда, а вторая - с соответствующим выходами элементов И-ИСКЛЮЧАКЩЕЕ; ИЛИ всех разрядов сумматора. На чертеже изображена принципиаль-, ная схема предложенного КДС. КДС соогржит слой одноосного материала 1 с ЦМД П, на поверхности которо- го расположены ЛЭ И-44СКЛЮЧАЩЕЁ : ИЛИ И1, взаимосвязанные с ДЛ ЦМД 1У и аннигиляторами ЦМД У, основная гокопроводящая аппликацияУ1 и первая УП и вторая ЗТи дополнительные г око гфо водящие аппликации. Буквами Xj( и Уд ( Р) обозначены входные переменнью. Цифрами 1-7 обозначены позиции,, занимаемые ЦМД под периаллоевыми аппликациями во время работы КДС. КДС работает еле сеющим образом. По параллельным вхоцным каналам X. y/f Х 2. сумматор поступает первый операнд, с задержкой на один такт по параллельным входным каналам У , :..., Ур, Хр , Ур в сумматор поступает второй операнд, причем старший разр 1д первого операнда и младший разряд BTopisro операнда поступают соответственно по каналам XI и Ур. Через два такта с момента поступления первого операнда на входы сумматора оба слагаемых сближаются разряд, к разряц/ на расстояние, достаточное для взаимодействия ЦМД в одаоименных разрядах. В течение первого такта в ре льтате взаимодействия доменов- на месте первого операнда остается результат пор изряднеего суммирования операндов по мосоглю 2, но сдвинутый на один разряд в сторону млацигах разрядов по отношению к начальному положению второго операнда, от Которого к этому времени в ДЛ 1У оста ются только переносы в старшие разрядя. В течение второго такта сложения ре льтат первого поразрядного суммирования по модулю 2 взаимодействует с ЦМД переносов, обрадует результат второго суммирования по модулю 2, который при этом сдвигается еще на один разряд в сторону младших разрядов по отношению к начальному положению второго операнда, от которого к этому моменту времен остаются переносы в старшие разряды, об разующиеся в результате этого суммирования по модулю 2, и так далее до момента времени, когда в ДЛ не остйег- ся ЦМД-переносов, что говорит dSokceчании процесса суммирования. Из описанной процедуры суммирования , что через два такта с момента поступления первого операнда в суммато на его выходе в позиции 3 появится младший разряд суммы, ете через такт следуюзций по порядку разряд суммы, а через (Р--2) такта - старший разряд сум мы. Процесс образования результат сложения и переноса в старший разряд рассмотрим более подробно на примере К-ы рпзряррв операндов. В момент времени, когда ЦМД, соответствующий K-wpr pa pajsy Второго операнда, поступает на вход К-го разряда сумматора (позиция 1), МД, соответствующей К-му разряду пер-, ого операнда, поступает в позицию j ь тслеживая полюса аппликаций, возникаю-, ие под действием вращающегося магнитного поля управления, указанные ЦМД перемещаются по траекториям 1-2-3 и 1 -з соответственно и достигают позиций 4 и 4 , ив которых за счет взаимного отталкивания переходят на полюса 5 ДЛ и 5 крестообразной аппли- кации соответственно, реали я тем самым перенос в старший разряс1 и ноль па выходе К-го разряда сумматора, так как ЦМД из позкцкк 5 поступает к анализатору У. Если в одном из двух К-х разрядов операндов ЦМД отсутствует, то присутствующий в К-м разряде другого операнда ЦМД, не испытывая отталкивающего воздействия, из позиции 4 (или 4 ) через половину такта поступит в ш дицию б , откуда через четверть периода появится на выходе К-го разргйда сумматора в позиции , реализуя тем самым еаиницу на выходе этого разряда, Случай с двумя нулями в разрядах операндов тривиален и поэтому не рассмат зивается. ; Преилсженный КДС также может быть использован и для логической обработки информации. Первая пополнительная токопроводящая аппликация УП совместно с основной токопроводящёи аппликацией У1 служит для стира гая ЦМД слова переносов в позициях 5 ДЛ 1У, что. позволяет вь яелить ре льтат поразрядной Логической . операции Неравнозначность. Вторая дополнительная токопроводящая аппликация :УШ в зависимости от полярности подава-. емого на ее вход импульсного сигнала используется либо для аннигиляции ЦМД на функциональных выходах Неравнозначность ЛЭ И-ИСКЛЮЧАЮЩЕЕ ИЛИ при выделении результата логической операии Конъюнкция, либо для Вывода ЦМД разрядов слова, находящизося .в позицияхб ЛЭ„ Использование токопроводящих аппликаций только для стирания ЦМД выбранного слова подразумевает последовательный вь&од ре льтата логической операции ЦМД которого в этом случае продвига- ются от старших ЛЭ к младшим и поя ляются на выходе С КДС . Для вьйода результата логической операции Нера&ноааачность из сумматора требуется (,S,) такта, а для вывода рееультЕта логической операции Котьюнкция - (P+3,5) такта (задержка на такт вызвана процвижением цоменсй в ДЛ сумматора), ,„. Применение второй токопроводяшей ап; пликадии УШ ддя|зывоца информации позволяет повысить быстродействие КДС при выполнении лоГичесхой операции Нера&г нозначн сть до 2,5 тактов, а логической оперший Ксибюнкция - до 3,5 тактов. Возбуждение аппликации УШ в момент нахождения ЦМД информационного спо&а в п зициях б вызывает их перемещение в позиции 7 и вывод в соответствующие BI ходные каналы. Причем в зависимости от сочетания импульсных сигналов в ап; пликациях У1, УП, УШ мсмсно осуществлять вывод либо ЦМД логической операции Неравнозначность, либо логической операции Коньюнкция, либо первой и вто рой из них с временным сдвирлм в один .такт. - . Формула изобретения Комбинадионный двоичный сумматор по авт. св. № 90 7810, о т л и ч а ю щ и и с я тем, что, с целью расширения области применения сумматора путем реализации логических операций, он содержит две Дополнительные токопроводяшиг аппликации, первая из которыхмагнитол... связана с динамическими ловушками цилиндрических магнитных доменов всея: разрядов сумматора, кроме Младшего pasiряда, а вторая - с соответствующими BfcFходами элементов И-ИСКЛЮЧАЮШЕЕ ИЛИ всех разрядов сумматоров. Источники информации, принятые по BHHMaime при экспертизе I. Авторское свидетельство СССР 9О781О, 2О.О3.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор | 1978 |

|

SU797077A1 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Многоразрядный двоичный комбинационный сумматор | 1978 |

|

SU764136A1 |

| Комбинационный двоичный сумматор | 1978 |

|

SU744993A1 |

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Накапливающий двоичный сумматор | 1981 |

|

SU991611A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU907810A2 |

Авторы

Даты

1982-09-15—Публикация

1979-03-29—Подача