(54) КОМБИНАЦИОННЫЙ ДВОИЧНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор | 1978 |

|

SU907810A2 |

| Комбинационный двоичный сумматор | 1977 |

|

SU690629A1 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU797077A1 |

| Многоразрядный двоичный комбинационный сумматор | 1978 |

|

SU764136A1 |

| Комбинационный двоичный сумматор | 1979 |

|

SU959281A2 |

Изобретение относится к вычиспитепь ной технике и может быть использовано при построении устройств переработки дискретной информации на ципиндрических .магнитных доменах (ЦМД). По основному авт. св. № 690629 из вестен комбинационный двоичный сумматор, который содержит в каждом разряде логический элемент И-ИСКЛЮЧАЮЩЕЕ ИЛИ, динамическую повушку и аннигилятор ЦМД, выполненные из пермаллоевых аппликаций и расположенные на поверхности магнитоодноосной пленки с ЦМД, причем первый вход каждого пошческого элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме первого, соединен с первым выходом предыдущего логического И-ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые вход и выход каждого логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом и входом соответствующей динамической ловушки, а третий выход каждого логического элемента И-ИСКЛЮЧА- ЮЩЕЕ ИЛИ соединен с аннигилятором ЦМД 1. Недостатком известного сумматора является сравнительно низкое быстродействие при сложении массивов чисел вследствие непроизводительных затрат времени на ввод результата предыдущего суммирования в сумматор, которое при сложении УY и-разрядных чисел в лучшем случае составляет ГУ1(и + 5) тактов (такт - время, необходимое для одного оборота вектора Н вращающегося в ппоскости доменосодержащего слоя магнитного попя), а также ограниченные функциональные возможности из-за отсутствия запоминающих элементов для хранения результата операции. Цель изобретения - повьгщение быстродействия комбинационного двоичного сумматора. Поставленная цель достигается тем, что комбинационный двоичный сумматор содержит компрессор и депитёпь ЦМД,

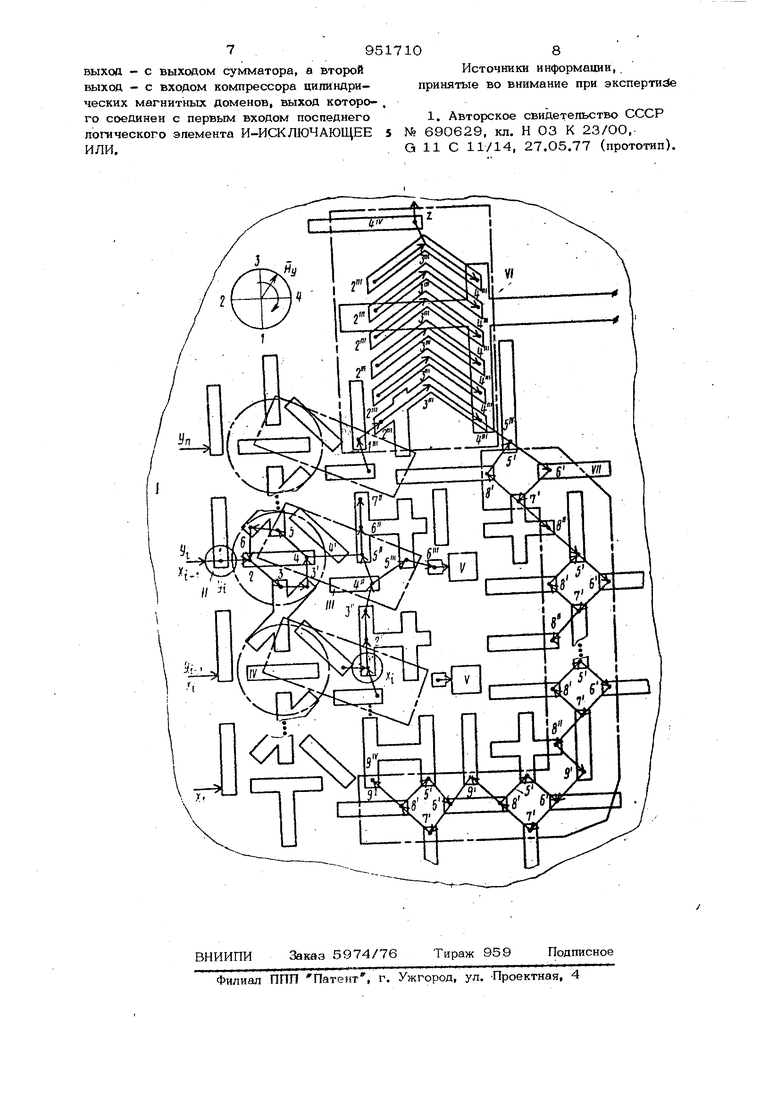

вход которого соединен с первым выхо-По параппепьным входным каналам дом первого аогического эпемента И-ИС- 1 i ,X,i... ; :, Х ,-....,Х„в суммаКЛЮЧАЮ1ДЕЕ ИЛИ, первый выход - с вы-тор поступает первый операнд, с задержходом сумматора, а второй выход - с вхо-кой на один такт по паралпепьным входдом компрессора ЦМД, выход которого sным каналам i ar---J |---;Уц., Х„; соединен с первым входом последнего по-vj, в сумматор поступает второй опегического элемента И-ИСКЛЮЧАЮЩЕЕранд, причем старший разряд nejJBoro опеИЛИ,ранда и младший разряд второго операнда

На чертеже изображена принципиапь-поступают соответственно по каналам X,f

ная схема сумматора.10и у,. Через два такта с момента поступПреДложенный сумматор содержит маг-пения первого операнда на входы сумма нитоодноосную пленку 1 с ЦМД И на по-тора оба слагаемых сводятся разряд к

верхности которой расположены погичес-разряду на расстояние, достаточное для

кие элементы И-ИСКЛЮЧАЮЩЕЕ ИЛИ )11взаимодействия ЦМД в одноименных разс двумя входами и тремя выходами, дина-15рядах.

мические повушки IV аннигиляторы ЦМДV,.В течение первого такта (в результаделитель ЦМД VI и компрес сор ЦМД VII.те взаимодействия доменов) на месте пер-Цифрами 1, 2, 3, 3 i 4, 4 обозначенвого операнда остается результат пораз- .

канал ввода i -го разряда второго one-рядного суммирования операндов ,

ранда и { -1 + 1 )-го разряда первого one- 20но сдвинутый на один разряд в сторону

ранда в 1 -й разряд сумматора. Цифрамимладших разрядов по отношению к начашь1,2,3,4 обозначены канал вводаному положению второго операнда, от ко1-го разряда первого операнда и каналторого к этому времени в динамических

вывода результата поразрядного суммиро-ловушках IV остаются только переносы

вания по vwod 2 с предыдущего (l-l)-ro 25в старшие разряды.i

разряда сумматора. Цифрами 2,3,3,

4, 5, 6 обозначена динамическая повуш-В течение второго такта сложения река tV. Цифрами 5, б, 7 обозначен ка-зультат первого поразрядного суммированал вывода результата поразрядного сум-ния по И1Ос|2 взаимодействует с ЦМД-пемирования по 1-го-разряда сумма- JQреносом на выходах динамических повутора Цифрами 5, б обозначен каналшек, образует результат второго суммировывода пишних доменов в аннигиляторвания noK«od2, который при этом сдвигаЦМД V. На первом выходе логическогоется еще на один разряд в сторону младэпемента позиции 5 реализуется функ-ших разрядов по отношению к начальному ция Неравнозначность, а на втором иположению второго операнда, от которотретбем в познпиях 5 и соответствен-го к этому моменту времени остаются пено - функция И. Позиция l 5голяетсяренрсы в старшие -разряды, образующиеся функциональным выходом Неравнознач-в результате этого суммирования по кость младшего логического.элемента И-wo62, и так далее до момента времени, ИСКЛЮЧАЮЩЕЕ ИЛИ и входом делителя когда в динамических ловушках не остадоменов V Цифрами обозна-нется ЦМД-переносов, что говорит об чен путь растянутого магнитного до-окончании процесса сложения, глена (РМД) в делителе ЦМД. Позиции

4 и 5 являются выходами делителя до-Таким образом, через два такта с моменов, причем позиция 4 соединена со мента поступления первого операнда в входом Z регистра суммы, а позиция 5 сумматор на его выходе в позиции 1 появляется входом компрессора VI/, состоя-является младший разряд суммы, еще чещего из взаимосвязанных динамическихрез такт - следующий по порядку разряд повушек, обозначенных цифрами 5 -б-суммы, а через (И+2) такта - старший . Цифрами а и 9 обозначены по-разряд суммы. По мере появления резульзиции соединения выхода каждой из преды- тат сложения начиная с младшего разрядущих динамических повушек с входом по-Да поступает в делитель VI способный раследующей, причем выход последней дина-ботать в следующих четырех режимах: мической повушки (позиция 9) соединенкак элемент задержки на такт (режим нас входом старшего .логического элементакопления результата), как аннигилятор И-ИСКЛЮЧАЮЩЕЕ ИЛИ. (режим стирания результата), как делиКомбинационный двоичный сумматортата) и как делитель-аннигилятор (режим

работает следующим образом.вывода результата). тель (режим накопления - вывода резульПри работе депитепя в первом режиме разряд суммы, поступивший на его вход, через такт появляется на входе компрессора (позиция 5 ) и одновременно на вы ходе компрессора (позиция э), При работе во втором режиме разряд суммы уничтожается в позициях 4 депитепя-аннигипятора, охваченных проводниковой петлей. При работе в третьем режиме разряд суммы дублируется в позициях З , причем дубль выводится в регистр суммы (позиция 4 ), а оригинал через такт с момента поступления в делитель появляртся на выходе компрессора в позиции 9 аналогично первому из рассматриваемых :;лучаев, В четвертом режиме работы делитель дублирует разряд суммы в позициях З и уничтожает оригинал в позициях 4 в результате чего производится вывод содержимого разряда в регистр суммы и очишенйе соответствующего разряда от хранимой в нем информации. Если делитель VI работает в режиме накопления или накопления - вывода результата, то разряды суммы по мере их поступления в поизицию l с задержкой на такт вновь вводятся в сумматор по первому входу старшего логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ, в результате чего через (и+1) тактов после начала процесса суммирования (или через такт после окончания процесса суммиро. вания) операнд суммы складывается с поступившим к этому времени по параллельным входным каналам ( Д , Х.;...; и очередным числом массива. Процесс образования результата споже кия и переноса в старший разряд (на при- мере 1 -X разрядов операндов), состоит в следующем. В момент времени, когда 11МД, соответствующий 1 -у разряду второго операн да, поступает на вход 1 -го разряда сумматора (позиция 1), ЦМД, соответствующий Л -му разряду первого операнда, поступает в поизицию l на Н-аппликации. Отслеживая полюса аппликаций, возникающие под действием вращающегося магнитного поля управления, вышеупомянутые перемещаются по траекториям и 1 , соответственно и стигают позиций 4 и 4 , из которых переходят счет взаимного отталкивания на полюса 5 динамической ловущки и 5 Н-аппликаИии соответственно, реализуя тем самым перенос в старший разряд и ноль на выходе i -гр разряда сумматора. 1-2до- за так как ЦМД из позиции 5 поступает к аннигилятору доменов V. Есш в одном из двух -X разрядов операндов 1МД отсутствует, то присутствующий в -f -ом разряде Другого операнда ЦМД, не испытывая поздействия, из позиции 4 (ига 4 ) через четверть такта поступает в позицию 5 , откуда через поповину периода появляется на выходе 1 -го разряда сумматора в позиции , реализуя тем самым единицу на выходе этого разряда. Случай с двумя нулями в 1-х разрядах операндов тривиален и поэтому не рассматривается. Младший разряд суммы двух первых операндов появляется на выходе сумматора в позиции l через два такта с момента поступления первого операнда на его входы, процесс суммирования занимает М тактов, каждое последующее суммирование предыдущего- результата с оче редньш оператором составляет (И) тактов. Таким образсял, для сложения массива из к и -разрядных чисел потребуется (jY)(VTl )+1 3 тактов, что превосходит по- т(и+5) добный показатель прототипа в Й1( Предложенный сумматор может рабо«тать в следующих режимах; комбинационный сумматор (делитель ЦМД функционирует в режиме вывода результата) с быстродействием, равным быстродействию прототипа; как накапливающий сумматор (делитель ЦМД функционирует в режиме элемента задержки), причем при сложении двух чисел его быстродействие аналогично быстродействию прототипа, при сложении массива чисел (значительно превос . ходит быстродействие прототипа); накапливающий сумматор, выводящий все промежуточные суммы, получающиеся при поэлементном cлJэжeнии массива чисел (делитель ЦМД функционирует в режиме накопления - вывода результата), с быстродействием, аналогичным предыдущему режиму работы. Формула изобретения. Комбинационный двоичный сумматор по авт. св. № 69О629, отличающийс я тем, что, с целью повышения быстродействия сумматора, он содержит компрессор и делитель цилиндрических магнитных доменов, вход которого соединен с первым выходом первого логического элемента И-ИСКЛЮЧАЮЩЕЕ ИЛИ, первый

Авторы

Даты

1982-08-15—Публикация

1978-06-12—Подача