(S) УСТРОЙСТВО ОПРОСА ИНФОРМАЦИОННЫХ

i

Изобретение относится к телемеханике и предназначено для использования в информационно-измерительных системах, в частности в устройствах для программного опроса информаци- . онных каналов с автоматическим выбором порядка опроса.

Известны устройства опроса, содержащие счетчик, выходы которого соединены со входами регистра и через запоминающий блок - со входами блока анализа и блока управления, второй вход которого подключен ко входной шине, а остальные - к выходам регистров фаз и первым входам мультиплексора, при этом первые выходы блока управления соединены с первыми входами фаз, а вторые - со вторыми входами мультиплексора, выходы которого подключены ко вторым входам регистров фаз и вторым входам, блока анализа ,третьи входы которого соединены с выходами счетчика позиций ,кроме того выходы блока анализа подключены КАНАЛОВ

КО входу регистра команд, причем выходы счетчика, счетчика позиций и третьи выходы регистров фаз-соединены с тактовой шиной l и 2.

В известных устройствах каждой из возможных частот опроса соответствует регистр фазы, причем его содержимое указывает последнюю занятую фазу данной частоты опроса. Закрепленная за каналом фаза считывается с помощью мультиплексора и поступает в блок анализа, где происходит ее сравнение с кодом текущей фазь и в случае равенства выдается сигнал на запись номера соответствующего канала в регистр команд.

Недостатками известных устройств являются ограниченные возможности контроля работоспособности их основных элементов и низкая надежность.

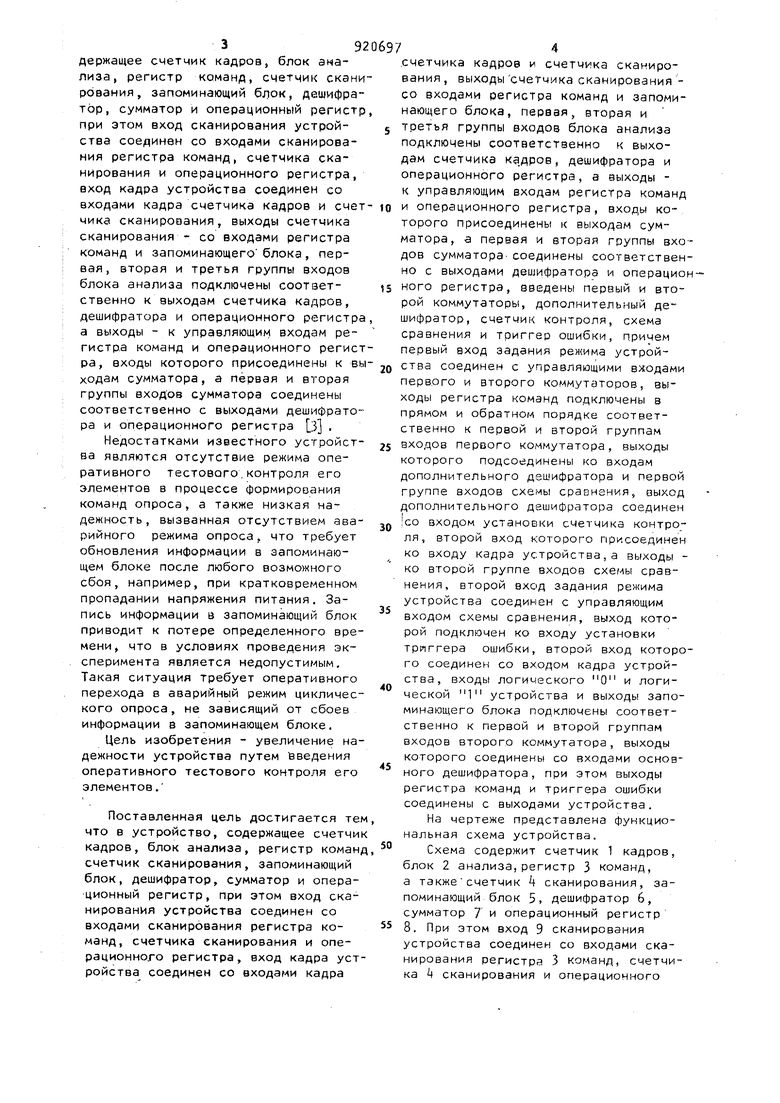

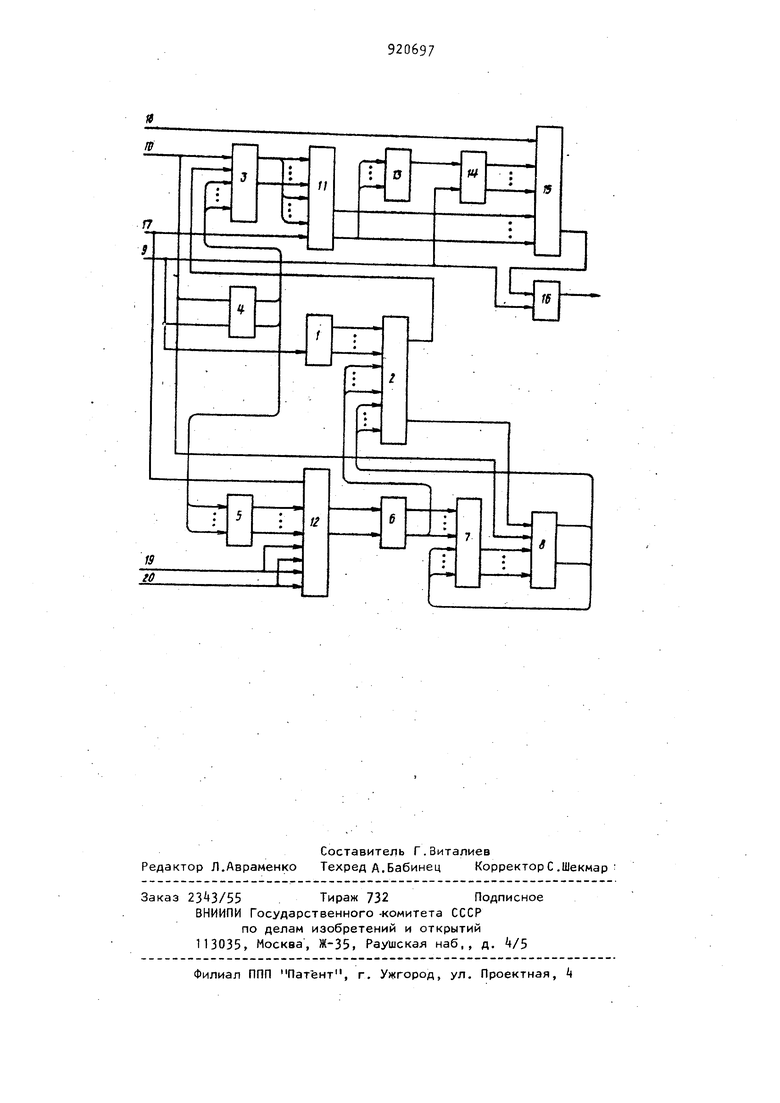

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство опроса информационных каналов, со392держащее счетчик кадров, блок анализа, регистр команд, счетчик скани рования, запоминающий блок, дешифратор, сумматор и операционный регистр при этом вход сканирования устройства соединен со входами сканирования регистра команд, счетчика сканирования и операционного регистра, вход кадра устройства соединен со входами кадра счетчика кадров и счет чика сканирования, выходы счетчика сканирования - со входами регистра команд и запоминающегоблока, первая, вторая и третья группы входов блока анализа подключены соотаетственно к выходам счетчика кадров, дешифратора и операционного регистра а выходы - к управляющим входам регистра команд и операционного регист ра, входы которого присоединены к вы ходам сумматора, а первая и вторая группы входов сумматора соединены соответственно с выходами дешифратора и операционного регистра З . Недостатками известного устройства являются отсутствие режима оперативного тестового.контроля его элементов в процессе формирования команд опроса, а также низкая надежность, вызванная отсутствием аварийного режима опроса, что требует обновления информации а запоминающем блоке после любого возможного сбоя, например, при кратковременном пропадании напряжения питания. Запись информации в запоминающий блок приводит к потере определенного времени, что в условиях проведения эксперимента является недопустимым. Такая ситуация требует оперативного перехода в аварийный режим цикличес кого опроса, не зависящий от сбоев информации в запоминающем блоке. Цель изобретения - увеличение на дежности устройства путем введения оперативного тестового контроля его элементов. Поставленная цель достигается те что в устройство, содержащее счетчи кадров, блок анализа, регистр коман счетчик сканирования, запоминающий блок, дешифратор, сумматор и операционный регистр, при этом вход сканирования устройства соединен со входами сканирования регистра команд, счетчика сканирования и операционного регистра, вход кадра уст ройства соединен со входами кадра счетчика кадров и счетчика сканирования , выходы счетчика сканирования со входами регистра команд и запоминающего блока, первая, вторая и третья группы входов блока анализа подключены соответственно к выходам счетчика кадров, дешифратора и операционного регистра, а выходы к управляющим входам регистра команд и операционного регистра, входы которого присоединены к выходам сумматора, а первая и вторая группы входов сумматорасоединены соответственно с выходами дешифратора и операционного регистра, введены первый и второй коммутаторы, дополнительный дешифратор, счетчик контроля, схема сравнения и триггер ошибки, причем первый вход задания устройства соединен с управляющими входами первого и второго коммутаторов, выходы регистра команд подключены в прямом и обратном порядке соответственно к первой и второй группам аходов первого коммутатора, выходы которого подсоединены ко входам дополнительного дешифратора и первой группе входов схемы сравнения, выход дополнительного дешифратора соединен |со входом установки счетчика контроля, второй вход которого присоединен ко входу кадра устройства,а выходы ко второй группе входов схемы сравнения, второй вход задания режима устройства соединен с управляющим входом схемы сравнения, выход которой подключен ко входу установки триггера ошибки, второй вход которого соединен со входом кадра устройства, входы логического О и логической 1 устройства и выходы запоминающего блока подключены соответственно к первой и второй группам входов второго коммутатора, выходы которого соединены со входами основного дешифратора, при этом выходы регистра команд и триггера ошибки соединены с выходами устройства. На чертеже представлена функциональная схема устройства. Схема содержит счетчик 1 кадров, блок 2 анализа,регистр 3 команд, а такжесчетчик k сканирования, запоминающий блок 5, дешифратор 6, сумматор 7 и операционный регистр 8. При этом вход 9 сканирования устройства соединен со входами сканирования регистра 3 команд, счетчика 4 сканирования и операционного регистра 8, Вход 10 кадра устройства соединен со входами кадра счетчика 1 кадра и счетчика сканирования, а выходы счетчика - со входами регистра 3 команд и запоминающего блока 5. Первая, вторая и третья группы входов блока 2 анализа подключены соответственно к выходам счетчика 1 кадров, дешифратора 6 и операционного регистра 8, а выходы к управляющим входам регистра 3 команд и операционного регистра 8. Входы регистра 3 присоединены к выходам сумматора 7. а первая и вторая группы входов сумматора 7 соединены соответственно с выходами дешифратора 6 и операционного регистра 8, Кроме этого, устройство содержит первый коммутатор 11, второй коммутатор 12., дополнительный дешифратор 13, счетчик 14 контроля, схему 15 сравнения и триггер 16 ошибки. Первый вход 17 задания режима устройства соединен с управляющими входами коммутатора 11 и коммутатора 12, Выходы регистра 3 команд подключены в прямом и обратном поряд ке соответственно к первой и второй группам входов первого коммутатора. выходы которого подсоединены ко вхо- зо док дам дешифратора 13 и первой группе входов схемы 15 сравнения. Выход дешифратора 13 соединен со входом установки счетчика 1 контроля, второй вход которого присоединен ко входу 10 кадра устройства, а выходы - ко второй группе входов схемы 15- Второй вход 18 задания режим устройства соединен с управляющим входом схемы 15, выход которой под ключен ко входу установки триггера 16 ошибки, второй вход которого сое динен со входом 10 устройства. Выхо 19 логического О и вход 20 логической 1 устройства и выходы запоминающего блока 5 подключены соответственно к первой и второй груп пам входов второго коммутатора, выходы которого соединены со входами дешифратора 6. При этом выходы реги ра 3 команд и триггера 16 соединены выходами устройства. Устройство работает следующим об разом . Подачей потенциального сигнала высокого уровня на первый вход зада ния режима 17 задается режим циклического опроса, который характеризуется тем, что всем измерительным 76 каналам задается одна и та же частота опроса - , где J,,- информативность , а N- общее число распределяемых каналов. При этом нет ° необходимости вводить в запоминающий блок 5 коды частот опроса, так как они одинаковы для всех каналов. С целью оперативного перевода устройства в указанный режим работы при сбое информации в запоминающем блоке достаточно обеспечить поступление на входы дешифратора 6 постоянного кода частоты в течение всего цикла распределения фаз. Это достигается с помощью второго коммутатора 12, который посигналу управления на входе 17 отключает выходы запоминающего блока 5 от входов дешифратора 6 и переключает последние на другое направление коммутации с постоянной кодовой комбинацией. Цикл операций, выполняемых устройством на очередной позиции кадра для определения номера опрашиваемого канала в описываемом режиме, аналогичен циклу, выполняемому известным устройством. Однако, хотя частоты следования команд опроса в общей последовательности одинаковы, поряследования команд отличается от циклического тем, что код номера канала 6, бг.--- 6 является зеркальным отражением кода номера канала в циклической последовательности. Поэтому при циклическом опросе первый коммутатор 11 переключается на другое направление, на входы которого разряды регистра 3 команд заведены в обратном порядке б, 6 пп-f, . SZiO- Контрольная (эталонная) циклическая последовательность команд формируется счетчиком 1 контроля,, который считает тактовые импульсы на входе 10. Начало формирования контрольной последовательности определяется сигналом установки в нулевое состояние счетчика Ц, который выдается дополнительным дешифратором 13 при поступлении на его входы кодовой комбинации, соответствующей номеру последнего канала. Таким образом достигается совпадение точек канала отсчета контрольной и проверяемой последовательностей команд. Номера каналов, входящие в состав обеих последовательностей, поочередно сравниваются схемой 15 при наличии потенциального сигнала высокого уровня на входе 18, В случае несовпадения схема 15 формирует сигнал ошибки, указывающий на сбой в работе устройства, который запоминается в триггере 1б по тактовому импульсу на входе 10, Таким образом, режим оперативного тестового контроля определяется пода чей сигнала высокого уровня одновременно на первый вход 17 и второй вход 18 задания режима, а режим циклического опроса - подачей сигнала высокого уровня только на первый вход 17. Данное устройство по сравнению с известным имеет расширенные возможности контроля, что обеспечено наличием режима оперативного тестового контроля. При этом основные элементы устройства проверяются с необходимой полнотой в режиме динамического фун ционирования. Дополнительным преимуществом устройства является повышение надежности за счет введения режима циклического опроса, в который устройство переводится при сбое информации в запоминающем блоке. Формула изобретения Устройство опроса информационных каналов, содержащее сметчик кадров, блок анализа, регистр команд.счетчик сканирования, запоминающий блок, дешифратор, сумматор, операционный регистр, при этом вход сканирования устройства соединен со входами сканирования регистра команд, счетчика сканирования и операционного регистра, вход кадра устройства соединен со входами кадра счетчика кадров и счетчика сканирования, выходы счетчика сканирования - со входами регистра команд и запоминающего блока, первая, вторая и третья группы входов блока анализа подключены соот ветственно к выходам счетчика кадров дешифратора и операционного регистра а выходы - к управляющим входам регистра команд и операционного регистра, входы которого присоединены к выходам сумматора, а первая и вторая группы входов сумматора соединен 78 соответственно с выходами дешифратора и операционного регистра, о тличающееся тем, что, с целью увеличения надежности устройства, оно содержит первый и второй коммутаторы, дополнительный дешифратор, счетчик контроля, схему сравнения и триггер ошибки, причем первый вход задания режима устройства соединен с управляющими входами первого и второго коммутаторов, выходы регистра команд подключены в прямом и обратном порядке соответственно к первой и второй группам входов первого коммутатора, выходы которого подсоединены ко входам дополнительного дешифратора и первой группе входов схемы сравнения, выход дополнительного дешифратора соединен со входом установки счетчика контроля, второй вход которого присоединен ко входу кадра устройства, а выходы ко второй группе входов схемы сравнения, второй вход задания режима устройства соединен с управляющим входом схемы сравнения, выход которой подключен ко входу установки триггера ошибки, второй вход которого соединен со входом кадра устройства, входы логиче.ского О и логической 1 устройства и выходы запоминающего блока подключены соответственно к первой и второй группам входов второго коммутатора, выходы которого соединены со входами основного дешифратора, при этом выходы регистра команд и триггера ошибки соединены с выходами устройства. Источники информации., принятые во внимание при экспертизе 1. Авторское свидетельство СССР 278759, кл. Н 03 К 17/00, 1970. 2. Авторское свидетельство СССР № 612406, кл. Н 03 К 17/02, 1Э78. 3. Авторское свидетельство СССР по заявке W 2567535/18-21, кл. Н 03 К 17/02, решение от 23.05.78 (прототип).

//

J7 3

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство опроса информационных каналов | 1980 |

|

SU911727A2 |

| Устройство опроса информационных каналов | 1978 |

|

SU720720A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Вычислительное устройство для контроля параметров объекта | 1975 |

|

SU690498A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство опроса телеметрических каналов | 1978 |

|

SU705678A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 2001 |

|

RU2216760C2 |

IS го

Авторы

Даты

1982-04-15—Публикация

1980-06-30—Подача