8

(Л СП 00

по модулю п. Устройство также содержит накапливающий сумматор 2,схему 3 сравнения, дешифратор 4 кодов команд, элементы И 8 и 9, элементы ИЛИ 10 и 11, триггер 12 и блок 13 фиксации ошибки. Сущность изобретения состоит в расширении функциональных возможностей устройства за счет обеспечения контроля переходов к последующим каналам от команд всех типов и сокращении аппаратурных затрат за счет организации контроля адресов по модулю, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для контроля условных переходов микропроцессора | 1984 |

|

SU1238076A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| Устройство для контроля последовательности микрокоманд | 1983 |

|

SU1087999A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем и микроЭВМ. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля переходов от команд всех типов и сокращение аппаратурных затрат. Поставленная цель достигается путем введения в устройство первой 5, второй б, третьей 7 схем свертки

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем и микроЭВМ.

Известен микропрограммный процессор, содержащий операционный блок, блок памяти микрокоманд, регистр микрокоманд, регистр адреса, регистр кода операций, первый и второй узлы ветвления, блок сопряжения с ОЗУ, сумматор приращений, счетчик микрокоманд, дешифратор, узел проверки нуля, узел проверки единицы, первый-четырнадцатый элементы И, пер- вый-третий триггеры, первый-седьмой элементы ИЛИ., первый-четвертый элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

Недостатками данного устройства являются узкие функциональные возможности и большие аппаратурные затраты.

Известен также микропрограммный процессоре контролем, содержащий операционный блок, блок памяти микрокоманд, регистр микрокоманд, два регистра адреса, регистр кода операций, блок сравнения, триггер фиксации сбоя, двенадцать элементов И, пять элементов ИЛИ, два элемента НЕ, элемент задержки, триггер признака, сумматор по модулю 2,

Недостатками данного устройства также являются узкие функциональные возможности и большие аппаратурные затраты.

Наиболее близким из известных устройств к предлагаемому изобретению по технической сущности и достигаемому положительному эффекту является устройство для контроля микропроцессорной системы, которое содержит первый-третий регистры операндов, первый и второй буферные регистры адреса, первый-третий блоки сравнения, счетчик команд, первый и второй сумматоры, формирователь сигналов опроса, коммутатор, первый и второй триггеры управления, триггер отказа, формирователь константы, первый-шестой элементы И, дешифратор кода операции, первый-четвертый элементы ИЛИ. Единичный выход первого триггера управления соединен с первым входом первого элемента И, выход

первого элемента ИЛИ соединен с первым входом второго элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ. Первые входы с первого по третий блоков сравнения и информационные входы первого и второго буферных регистров адреса подключены к входу адреса устройства для подключения к адресному входу контролируемой микро0 процессорной системы.

Информационные входы с первого по третий буферных регистров операндов подключены к входу данных устройства для подключения к информационному выходу

5 контролируемой микропроцессорной системы. Первые входы третьего и четвертого элементов И, входы синхронизации второго буферного регистра адреса и первого триггера управления и первый синхровход фор0 мирователя сигналов опроса подключены к входу управления устройства для подключения к выходу синхронизации контролируемой микропроцессорной системы. Вторые входы первого и третьего элементов И и ин5 версный вход четвертого элемента И подключены к входу управления устройства для подключения к выходу состояния контролируемой микропроцессорной системы. Входы синхронизации с первого по третий

0 буферных регистров операндов и первый разрешающий вход формирователя сигналов опроса подключены к входу управления устройства для подключения к выходу разрешения ввода контролируемой микропро5 цессорной системы. Разрешающий вход первого буферного регистра операндов, второй вход второго элемента И и второй разрешающий вход формирователя сигналов опроса подключены к входу управления

0 устройства для подключения к выходу реализации цикла чтения кода команды контролируемой микропроцессорной системы.

Тактовый вход устройства подключен к второму входу четвертого элемента И, к

5 третьему входу третьего элемента И, к второму синхровходу формирователя сигналов опроса и входу синхронизации триггера отказа. Выход первого буферного регистра

операндов соединен с входом дешифратора кода операции, выходы которого соединены с входами первого элемента ИЛИ, выход которого соединен с S-входом второго триггера управления и разрешающим входом второго буферного регистра адреса. Выход последнего соединен с первым входом первого сумматора, второй вход которого соединен с входом формирователя константы, соединенного информационным входом с выходом второго триггера управления. Разрешающий вход формирователя константы подключен к входной шине единичного потенциала устройства, а выход первого сумматора соединен с вторым входом второго блока сравнения, выход которого соединен с первым информационным входом коммутатора.

Выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен со счетным входом счетчика команд, с прямым входом пятого элемента И и R-входом второго триггера управления. Выход четвертого элемента И соединен с вторым входом третьего элемента ИЛИ, вторым входом второго элемента ИЛИ и первым входом шестого элемента И, выход которого соединен с первым информационным входом формирователя сигналов опроса, Выход счетчика команд соединен с инверсным входом пятого элемента И и первым входом второго суммато ра, второй вход которого соединен с выходом первого буферного регистра адреса, вход синхронизации которого соединен с выходом пятого элемента И. Выход второго элемента И соединен с D-входом первого триггера управления, выход которого соединен с первым управляющим входом коммутатора и вторым входом шестого элемента И, выход которого соединен с вторым информационным входом формирователя сигналов опроса и первым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса счетчика команд.

Первый-пятый выходы опроса формирователя сигналов опроса соединены соответственно с вторым управляющим входом коммутатора, третьим управляющим входом коммутатора, разрешающим входом второго буферного регистра операндов, разрешающим входом третьего буферного регистра операндов и вторым входом четвертого элемента ИЛИ, Выходы второго и третьего буферных регистров операндов соединены с вторым входом первого блока сравнения, выход которого соединен с вторым информационным входом коммутатора. Выход второго сумматора соединен с вторым входом третьего блока сравнения,

выход которого соединен с третьим информационным входом коммутатора. Его выход соединен с D-входом триггера отказа, выход которого является выходом отказа устройст- 5 ва, а выход второго элемента ИЛИ соединен с четвертым управляющим входом коммутатора.

Недостатками данного устройства являются узкие функциональные возможности,

0 так как в нем не обеспечивается контроль правильности выполнения таких команд условных переходов, для выполнения которых .требуется неизменное число тактов, не зависящее от значения проверяемого условия

5 (команд типа JXX), контроль правильности выполнения команд безусловных переходов (JMP, CALL) и команды вызова подпрограммы (RSTN), большие аппаратурные затраты.

0Целью изобретения является расширение функциональных возможностей путем обеспечения контроля переходов от команд всех типов и уменьшение аппаратурных затрат.

5Поставленная цель достигается следующим. Устройство содержит накапливающий сумматор, схему сравнения, триггер, дешифратор кодов команд, два элемента И, два элемента ИЛИ, блок фиксации ошибки.

0 Первый вход первого элемента соединен с первым разрядом входа устройства для подключения к шине данных контролируемой микропроцессорной системы. Второй вход первого элемента И соединен с входом уст5 ройства для подключения с выходом синхронизации упомянутой системы. Третий вход первого элемента И, первый вход второго элемента И и синхровход триггера соединены с тактовым входом устройства.

0Для достижения поставленной цели в

устройство введены три схемы свертки по модулю п. Первый, второй и третий входы первой схемы свертки по модулю п соединены с шиной нулевого потенциала устройст5 ва, а четвертый, пятый и шестой входы - соответственно с первым, вторым и третьим разрядами входа устройства для подключения к шине данных контролируемой системы. Группа выходов первой схемы свертки

0 по модулю п соединена с первой группой информационных входов накапливающего сумматора. Вход дешифратора кодов команд подключен к входу устройства для подключения к шине данных контролируемой

5 системы, его первый и второй выходы - к первым входам первого и второю элементов ИЛИ, а третий выход - к вторым входам первого и второго элементов ИЛИ. Их выходы соединены соответственно с первым и вторым разрядами второй группы информационных входов накапливающего сумматора, третий - m-й раряды второй группы информационных входов которого соединены с шиной нулевого потенциала устройства.

Четвертый выход дешифратора кодов команд соединен с управляющим входом накапливающего сумматора. Выход первого элемента И подключен к информационному входу триггера. Группа входов и группа выходов второй схемы свертки по модулю п соединены соответственно с входом устройства для подключения к шине адреса контролируемой системы и с первой группой входов схемы сравнения. Ее выход подключен к информационному входу блока фиксации ошибки. Вход начальной установки устройства соединен с входами начальной установки триггера блока фиксации ошибки накапливающего сумматора, группа выходов которого соединена с группой входов третьей схемы свертки по модулю п, группа выходов которой подключена к второй группе входов схемы сравнения. Выходтриггера соединен с вторым входом второго элемента И, выход которого подключен к входам синхронизации накапливающего сумматора и блока фиксации ошибки, выход которого является выходом.устройства.

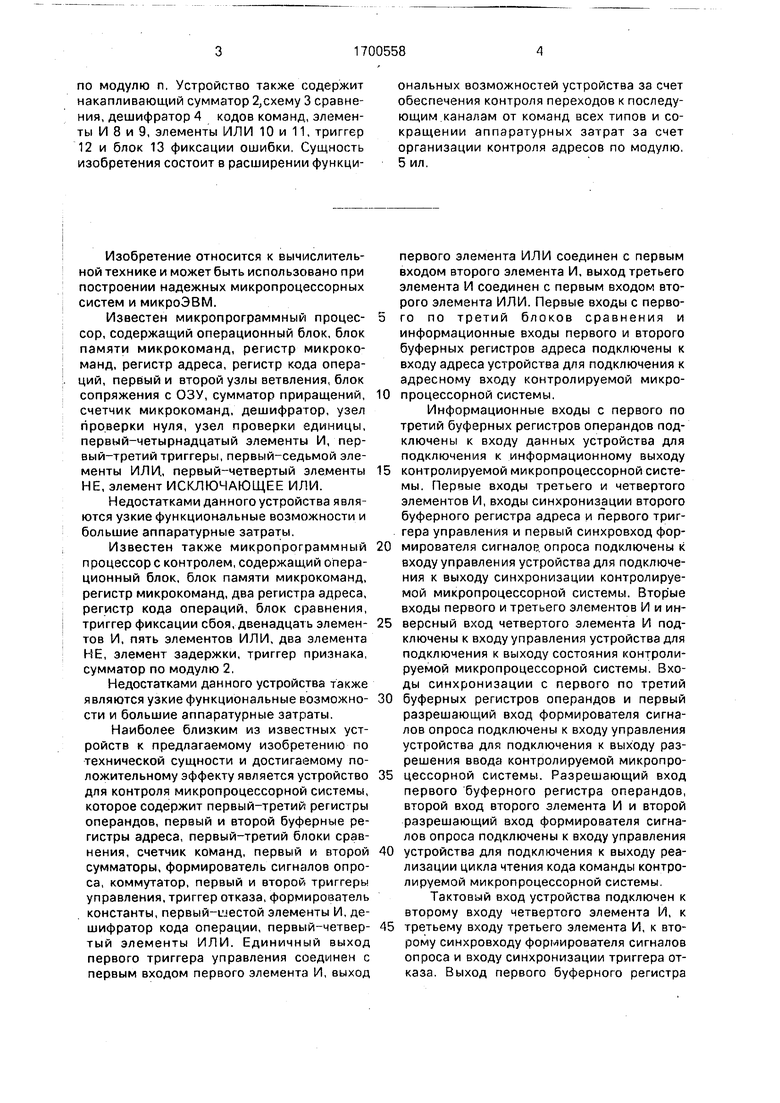

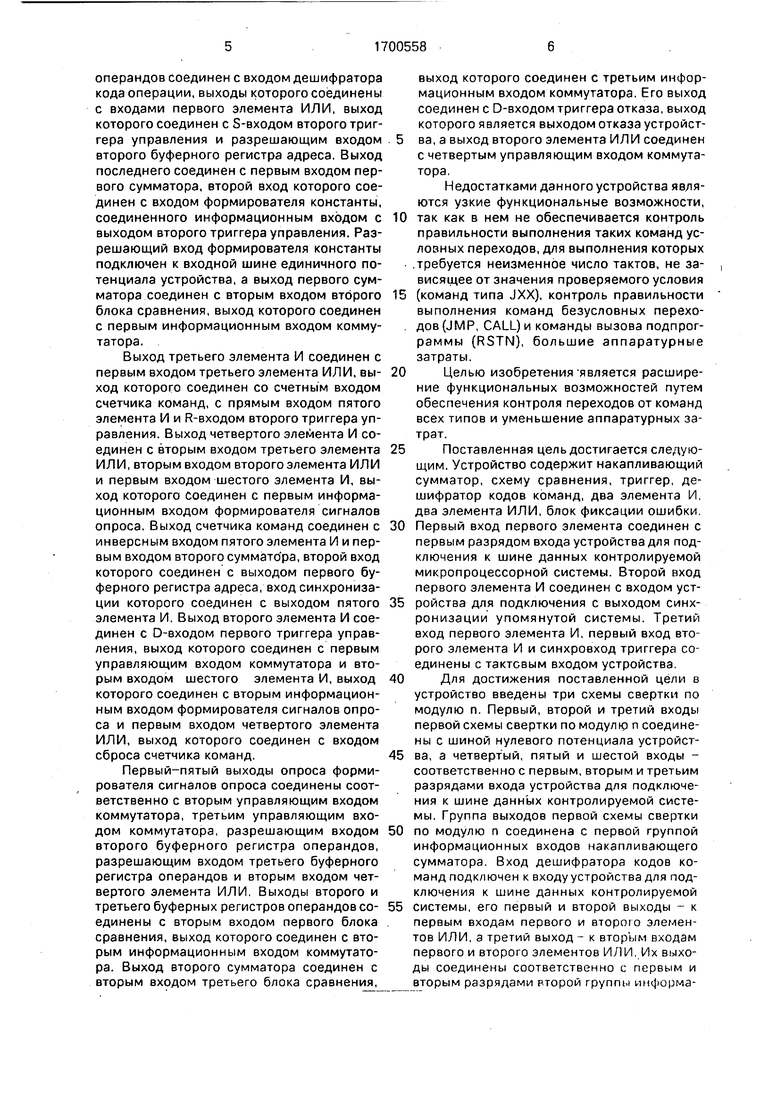

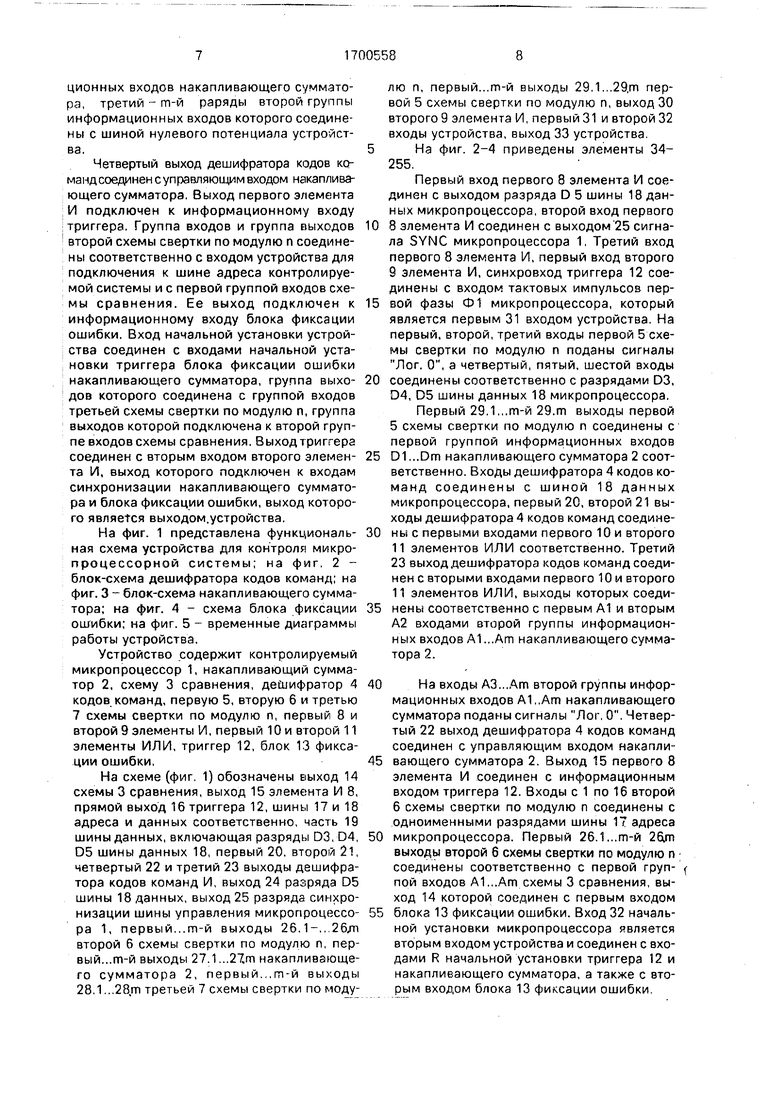

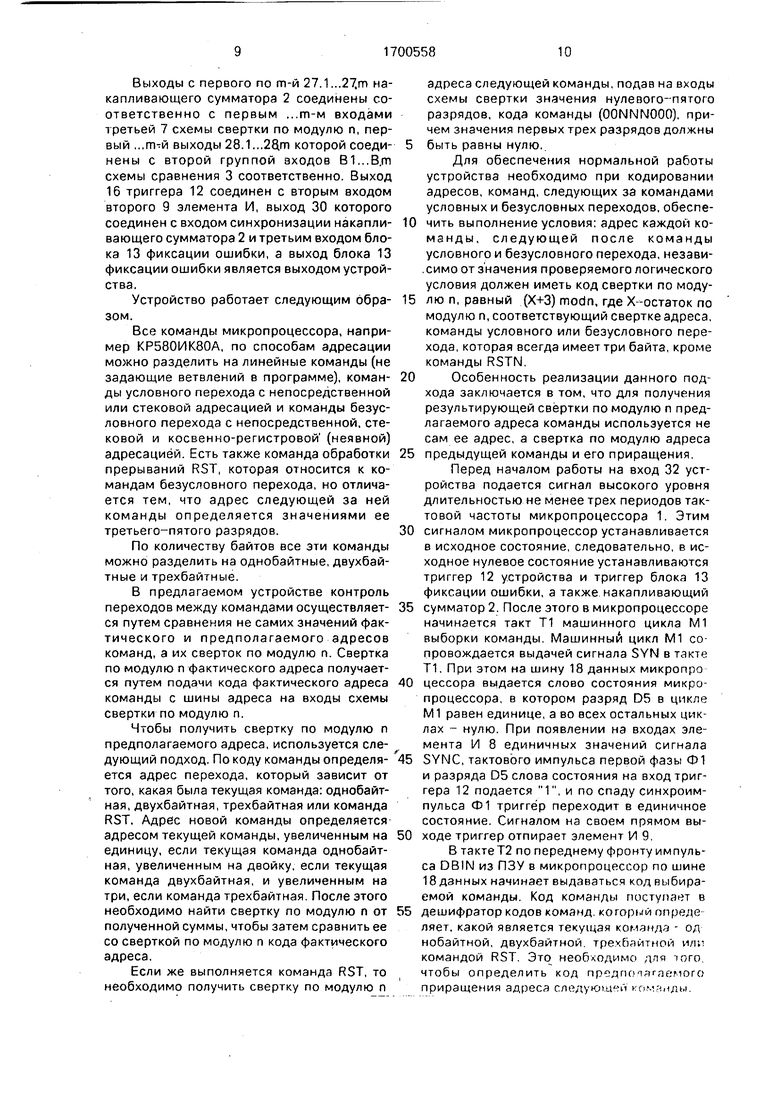

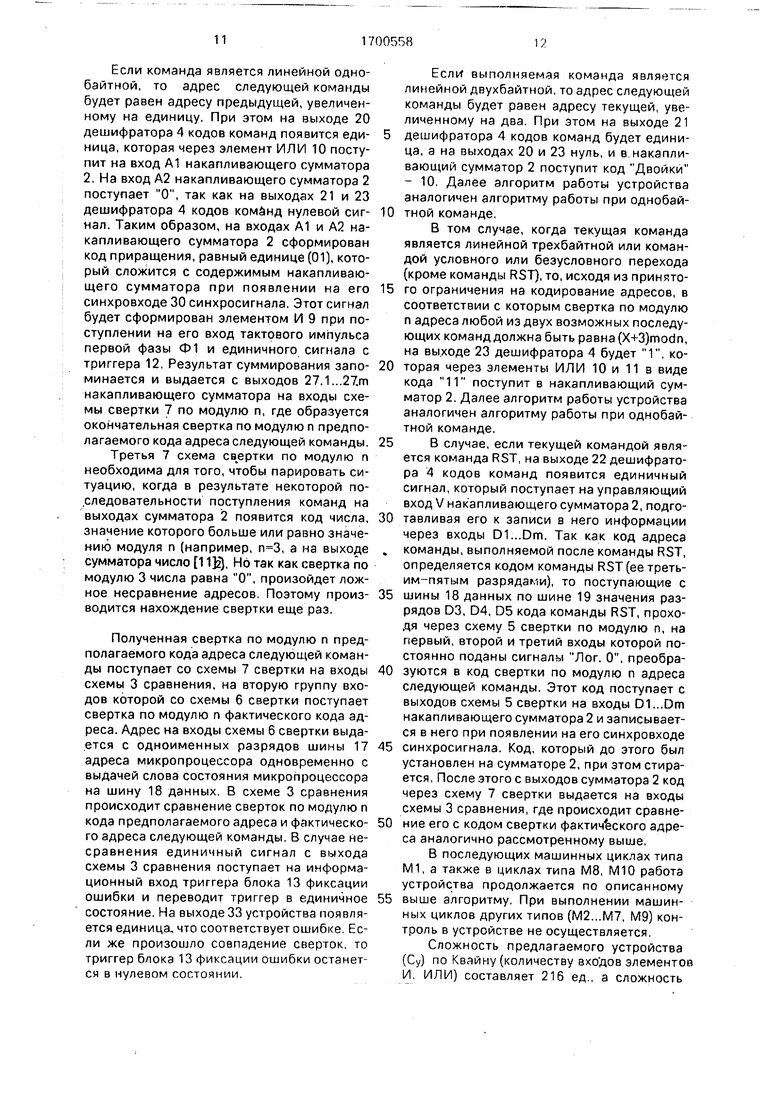

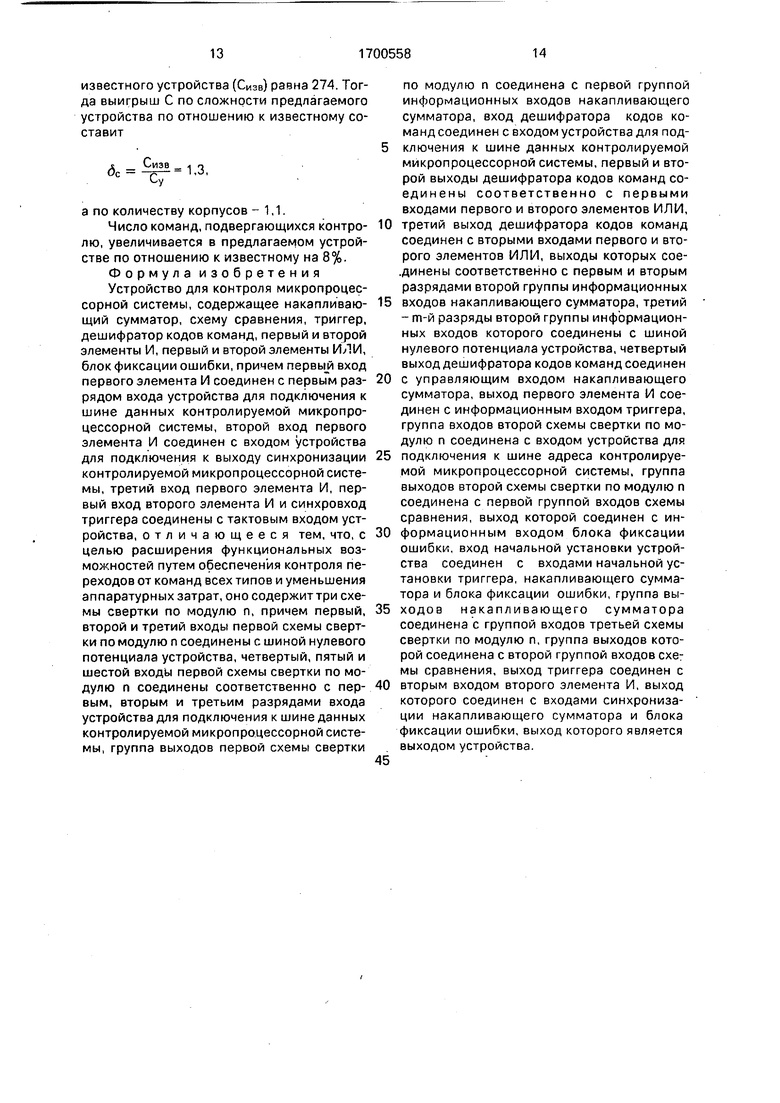

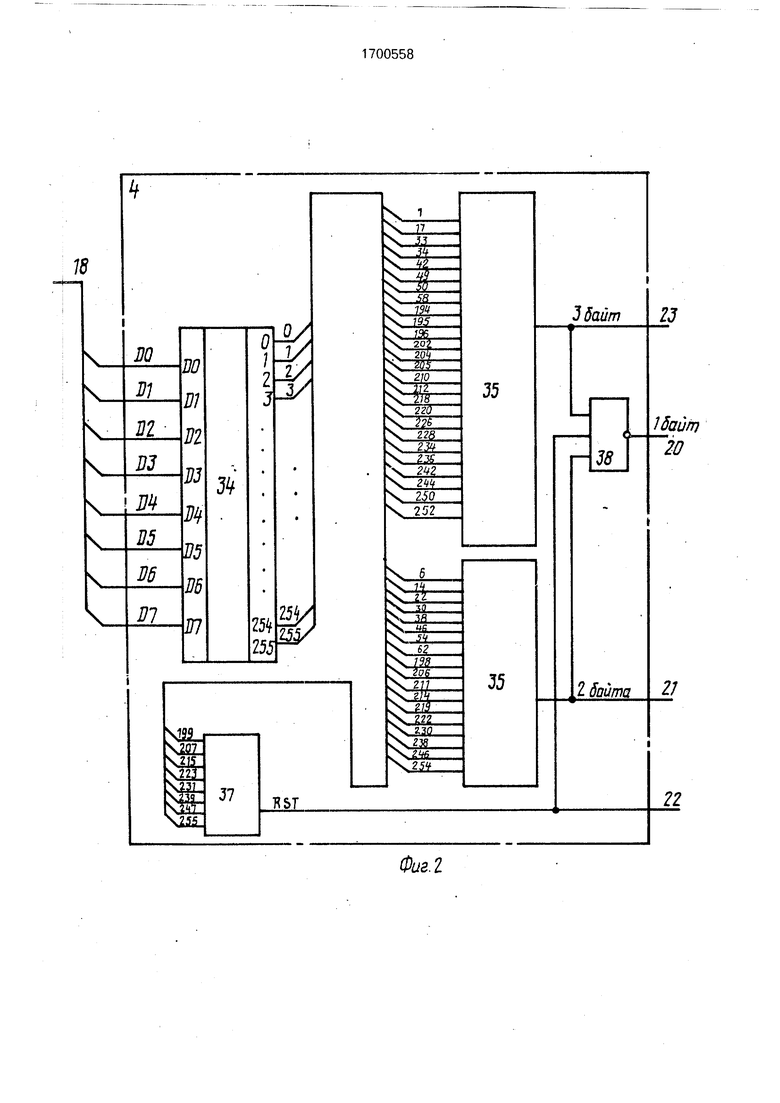

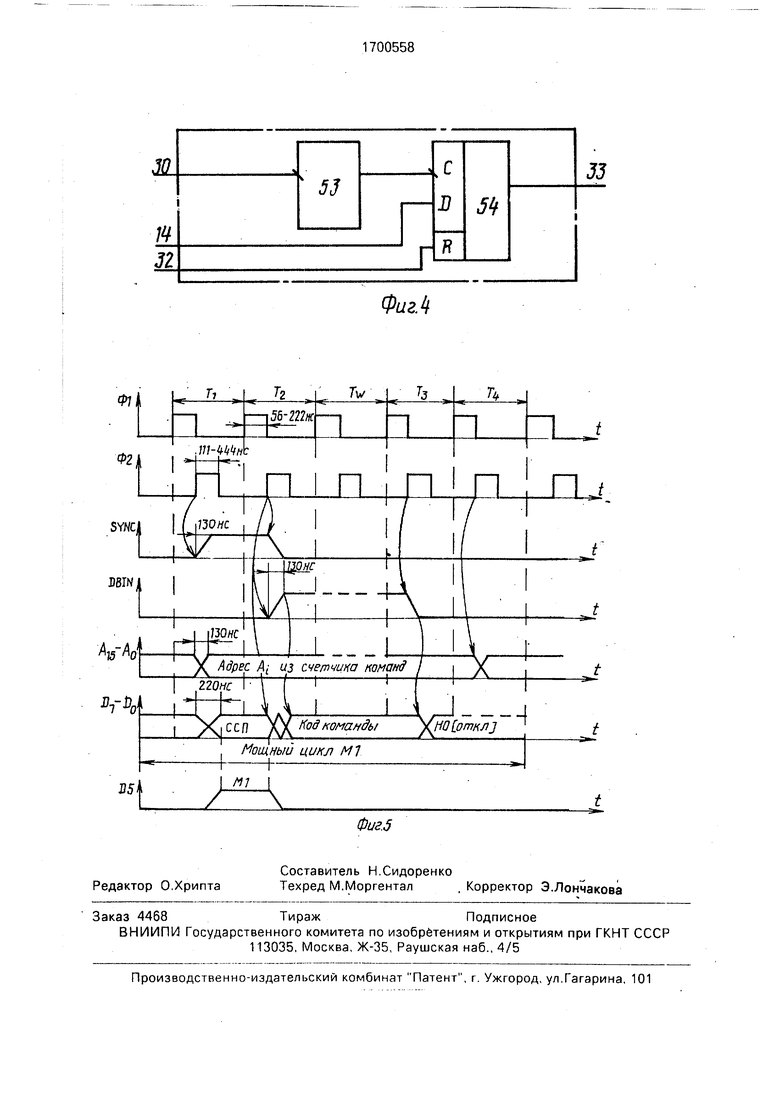

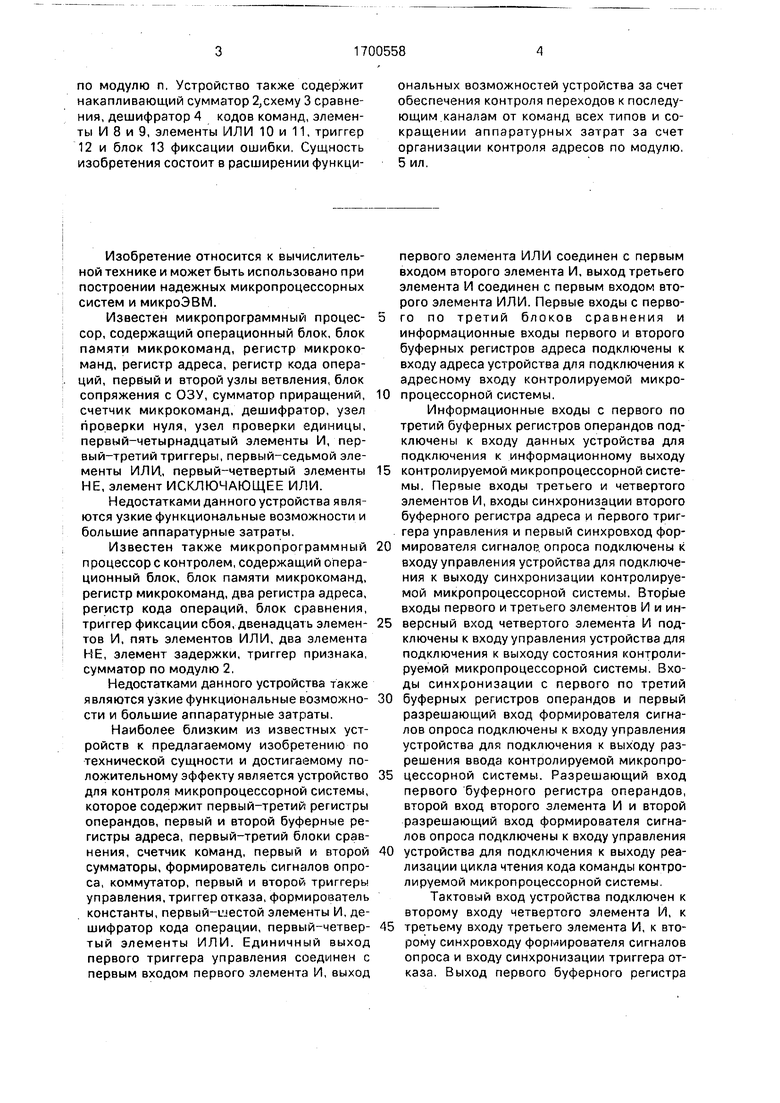

На фиг. 1 представлена функциональная схема устройства для контроля микропроцессорной системы; на фиг. 2 - блок-схема дешифратора кодов команд; на фиг. 3 - блок-схема накапливающего сумматора; на фиг. 4 - схема блока фиксации ошибки; на фиг. 5 - временные диаграммы работы устройства.

Устройство содержит контролируемый микропроцессор 1, накапливающий сумматор 2, схему 3 сравнения, дешифратор 4 кодов команд, первую 5, вторую 6 и третью 7 схемы свертки по модулю п, первый 8 и второй 9 элементы И, первый 10 и второй 11 элементы ИЛИ, триггер 12, блок 13 фиксации ошибки,

На схеме (фиг. 1) обозначены выход 14 схемы 3 сравнения, выход 15 элемента И 8, прямой выход 16 триггера 12, шины 17 и 18 адреса и данных соответственно, часть 19 шины данных, включающая разряды D3, D4, D5 шины данных 18, первый 20, второй 21, четвертый 22 и третий 23 выходы дешифратора кодов команд И, выход 24 разряда D5 шины 18 данных, выход 25 разряда синхронизации шины управления микропроцессора 1, первый...m-й выходы 26.1-..26Я1 второй 6 схемы свертки по модулю п, первый...m-й выходы 27.1 ...27.ГЛ накапливающего сумматора 2, первый.,.m-й выходы 28.1...28.т третьей 7 схемы свертки по модулю п, первый...m-й выходы 29.1...29,т первой 5 схемы свертки по модулю п, выход 30 второго 9 элемента И, первый 31 и второй 32 входы устройства, выход 33 устройства.

На фиг. 2-4 приведены элементы 34255.

Первый вход первого 8 элемента И соединен с выходом разряда D 5 шины 18 данных микропроцессора, второй вход первого

0 8 элемента И соединен с выходом 25 сигнала SYNC микропроцессора 1, Третий вход первого 8 элемента И, первый вход второго 9 элемента И, синхровход триггера 12 соединены с входом тактовых импульсов пер5 вой фазы Ф1 микропроцессора, который является первым 31 входом устройства. На первый, второй, третий входы первой 5 схемы свертки по модулю п поданы сигналы Лог. О, а четвертый, пятый, шестой входы

0 соединены соответственно с разрядами D3, D4, D5 шины данных 18 микропроцессора. Первый 29.1,..m-й 29.гп выходы первой

5схемы свертки по модулю п соединены с первой группой информационных входов

5 D1 ,..Dm накапливающего сумматора 2 соответственно. Входы дешифратора 4 кодов ко- манд соединены с шиной 18 данных микропроцессора, первый 20, второй 21 выходы дешифратора 4 кодов команд соедине0 ны с первыми входами первого 10 и второго 11 элементов ИЛИ соответственно. Третий 23 выход дешифратора кодов команд соединен с вторыми входами первого 10 и второго 11 элементов ИЛИ, выходы которых соеди5 нены соответственно с первым А1 и вторым А2 входами второй группы информационных входов А1 ...Am накапливающего сумматора 2.

0На входы A3...Am второй группы информационных входов А1..Am накапливающего сумматора поданы сигналы Лог. О. Четвертый 22 выход дешифратора 4 кодов команд соединен с управляющим входом накапли5 вающего сумматора 2. Выход 15 первого 8 элемента И соединен с информационным входом триггера 12. Входы с 1 по 16 второй

6схемы свертки по модулю п соединены с одноименными разрядами шины 17 адреса

0 микропроцессора. Первый 26.1...m-й 26jn выходы второй 6 схемы свертки по модулю п соединены соответственно с первой труп- пой входов А1...Ат схемы 3 сравнения, выход 14 которой соединен с первым входом

5 блока 13 фиксации ошибки. Вход 32 начальной установки микропроцессора является вторым входом устройства и соединен с входами R начальной установки триггера 12 и накапливающего сумматора, а также с вторым входом блока 13 фиксации ошибки.

Выходы с первого по m-й 27.1...27.т накапливающего сумматора 2 соединены соответственно с первым ...m-м входами третьей 7 схемы свертки по модулю п, первый ...m-й выходы 28.1..,28.т которой соеди- йены с второй группой входов В1...В.гл схемы сравнения 3 соответственно. Выход 16 триггера 12 соединен с вторым входом второго 9 элемента И, выход 30 которого соединен с входом синхронизации накапли- вающего сумматора 2 и третьим входом блока 13 фиксации ошибки, а выход блока 13 фиксации ошибки является выходом устройства.

Устройство работает следующим обра- зом.

Все команды микропроцессора, например КР580ИК80А, по способам адресации можно разделить на линейные команды (не задающие ветвлений в программе), коман- ды условного перехода с непосредственной или стековой адресацией и команды безусловного перехода с непосредственной,стековой и косвенно-регистровой (неявной) адресацией. Есть также команда обработки прерываний RST, которая относится к командам безусловного перехода, но отличается тем, что адрес следующей за ней команды определяется значениями ее третьего-пятого разрядов.

По количеству байтов все эти команды можно разделить на однобайтные, двухбайтные и трехбайтные.

В предлагаемом устройстве контроль переходов между командами осуществляет- ся путем сравнения не самих значений фактического и предполагаемого адресов команд, а их сверток по модулю п. Свертка по модулю п фактического адреса получается путем подачи кода фактического адреса команды с шины адреса на входы схемы свертки по модулю п.

Чтобы получить свертку по модулю п предполагаемого адреса, используется еле- дующий подход. По коду команды определи- ется адрес перехода, который зависит от того, какая была текущая команда: однобайтная, двухбайтная, трехбайтная или команда RST. Адрес новой команды определяется адресом текущей команды, увеличенным на единицу, если текущая команда однобайтная, увеличенным на двойку, если текущая команда двухбайтная, и увеличенным на три, если команда трехбэйтная. После этого необходимо найти свертку по модулю п от полученной суммы, чтобы затем сравнить ее со сверткой по модулю п кода фактического адреса.

Если же выполняется команда RST, то необходимо получить свертку по модулю п

адреса следующей команды, подав на входы схемы свертки значения нулевого-пятого разрядов, кода команды (OONNIMOOO), причем значения первых трех разрядов должны быть равны нулю.

Для обеспечения нормальной работы устройства необходимо при кодировании адресов, команд, следующих за командами условных и безусловных переходов, обеспечить выполнение условия: адрес каждой команды, следующей после команды условного и безусловного перехода, незави- .симо от значения проверяемого логического условия должен иметь код свертки по модулю п, равный (Х+3) modn, где Х-остаток по модулю п, соответствующий свертке адреса, команды условного или безусловного перехода, которая всегда имеет три байта, кроме команды RSTN.

Особенность реализации данного подхода заключается в том, что для получения результирующей свертки по модулю п предлагаемого адреса команды используется не сам ее адрес, а свертка по модулю адреса предыдущей команды и его приращения.

Перед началом работы на вход 32 устройства подается сигнал высокого уровня длительностью не менее трех периодов тактовой частоты микропроцессора 1. Этим сигналом микропроцессор устанавливается в исходное состояние, следовательно, в исходное нулевое состояние устанавливаются триггер 12 устройства и триггер блока 13 фиксации ошибки, а также накапливающий сумматор 2. После этого в микропроцессоре начинается такт Т1 машинного цикла М1 выборки команды. Машинный цикл М1 сопровождается выдачей сигнала SYN в такте Т1. При этом на шину 18 данных микропро цессора выдается слово состояния микропроцессора, в котором разряд D5 в цикле М1 равен единице, а во всех остальных циклах - нулю. При появлении на входах элемента И 8 единичных значений сигнала SYNC, тактового импульса первой фазы Ф1 и разряда D5 слова состояния на вход триггера 12 подается 1, и по спаду синхроимпульса Ф1 триггер переходит в единичное состояние. Сигналом на своем прямом выходе триггер отпирает элемент И 9.

В такте Т2 по переднему фронту импульса DBIN из ПЗУ в микропроцессор по шине 18 данных начинает выдаваться код выбираемой команды. Код команды поступает в дешифратор кодов команд который опреде ляет, какой является текущая команда - од нобайтной, двухбайтной трехбайтной ил;1 командой RST. Это необходимо для того чтобы определить код продпотдгаемого приращения адреса следующей ко - чнды

Если команда является линейной однобайтной, то адрес следующей команды будет равен адресу предыдущей, увеличенному на единицу. При этом на выходе 20 дешифратора 4 кодов команд появится единица, которая через элемент ИЛИ 10 поступит на вход А1 накапливающего сумматора 2. На вход А2 накапливающего сумматора 2 поступает О, так как на выходах 21 и 23 дешифратора 4 кодов команд нулевой сигнал. Таким образом, на входах А1 и А2 накапливающего сумматора 2 сформирован код приращения, равный единице (01), который сложится с содержимым накапливающего сумматора при появлении на его синхровходе 30 синхросигнала. Этот сигнал будет сформирован элементом И 9 при поступлении на его вход тактового импульса первой фазы Ф1 и единичного сигнала с триггера 12, Результат суммирования запоминается и выдается с выходов 27.1...27.т накапливающего сумматора на входы схемы свертки 7 по модулю п, где образуется окончательная свертка по модулю п предполагаемого кода адреса следующей команды.

Третья 7 схема свертки по модулю п необходима для того, чтобы парировать ситуацию, когда в результате некоторой последовательности поступления команд на выходах сумматора 2 появится код числа, значение которого больше или равно значению модуля п (например, , а на выходе сумматора число 11J2), Но так как свертка по модулю 3 числа равна О, произойдет ложное несравнение адресов. Поэтому производится нахождение свертки еще раз.

Полученная свертка по модулю п предполагаемого кода адреса следующей команды поступает со схемы 7 свертки на входы схемы 3 сравнения, на вторую группу входов которой со схемы 6 свертки поступает свертка по модулю п фактического кода адреса. Адрес на входы схемы 6 свертки выдается с одноименных разрядов шины 17 адреса микропроцессора одновременно с выдачей слова состояния микропроцессора на шину 18 данных, В схеме 3 сравнения происходит сравнение сверток по модулю п кода предполагаемого адреса и фактического адреса следующей команды. В случае несравнения единичный сигнал с выхода схемы 3 сравнения поступает на информационный вход триггера блока 13 фиксации ошибки и переводит триггер в единичное состояние. На выходе33 устройства появляется единица, что соответствует ошибке Если же произошло совпадение сверток, то триггер блока 13 фиксации ошибки останется в нулевом состоянии.

Если выполняемая команда является линейной двухбайтной, то адрес следующей команды будет равен адресу текущей, увеличенному на два. При этом на выходе 21

дешифратора 4 кодов команд будет единица, а на выходах 20 и 23 нуль, и в накапливающий сумматор 2 поступит код Двойки - 10. Далее алгоритм работы устройства аналогичен алгоритму работы при однобай0 тной команде,

В том случае, когда текущая команда является линейной трехбайтной или командой условного или безусловного перехода (кроме команды RST), то, исходя из принято5 го ограничения на кодирование адресов, в соответствии с которым свертка по модулю п адреса любой из двух возможных последующих команд должна быть равна (X+3)modn, на выходе 23 дешифратора 4 будет 1, ко0 торая через элементы ИЛИ 10 и 11 в виде кода 11 поступит в накапливающий сумматор 2. Далее алгоритм работы устройства аналогичен алгоритму работы при однобайтной команде.

5В случае, если текущей командой является команда RST, на выходе 22 дешифратора 4 кодов команд появится единичный сигнал, который поступает на управляющий вход V накапливающего сумматора 2, подго0 тавливая его к записи в него информации через входы D1...Dm. Так как код адреса команды, выполняемой после команды RST, определяется кодом команды RST(ее третьим-пятым разрядами), то поступающие с

5 шины 18 данных по шине 19 значения разрядов D3, D4, D5 кода команды RST, проходя через схему 5 свертки по модулю п, на первый, второй и третий входы которой постоянно поданы сигналы Лог. О, преобра0 зуются в код свертки по модулю п адреса следующей команды. Этот код поступает с выходов схемы 5 свертки на входы D1...Dm накапливающего сумматора 2 и записывается в него при появлении на его синхровходе

5 синхросигнала. Код, который до этого был установлен на сумматоре 2, при этом стирается, После этого с выходов сумматора 2 код через схему 7 свертки выдается на входы схемы 3 сравнения, где происходит сравне0 ние его с кодом свертки фактического адреса аналогично рассмотренному выше.

В последующих машинных циклах типа М1, а также в циклах типа М8, М10 работа устройства продолжается по описанному

5 выше алгоритму. При выполнении машинных циклов других типов (М2...М7, М9) контроль в устройстве не осуществляется.

Сложность предлагаемого устройства (Су) по Квайну (количеству входов элементов И, ИЛИ) составляет 216 ед , а сложность

известного устройства (Сизв) равна 274. Тогда выигрыш С по сложности предлагаемого устройства по отношению к известному составит

tСиЗВ

Ос

Су

1,3,

а по количеству корпусов - 1,1.

Число команд, подвергающихся контролю, увеличивается в предлагаемом устройстве по отношению к известному на 8%. Формула изобретения Устройство для контроля микропроцессорной системы, содержащее накапливающий сумматор, схему сравнения, триггер, дешифратор кодов команд, первый и второй элементы И, первый и второй элементы ИЛИ, блок фиксации ошибки, причем первый вход первого элемента И соединен с первым разрядом входа устройства для подключения к шине данных контролируемой микропроцессорной системы, второй вход первого элемента И соединен с входом устройства для подключения к выходу синхронизации контролируемой микропроцессорной системы, третий вход первого элемента И, первый вход второго элемента И и синхровход триггера соединены с тактовым входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения контроля переходов от команд всех типов и уменьшения аппаратурных затрат, оно содержит три схемы свертки по модулю п, причем первый, второй и третий входы первой схемы свертки по модулю п соединены с шиной нулевого потенциала устройства, четвертый, пятый и шестой входы первой схемы свертки по модулю п соединены соответственно с первым, вторым и третьим разрядами входа устройства для подключения к шине данных контролируемой микропроцессорной системы, группа выходов первой схемы свертки

0

5

0

5

0

5

0

5

по модулю п соединена с первой группой информационных входов накапливающего сумматора, вход дешифратора кодов команд соединен с входом устройства для подключения к шине данных контролируемой микропроцессорной системы, первый и второй выходы дешифратора кодов команд со- единены соответственно с первыми входами первого и второго элементов ИЛИ, третий выход дешифратора кодов команд соединен с вторыми входами первого и второго элементов ИЛИ, выходы которых сое- .динены соответственно с первым и вторым разрядами второй группы информационных входов накапливающего сумматора, третий - m-й разряды второй группы информационных входов которого соединены с шиной нулевого потенциала устройства, четвертый выход дешифратора кодов команд соединен с управляющим входом накапливающего сумматора, выход первого элемента И соединен с информационным входом триггера, группа входов второй схемы свертки по модулю п соединена с входом устройства для подключения к шине адреса контролируемой микропроцессорной системы, группа выходов второй схемы свертки по модулю п соединена с первой группой входов схемы сравнения, выход которой соединен с информационным входом блока фиксации ошибки, вход начальной установки устройства соединен с входами начальной установки триггера, накапливающего сумматора и блока фиксации ошибки, группа выходов накапливающего сумматора соединена с группой входов третьей схемы свертки по модулю п, группа выходов которой соединена с второй группой входов схемы сравнения, выход триггера соединен с вторым входом второго элемента И, выход которого соединен с входами синхронизации накапливающего сумматора и блока фиксации ошибки, выход которого является выходом устройства.

18

so

л ж

Ж Ж

S5.

Ж.

VI

#

IZ

X

s±a

UG

JV

J5

2 Ji J/77g

27

fO c-i

#

SYNC

DS

/

ФигЛ

i Ii

y QLomM |f

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-23—Публикация

1990-01-09—Подача