Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных матричных, конвейерных, систолических, векторных и других процессоров, в которых в процессе обработки происходит движение данных в вычислительной среде, вычислительных систем с динамической архитектурой.

Цель изобретения - повышение достоверности передаваемой транзитной информации при одновременном сокращении числа внешних связей устройства.

Сущность предлагаемого изобретения состоит в следующем. Во время выполнения программы i-Й процессорный элемент (ПЭ) вычислительной системы может выдавать в один из двух каналов команду передачи управления (команду обмена). Формат данной команды представляется в виде

кпр # к

& ч on йе

Г Д..

К пр - номер (код) ПЭ приемника

информации; К

on

- номер (код) операции, которую должен выполнить ПЭ приемник информации; S - код сигнатуры; v # - знак конкатенации (сцепления) .

Каждому ПЭ, входящему в состав вычислительной системы, присваивается номер (идентификатор), определяющий его местоположение в матрице ПЭ. Обмен командами передачи управления может производиться между ПЭ системы либо по строке ПЭ (слева направо), либо в столбце ПЭ (снизу ввеох). ПЭ, расположенные в одном столбце (строке) образуют кольцевую структуру. Поэтому команда обмена с (q, V)TO ПЭ (q,V6 1, п) поступает либо на (q+1, )-й ПЭ (движение по строке ПЭ), либо на (q,+1)-ri ПЭ (движение по столбцу ПЭ). Очевидно, при организации двойного конвейера перемещения информации между ПЭ системы организация движения вертикаль-горизонталь тождественна движению горизонталь- вертикаль. Пусть движение информации в матрице ПЭ будет организовано при принципу вертикаль-горизонталь При такой дисциплине организации взаимодействия отдельных ПЗ характеры-

0

5

0

5

0

5

0

5

0

5

стикой маршрута продвижения информации может служить некоторое число (сигнатура).

При выдаче команды обмена дополняется из отдельного блока памяти сигнатурой, идентифицирующей путь прохождения информации между ПЭ. При поступлении сообщения на соседний ПЭ системы определяется, ему ли предназначена поступившая информация. Определение принадлежности информации происходит путем сравнения кода ПЭ приемника информации с кодом (идентификатором) ПЭ. При несовпадении этих кодов поступившая ишЬорма- ция отправляется к следующему ПЭ и т.д. до совпадения кодов либо Е столбце, либо в строке П З.

При совпадении одного из двух кодов меняется направление продвижения информации.

При мере транзитного прохождения информации код сигнатуры модифицируется идентификаторами (процессорных элементов) и направлениями выдачи информации. При достижении ПЭ приемника информации (сообщения) полученная сигнатура должна быть нулевой в противном случае пройденный маршрут не соответствует требуемому и, .следовательно, произошла ошибка в назначении поступившего на обслуживание сообщения (ошибка адреса).

При совпадении адресной части сообщения с кодом-идентифукатором ПЭ и нулевой сигнатурой информация о коде операции заносится в буферный запоминающий блок для дальнейшего обслуживания в соответствии с правилом: первым пришел - первым обслужен (организация типа ).

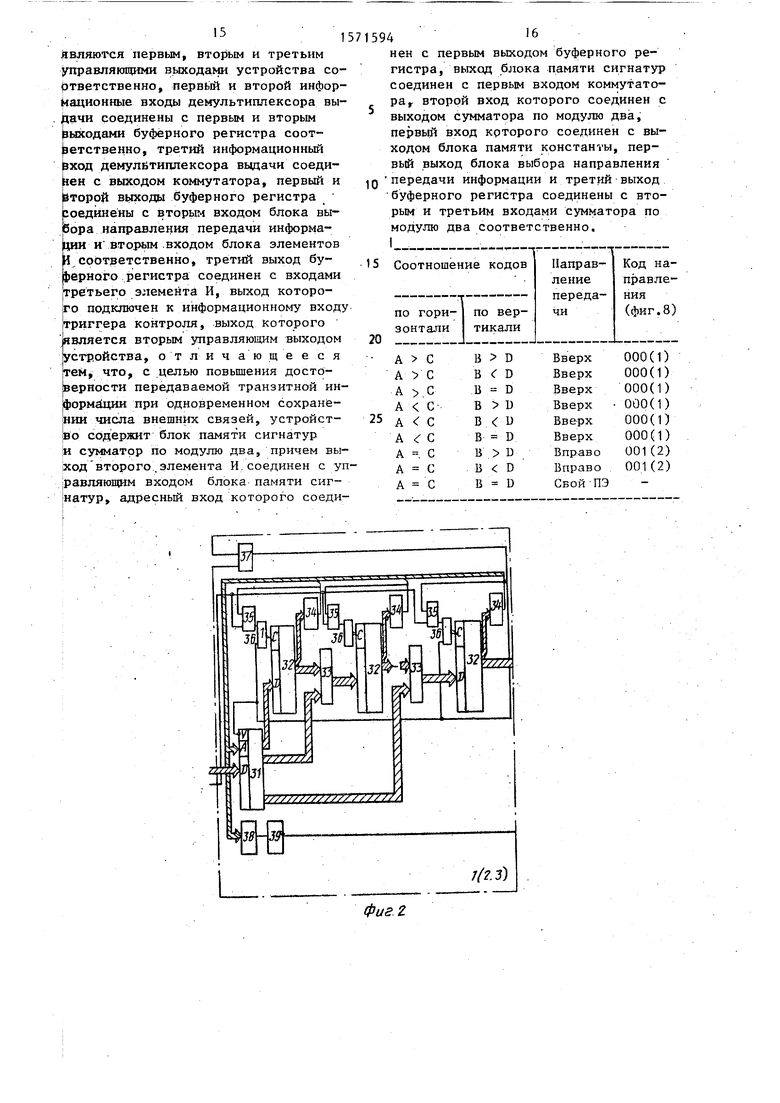

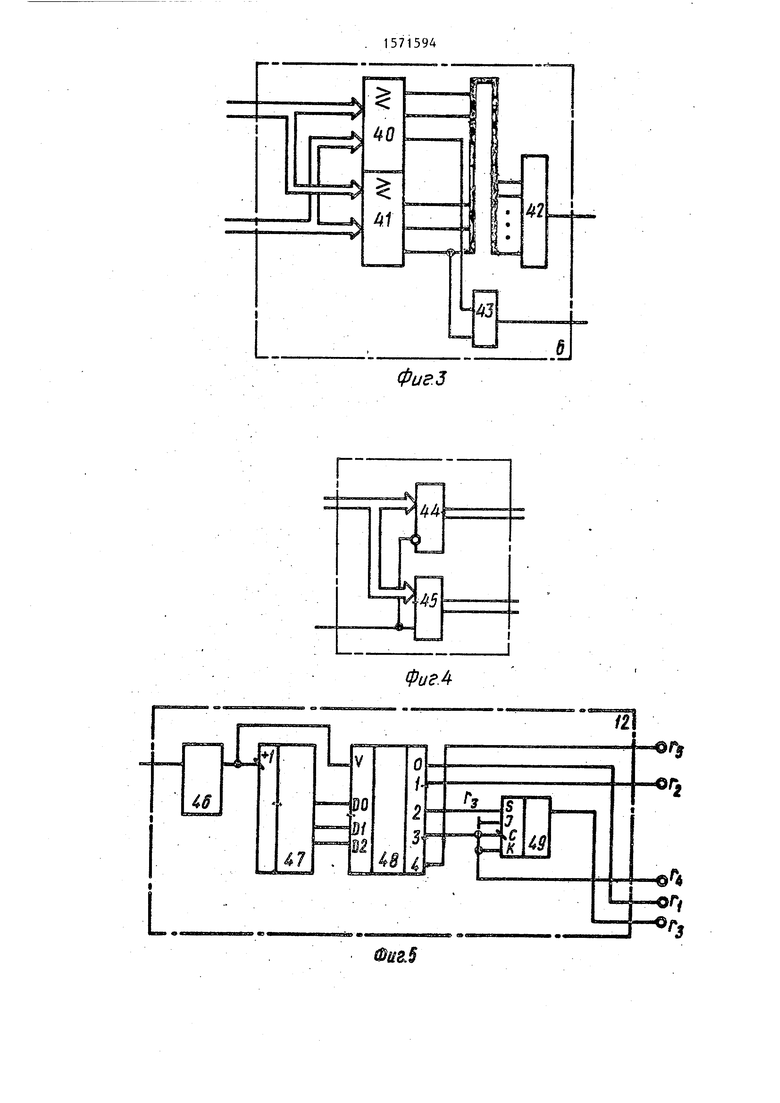

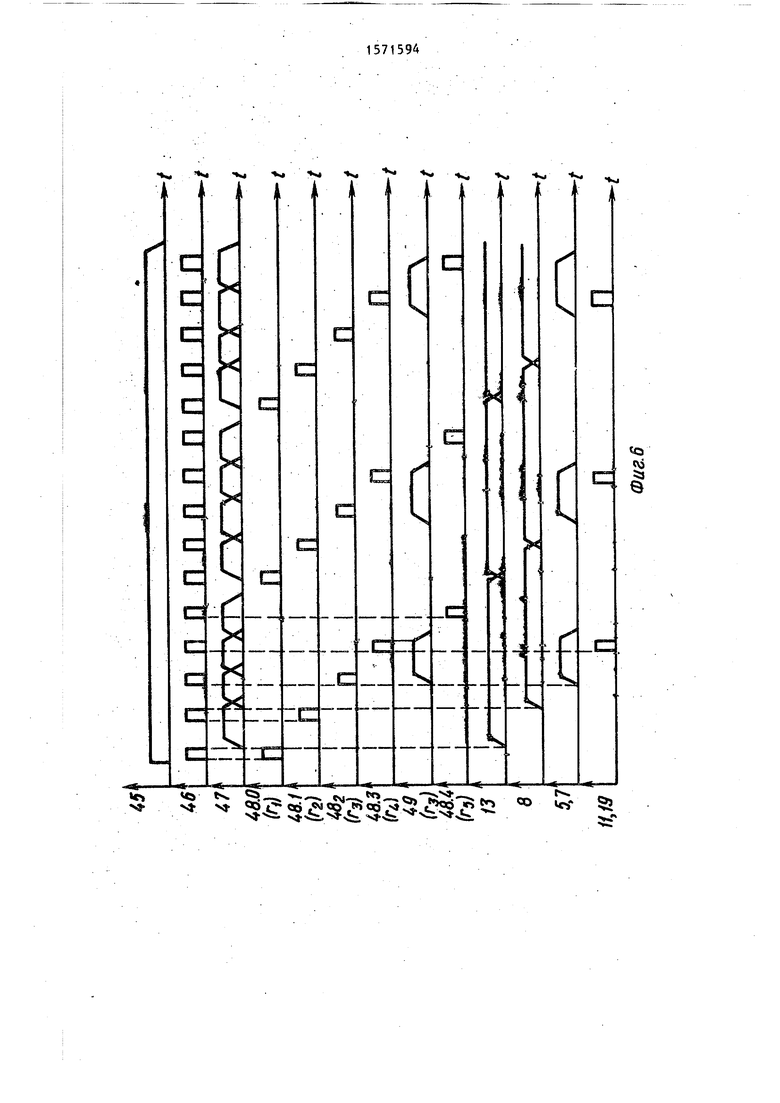

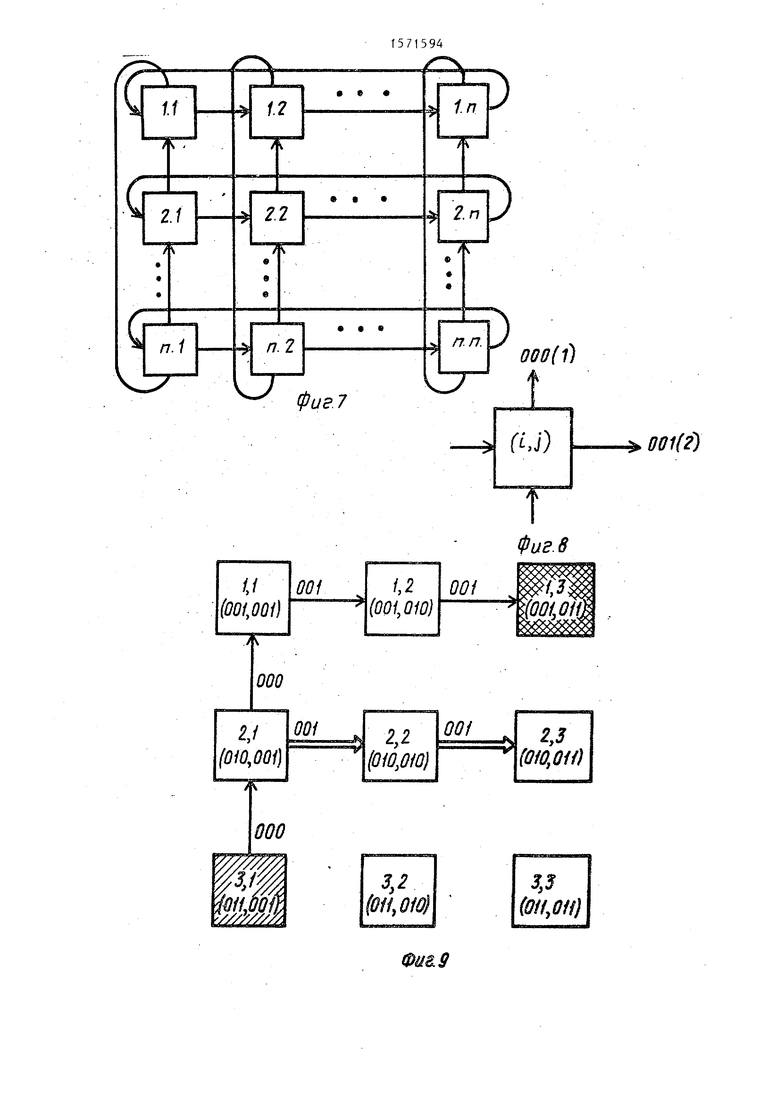

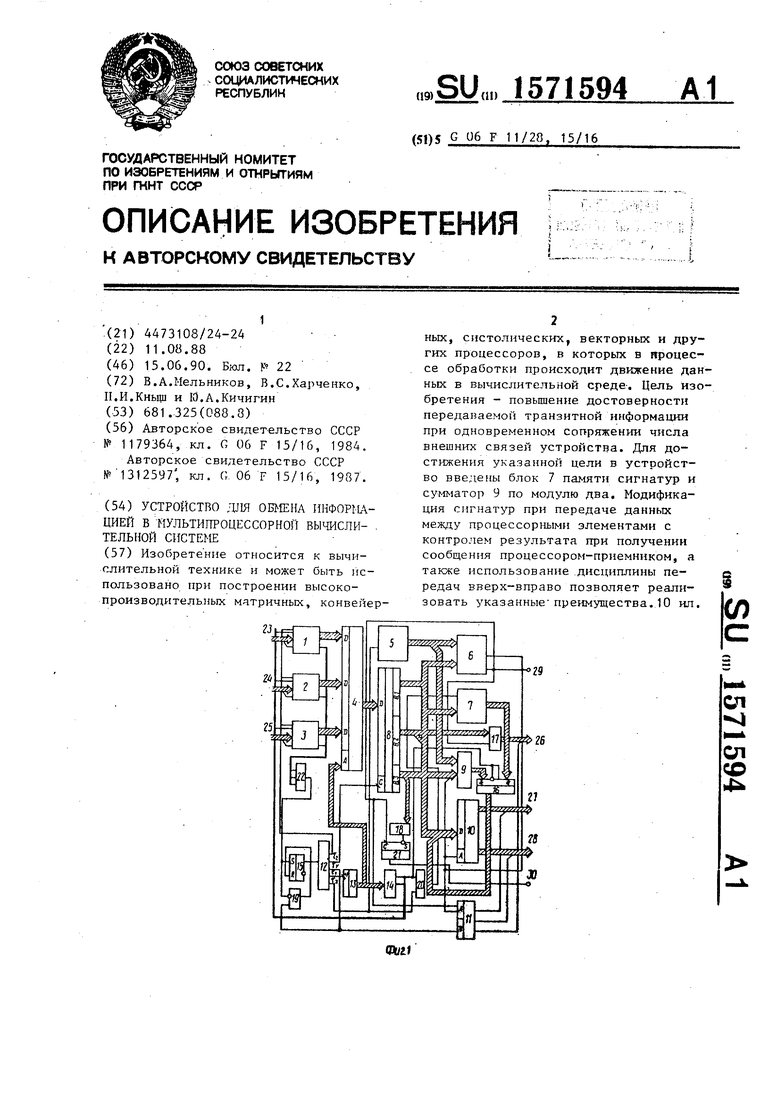

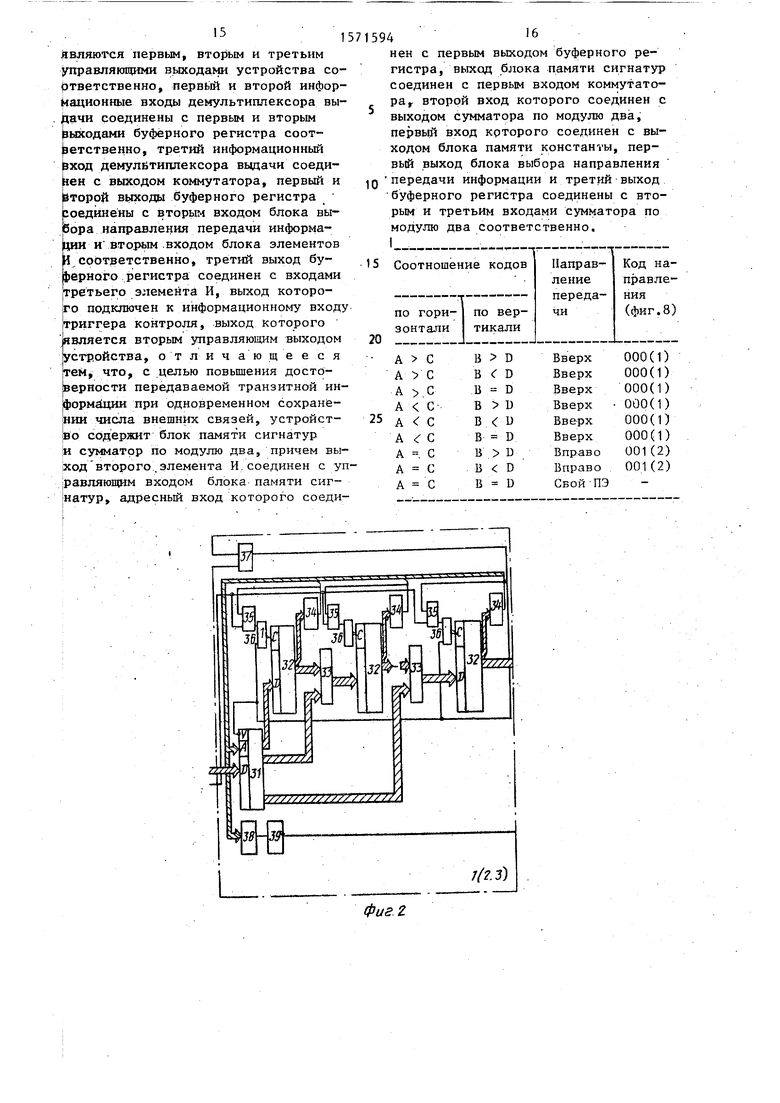

На фиг.1 представлена функциональная схема устройства для обмена информацией в мультипроцессорной вычислительной системе; на фиг.2 - функциональная схема блока памяти сообщений (ВПС); на фиг. 5 - функциональная схема блока выбо эа направления передачи информации БВНПИ); на фиг.4 - функциональная с сема демуль- типлексора выдачи; на фиг . 5 «- функциональная схема распредели геля импульсов (РИ); на фиг. 6 - времеьные диаграммы функционирования устройства; на фиг.7 - пример организации однородной вычислительной системы из отдельных процессорных элементов; на фиг.8 - пример кодирования направ51

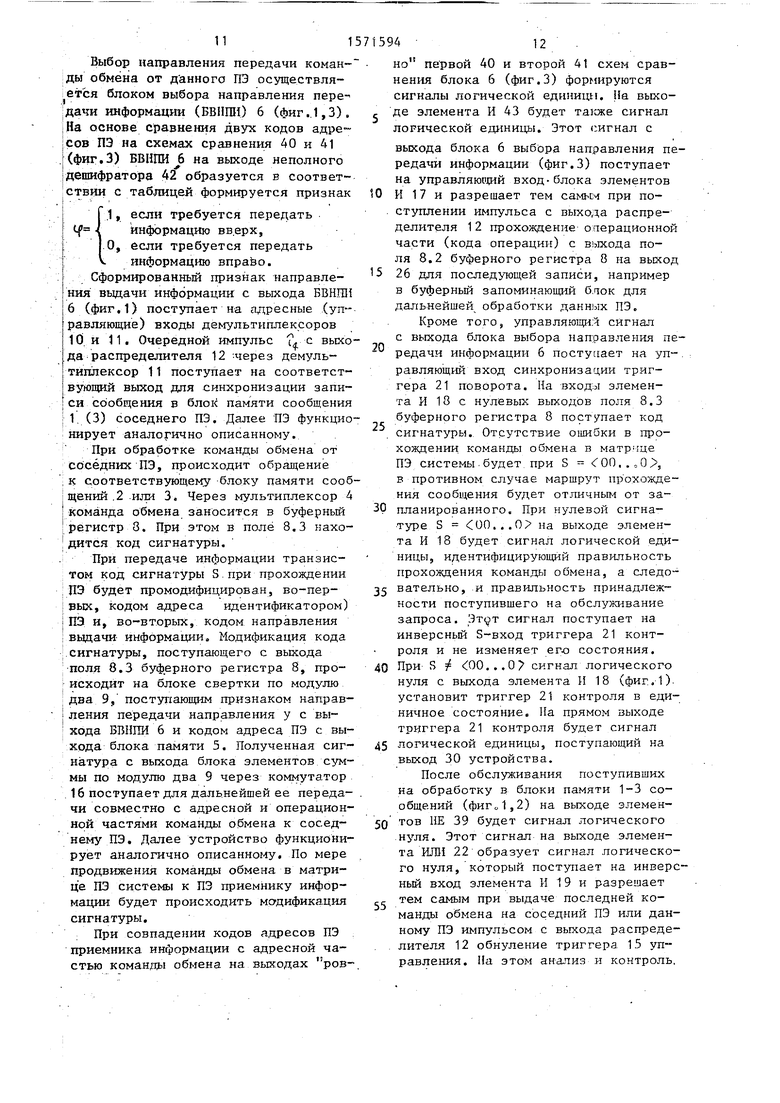

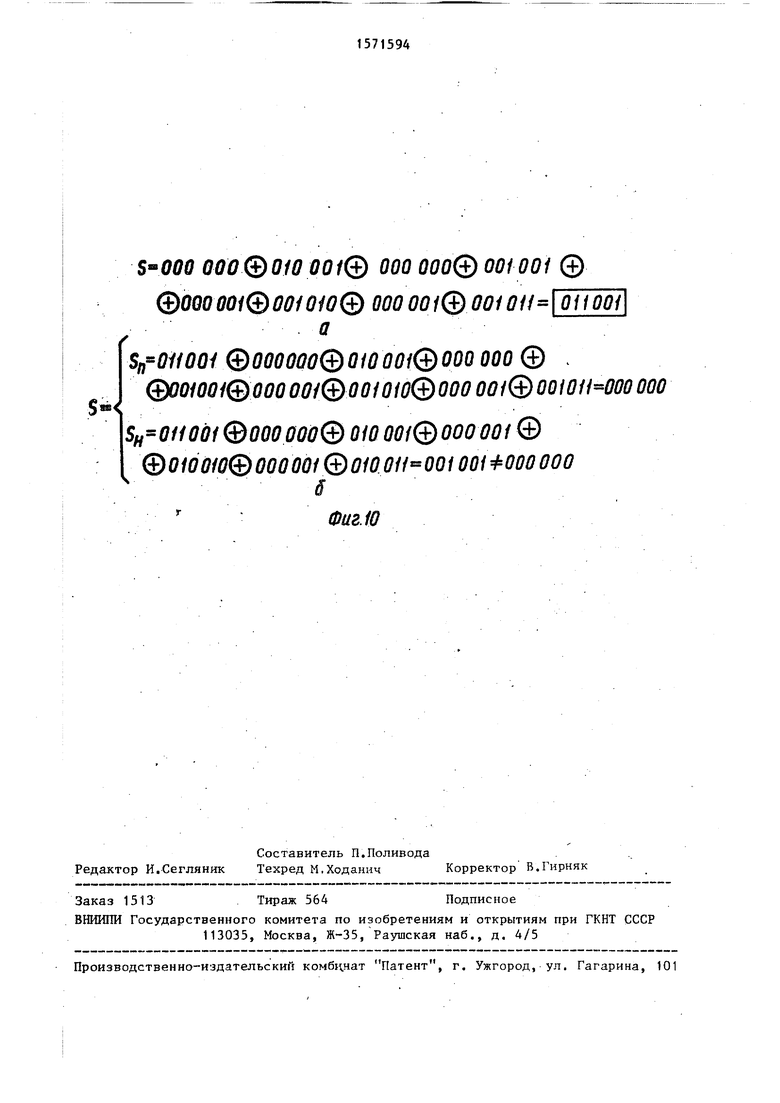

лений (i.j)-ro гфоцессорного элемента; на фиг.9 - пример кодирования матрицы Ю однородной вычислительной системы размерности 3x3 и направ лений передач сообщений (команд)обмена) от ПЭ (3,1) к ПЭ (1,3); на фиг.10 а - пример кода сигнатуры, хранимого в специальном блоке памяти и используемого при передаче команды обмена от ПЭ (3,1) к ПЭ (1,3); на фиг.106- пример модификации кода сигнатуры при правильной (S) и неправильной (йи) передаче команды обмена.

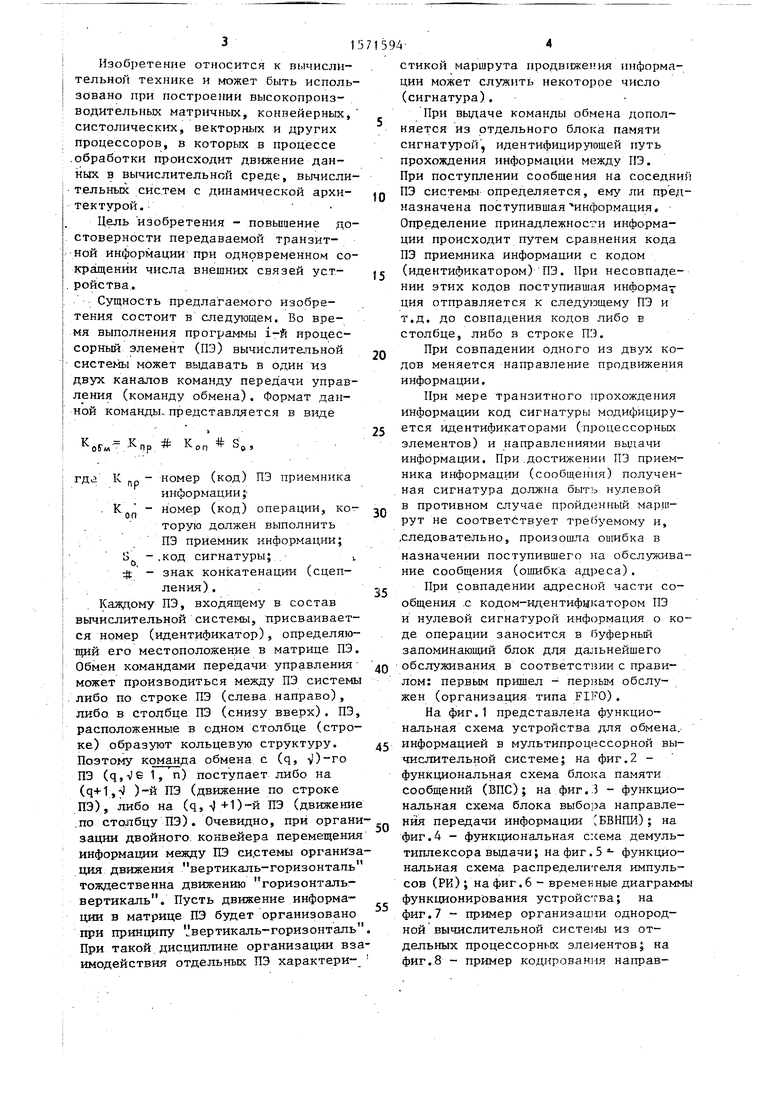

Устройство для обмена информацией в мультипроцессорной вычислительной системе (фиг.1) содержит первый 1, второй 2 и третий 3 блоки памяти сообщений типа первым пришел - первым обслужен, мультиплексор 4, блок памяти 5 константы, блок выбора направления передачи информации (БВНПИ) 6, блок памяти 7 сигнатур,буферный регистр 8 с первым - третьим полями: 8.1 - адресным полем, 8.2 - операционным полем и 8.3 - контрольным полем (полем сигнатуры), сумматор по модулю два 9, демультиплексор 10 выдачи, демультиплексор 11 синхронизации, распределитель 12 импульсов, счетчик 13, дешифратор 14, триггер 15 управления, коммутатор 16, блок элементов И 17, первый элемент И 18, второй элемент И 19, третий элемент И 20, триггер 21 контроля, элемент ИЛИ 22

На фиг.1 обозначены также первый- третий 23-25 входы устройства,первый третий 2b-28 информационные выходы устройства, первый 29 и второй 30 управляющие выходы.

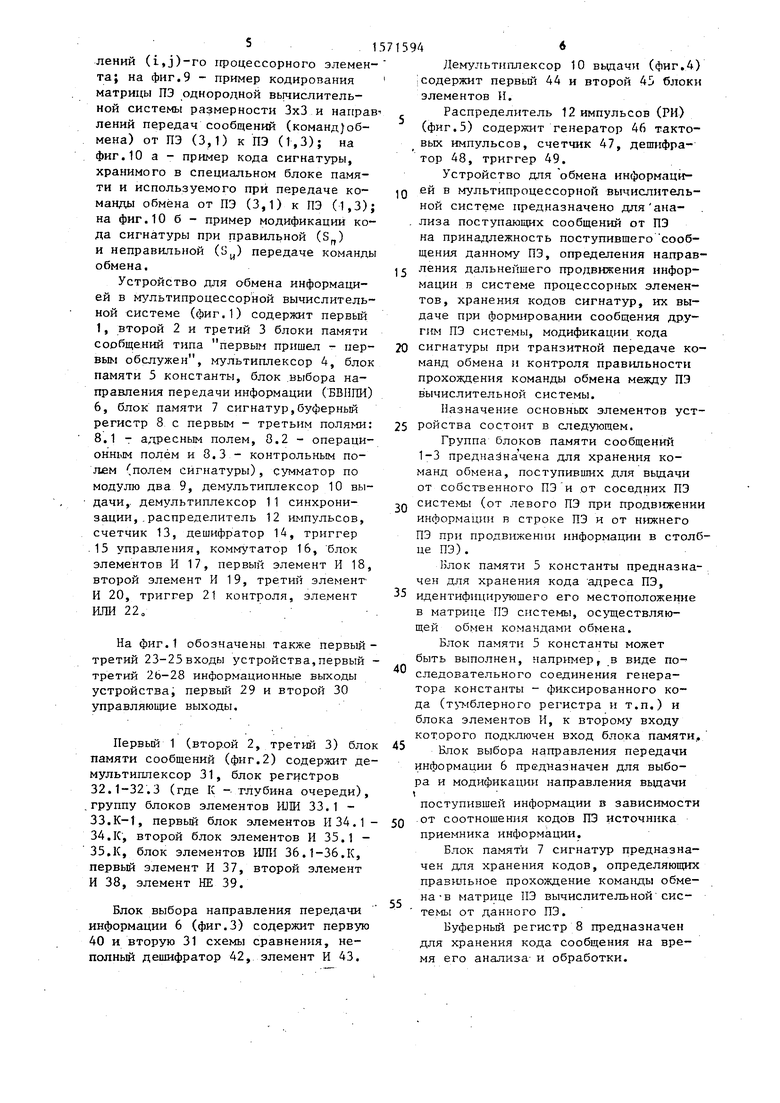

Первый 1 (второй 2, третий 3) блок памяти сообщений (фиг.2) содержит демультиплексор 31, блок регистров 32.1-32.3 (где К - глубина очереди), группу блоков элементов ИЛИ 33.1 - ЗЗ.К-1, первый блок элементов И 34.1 - 34.К, второй блок элементов И 35.1 - 35.К, блок элементов ИЛИ 36.1-36.К, первый элемент И 37, второй элемент И 38, элемент НЕ 39.

Блок выбора направления передачи информации 6 (фиг.З) содержит первую 40 и вторую 31 схемы сравнения, неполный дешифратор 42, элемент И 43.

594

Демультиплексор 10 выдачи (фиг.4) содержит первый 44 и второй 45 блоки элементов И.

Распределитель 12 импульсов (РИ) (фиг.5) содержит генератор 46 тактовых импульсов, счетчик 47, дешифратор 48, триггер 49.

Устройство для обмена информациQ ей в мультипроцессорной вычислительной системе предназначено для анализа поступающих сообщений от ПЭ на принадлежность поступившего сообщения данному ПЭ, определения направ5 ления дальнейшего продвижения информации в системе процессорных элементов, хранения кодов сигнатур, их выдаче при формировании сообщения другим ПЭ системы, модификации кода

0 сигнатуры при транзитной передаче команд обмена и контроля правильности прохождения команды обмена между ПЭ вычислительной системы.

Назначение основных элементов уст5 ройства состоит в следующем.

Группа блоков памяти сообщений 1-3 предназначена для хранения команд обмена, поступивших для выдачи от собственного ПЭ и от соседних ПЭ

Q системы (от левого ПЭ при продвижении информации в строке ПЭ и от нижнего ПЭ при продвижении информации в столбце ПЭ).

Блок памяти 5 константы предназначен для хранения кода адреса ПЭ,

5 идентифицируюшего его местоположение в матрице ПЭ системы, осуществляющей обмен командами обмена.

Блок памяти 5 константы может быть выполнен, например, в виде последовательного соединения генератора константы - фиксированного кода (тумблерного регистра и т.п.) и блока элементов И, к второму входу которого подключен вход блока памяти.

0

5

0

5

Блок выбора направления передачи информации 6 предназначен для выбора и модификации направления выдачи 1 поступившей информации в зависимости

от соотношения кодов ПЭ источника приемника информации.

Блок памяти 7 сигнатур предназначен для хранения кодов, определяющих правильное прохождение команды обмена -в матрице ПЭ вычислительной сис- темы от данного ПЭ.

Буферный регистр 8 предназначен для хранения кода сообщения на время его анализа и обработки.

71

Сумматор по модулю два 9 предназначен для модификации поступившего кода сигнатуры кодом адреса ПЭ и признаком направления дальнейшего продвижения команды обмена.

Демультиплексор 10 выдачи предназначен для коммутации команды обмена на один выходов 27 или 28 устройства К аналогичным ПЭ системы.

Распределитель 12 импульсов предназначен для синхронизации работы устройства.

Распределитель 12 импульсов формирует последовательность импульсов V. - с , Принцип действия рас

Г) л S Ь5 пределителя 12 поясняется временной

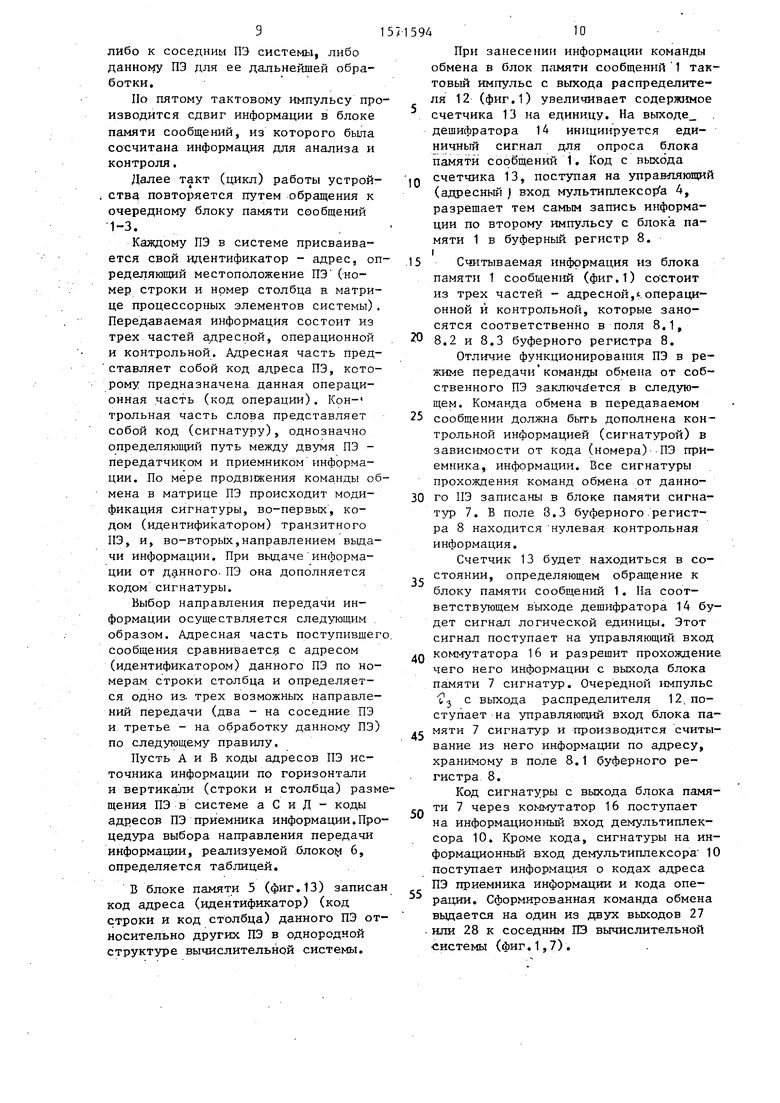

диаграммой на фиг.6. Посредством генератора 46, который включается единичным сигналом на входе, счетчика 47 с коэффициентом пересчета 5 формируется последовательность импульсов

Р 1 u 1 u з

и

г1 Триггер 49 устанавливается в единичное состояние импульсов .Ј и обнуля- ,ется задним фронтом импульса С, формируя удлиненный импульс 1}э , который является стробирующим сигналом опроса блоков 5 и 7,

Счетчик 13 совместно с дешифратором 14 служат для последовательного циклического опроса .блоков памяти сообщений 1-3.

Коммутатор 16 предназначен для коммутации либо начального кода сигнатуры (при передаче команды обмена от данного ПЭ), либо модифицированного кода сигнатуры (при передаче команды обмена транзитом).

Первый элемент И 18, триггер 21 контроля предназначены для формирования управляющего сигнала при ненулевом коде сигнатуры полученной при поступлении сообщения данному ПЭ.

Элемент И 20 и обусловленные им связи предназначены для формировани сигнала на обращение к блоку памяти 7 сигнатур при выдаче информации от данного ПЭ.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии.

т

Обмен информацией в вычислительной системе, состоящей из однотипных ПЭ (фиг.7), осуществляется в двух направлениях. По каждому из направлений блок памяти сообщений (БП принимает команды обмена (фиг.1).

8

0

5

0

5

0

5

0

5

0

5

Третий БПС предназначен рля хранения команд обмена от собственного ПЭ.

Команда обмена в зависимости от источника информации поступает на один из входов 23-25 устройства. Одновременно с командой обмена на этот вход поступает тактовый импульс.

Поступившая команда обмена заносится- в блок приема сообщения (БПС), HanpiiMep 1 (фиг.2). Так как блок регистров 32.1-32.К (где К - глубина очереди) находится в нулевом состоянии, то на выходах элементов И 34.1 - 34.К находятся сигналы логической единицы. Эти сигналы поступают на адресный вход демультиплексора 31 и разрешают тем самым запись поступившего сообщения в первьй регистр очереди 32,1 состояние этого регистра будет отличным от нулевого и тем самым будет подготовлен для записи очередного сообщения второй регистр 32.2. При записи информации в регистр 32.1 блока приема сообщения 1 на выходе элемента IIE 39 появляется сигнал логической единицы (фиг.2), который с выхода БПС 1 через элемент ИЛИ 22 (фиг.1) устанавливает триггер 15 управления в единичное состояние. Единичное состояние триггера 15 управления идентифицирует разрешение формирования на выходах распределителя импульсов (РИ) 12 импульсов для синхронизации работы устройства.

Синхронизация работы устройства происходит по импульсам, формируемым на первом - пятом выходах распределителя 12 (фиг.5) и представляют собой пять импульсных последовательностей (фиг.6). Такт (цикл) работы состоит из пяти фаз. Каждая фаза работы устройства начинается тактовым импульсом соответствующей импульсной последовательности.

По первому тактовому импульсу происходит обращение к соответствующему блоку памяти сообщений 1-3 путем увеличения содержимого счетчика 13 на единицу.

По второму тактовому импульсу производится запись сообщекия в буферный регистр 8.

По третьему тактовму импульсу происходит обращение к Елокам памяти сигнатур 5 и констант 7.

По четвертому тактовому импульсу производится выдача комгнды обмена

9

либо к соседним ПЭ системы, либо данному ПЭ для ее дальнейшей обработки.

По пятому тактовому импульсу производится сдвиг информации в блоке памяти сообщений, из которого была сосчитана информация для анализа и контроля.

Далее такт (цикл) работы устройства повторяется путем обращения к очередному блоку памяти сообщений 1-3.

Каждому ПЭ в системе присваивается свой идентификатор - адрес, определяющий местоположение ПЭ (номер строки и номер столбца в матрице процессорных элементов системы). Передаваемая информация состоит из трех частей адресной, операционной и контрольной. Адресная часть представляет собой код адреса ПЭ, которому предназначена данная операционная часть (код операции). Кон- трольная часть слова представляет собой код (сигнатуру), однозначно определяющий путь между двумя ПЭ - передатчиком и приемником информации. По мере продвижения команды обмена в матрице ПЭ происходит модификация сигнатуры, во-первых, кодом (идентификатором) транзитного ИЗ, и, во-вторых,направлением выдачи информации. При выдаче информации от данного ПЭ она дополняется кодом сигнатуры.

Выбор направления передачи информации осуществляется следующим образом. Адресная часть поступившег сообщения сравнивается с адресом (идентификатором) данного ПЭ по номерам строки столбца и определяется одно из трех возможных направлений передачи (два - на соседние ПЭ и третье - на обработку данному ПЭ) по следующему правилу.

Пусть А и В коды адресов ПЭ источника информации по горизонтали и вертикали (строки и столбца) размщения ПЭ в системе а С и Д - коды адресов ПЭ приемника информации.Процедура выбора направления передачи информации, реализуемой блоком 6, определяется таблицей.

В блоке памяти 5 (фиг.13) записан код адреса (идентификатор) (код строки и код столбца) данного ПЭ относительно других ПЭ в однородной структуре вычислительной системы.

594Ю

При занесении информации команды обмена в блок памяти сообщений 1 тактовый импульс с выхода распределителя 12 (фиг.1) увеличивает содержимое счетчика 13 на единицу. На выходе дешифратора 14 инициируется единичный сигнал для опроса блока памяти сообщений 1. Код с выхода

0 счетчика 13, поступая на управляющий (адресный ) вход мультиплексора 4, разрешает тем самым запись информации по второму импульсу с блока памяти 1 в буферный регистр 8.

5 Считываемая информация из блока памяти 1 сообщений (фиг.1) состоит из трех частей - адресной, операционной и контрольной, которые заносятся соответственно в поля 8.1,

0 8.2 и 8.3 буферного регистра 8.

Отличие функционирования ПЭ в режиме передачи команды обмена от собственного ПЭ заключается в следующем. Команда обмена в передаваемом

5 сообщении должна быть дополнена контрольной информацией (сигнатурой) в зависимости от кода (номера) ПЭ приемника, информации. Все сигнатуры прохождения команд обмена от данно0 го ПЭ записаны в блоке памяти сигнатур 7. В поле 8.3 буферного регистра 8 находится нулевая контрольная информация.

Счетчик 13 будет находиться в со, стоянии, определяющем обращение к блоку памяти сообщений 1. На соответствующем выходе дешифратора 14 будет сигнал логической единицы. Этот сигнал поступает на управляющий вход

д коммутатора 16 и разрешит прохождение чего него информации с выхода блока памяти 7 сигнатур. Очередной импульс 3 с выхода распределителя 12 поступает на управляющий вход блока пас мяти 7 сигнатур и производится считывание из него информации по адресу, хранимому в поле 8.1 буферного регистра 8.

Код сигнатуры с выхода блока памяти 7 через коммутатор 16 поступает на информационный вход демультиплек- сора 10. Кроме кода, сигнатуры на информационный вход демультиплексора 10 поступает информация о кодах адреса ПЭ приемника информации и кода операции. Сформированная команда обмена выдается на один из двух выходов 27 или 28 к соседним ГО вычислительной системы (фиг.1,7).

0

11

Выбор направления передачи команды обмена от д анного ПЭ осуществля- тся блоком выбора направления передачи информации (БВНПИ) 6 (фиг.1,3). На основе сравнения двух кодов адре- tcoB ПЭ на схемах сравнения 40 и 41 г(фиг.З) БВИГШ Ь на выходе неполного дешифратора 42 образуется в соответствии с таблицей формируется признак

1, если требуется передать tf информацию вверх,

О, если требуется передать информацию вправо.

Сформированный признак направления выдачи информации с выхода БВНПИ 6 (фиг.1) поступает на адресные (управляющие) входы демультиплексоров 10 и 11. Очередной импульс . с выхода распределителя 12 через демуль- типлексор 11 поступает на соответствующий выход для синхронизации записи сообщения в блок памяти сообщения 1 (3) соседнего ПЭ. Далее ПЭ функционирует аналогично описанному.

При обработке команды обмена от соседних ПЭ, происходит обращение к соответствующему блоку памяти сообщений 2 или 3, Через мультиплексор 4 команда обмена заносится в буферный регистр 3. При этом в поле 8.3 находится код сигнатуры.

При передаче информации транзистом код сигнатуры S при прохождении ПЭ будет промодифицирован, во-первых, кодом адреса идентификатором) ПЭ и, во-вторых, кодом направления выдачи информации. Модификация кода сигнатуры, поступающего с выхода поля 8.3 буферного регистра 8, происходит на блоке свертки по модулю два 9, поступающим признаком направления передачи направления у с выхода БВНПИ 6 и кодом адреса ПЭ с выхода блока памяти 5. Полученная сигнатура с выхода блока элементов суммы по модулю два 9 через коммутатор 16 поступает для дальнейшей ее передачи совместно с адресной и операционной частями команды обмена к соседнему ПЭ. Далее устройство функционирует аналогично описанному. По мере продвижения команды обмена в матрице ПЭ системы к ПЗ приемнику информации будет происходить модификация сигнатуры.

При совпадении кодов адресов ПЭ приемника информации с адресной частью команды обмена на выходах ров20

25

157159412

но первой 40 и второй 41 схем сравнения блока 6 (фиг.З) формируются сигналы логической единицы. На выхо- , де элемента И 43 будет также сигнал логической единицы. Этот сигнал с

выхода блока 6 выбора направления передачи информации (фиг.З) поступает на управляющий вход-блока элементов

10 И 17 и разрешает тем самыч при поступлении импульса с выхода распределителя 12 прохождение оаерационной части (кода операции) с выхода поля 8.2 буферного регистра 8 на выход

5 26 для последующей записи, например в буферный запоминающий б ток для дальнейшей обработки данных ПЭ.

Кроме того, управляющий сигнал с выхода блока выбора направления передачи информации 6 постуиает на управляющий вход синхронизации триггера 21 поворота. На входз элемента И 18 с нулевых выходов поля 8.3 буферного регистра 8 поступает код сигнатуры. Отсутствие ошибки в прохождении команды обмена в матрице ПЭ системы будет при S О0..00, в противном случае маршрут прохождения сообщения будет отличным от за30 планированного. При нулевой сигнатуре S 00...0 на выходе элемента И 18 будет сигнал логической единицы, идентифицирующий правильность прохождения команды обмена, а следо35 вательно, и правильность принадлежности поступившего на обслуживание запроса. Этот сигнал поступает на инверсный S-вход триггера 21 контроля и не изменяет его состояния.

40 При S Ј 00...0 сигнал логического нуля с выхода элемента И 18 (фиг,1) установит триггер 21 контроля в единичное состояние. На прямом выходе триггера 21 контроля будет сигнал

45 логической единицы, поступающий на выход 30 устройства.

После обслуживания поступивших на обработку в блоки памяти 1-3 сообщений (фиг„1,2) на выходе элемен50 тов НЕ 39 будет сигнал логического нуля. Этот сигнал на выходе элемента ИЛИ 22 образует сигнал логического нуля, который поступает на инверсный вход элемента И 19 и разрешает тем самым при выдаче последней команды обмена на соседний ПЭ или данному ПЭ импульсом с выхода распределителя 12 обнуление триггера 15 управления. На этом анализ и контроль,

55

13

1

поступивших команд обмена завершается.

Пусть имеется матрица процессорных элементов (ПЭ) системы размерности М 3x3 (фиг.9). Пусть необходимо передать команду обмена от ПЭ с номером (3.1) к ПЭ с номером (1.3). В этом случае из блока памяти сигнатур будет сосчитан контрольный код S 011001 (фиг.Юа). При правильном прохождении информации оставшаяся сигнатура S S n 000000 (фиг.106). Допустим, что при поступлении информации в ПЭ с номером (2.2 (фиг.9) адресная часть будет изменена (001011) -S- (010011). В этом случа произойдет изменение прохождения информации и сообщение будет передано на ПЭ с номером (2,3) вместо ПЭ с номером (1,3). Без реализации средст контроля прохождения сообщение будет принято к исполнению и в системе произойдет искажение обрабатываемой информации.

В предлагаемом устройстве оставшаяся сигнатура S ...O 001001 и будет сформирован признак неверного прохождения информации. По данному признаку возможно обращение, например, к диагностической процедуре.

Р Формула изобретения

Устройство для обмена информацией в мультипроцессорной вычислительной системе,содержащее три блока памяти сообщений, мультиплексор, буферный регистр, блок памяти константы, счетчик, дешифратор, демульти- плексор выдачи, блок выбора направления, передачи информации, блок элементов И, распределитель импульсов, коммутатор, демультиплексор синхронизации, триггер контроля, триггер управления, три элемента И и элемент ИЛИ, причем информационные входы первого, второго и третьего блоков памяти сообщений является первым вторым и третьим информационными входами устройства соответственно, первые управляющие входы первого, второго и третьего блоков памяти сообщений являются первым, вторым и третьим управляющими входами уст- ройства соответственно, вторые управляющие входы первого, второго и третьего блоков памяти сообщений соединены с первым выходом распредели

10

15

159414

теля импульсовj третьи управляющие входы первого,второго и третьего блоков памяти сообщений соединены с первым, вторым и третьим выходами

5 дешифратора соответственно, информационные выходы первого, второго и третьего блоков памяти сообщений соединены с первым, вторым и третьим информационными входами мультиплексора соответственно, управляющие выходы первого, второго и третьего блоков памяти сообщений соединены с первым, вторым и третьим входами элемента ИЛИ соответственно, выход эле- . мента ИЛИ соединен с входом установки единицы триггера управления и инверсным входом первого элемента И, выход которого подключен к входу установ2Q ки поля триггера управления, выход которого соединен с входом распределителя импульсов, второй выход которого соединен с управляющим входом буферного регистра, информационный

25 вход которого подключен к выходу

мультиплексора, третий выход распределителя импульсов соединен с прямым входом первого элемента И и информационным входом демультиштексора синхронизации, четвертый выход распределителя импульсов соединен со счетным входом счетчика,выход которого соединен с управляющим входом мультиплексора и входом дешифратора,первый выход которого соединен с уп35 равляющим входом коммутатора и с первым входом второго элемента И, второй вход которого соединен с пятым выходом распределителя импульсов и управляющим входом блока памяти

40 константы, выход которого подключен к первому входу блока выбора направления передачи информации, первый выход которого является первым управляющим выходом устройства и соединен

45 с первым входом блока элементов И, управляющим входом триггера контроля и первым управляющим входом демуль- типлексора синхронизации, второй управляющий вход которого соединен с

50 вторым выходом блока выбора направления передачи информации и управляющим входом демультиплексора выдачи, первый и второй выходы которого являются первым и вторым информацион55 ными выходами устройства соответственно, выход блока элементов И является третьим информационным выходом устройства, первый, второй и третий выходы демультиплексора синхронизации

30

15

являются первым, вторым и третьим управляющими выходами устройства со- ртветственно, первый и второй информационные входы демультиплексора выдачи соединены с первым и вторым выходами буферного регистра соответственно, третий информационный вход демулйтиплексора выдачи соеди- яен с выходом коммутатора, первый и Второй выходы буферного регистра соединены с вторым входом блока выбора направления передачи информации и вторым входом блока элементов И соответственно, третий выход буферного регистра соединен с входами третьего элемента И, выход которого подключен к информационному входу триггера контроля, выход которого является вторым управляющим выходом устройства, отличающееся тем, что, с целью повышения достоверности передаваемой транзитной информации при одновременном сохранении числа внешних связей, устройство содержит блок памяти сигнатур и сумматор по модулю два, причем выход второго .элемента И соединен с управляющим входом блока памяти сигнатур, адресный вход которого соеди157159416

нен с первым выходом буферного регистра, выход блока памяти сигнатур соединен с первым входом коммутатора г второй вход которого соединен с выходом сумматора по модулю два, первый вход которого соединен с выходом блока памяти константы, первый выход блока выбора направления JQ передачи информации и третий выход буферного регистра соединены с вторым и третьим входами сумматора по модулю два соответственно.

15

20

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных матричных, конвейерных, систолических, векторных и других процессоров, в которых в процессе обработки происходит движение данных в вычислительной среде. Цель изобретения - повышение достоверности передаваемой транзитной информации при одновременном сопряжении числа внешних связей устройства. Для достижения указанной цели в устройство введены блок 7 памяти сигнатур и сумматор 9 по модулю два. Модификация сигнатур при передаче данных между процессорными элементами с контролем результата при получении сообщения процессором-приемником, а также использование дисциплины передач вверх - вправо позволяет реализовать указанные преимущества. 10 ил.

Фиг 2

46

i

Ј

«о

1

Ј

т

42

4J

д

ФигЗ

Фиг 4

+Ъ

т

s з с к

4§

ч -Ч

«e o ts. .-. -. см-.с.-. « f t vr « w

-цч .

Vj I

(

к

(

o

s

в

X

ъ

±L -C2

Ј

-

000(1

fU)

001(2)

Т

Фиг. 8

s

© 001001 ffl

S- 000 000® ®OQ0001®001010® 000001®001011 01100i

и

Sn Q1100i ©000000® 010 001® 000 000 ® .

(booiooi&oooooi&ooiowQooo 001® 001011 000 ooo

SH 011001 ©000000® 010 001® 000 001® ©010010® 000001 ©010011 001001 000 000

Фиг. 10

© 001001 ffl

001011 01

| Шкаф с приспособлением для уборки в него кровати | 1924 |

|

SU1179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1985 |

|

SU1312597A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-08-11—Подача