.1

Изобретение относится к накоплению информации, в частности к аналоговы|« запоминающим устройствам, и может быть использовано в различных устройствах автоматики, вычислительной и измерительной техники для регистрации быстропротекающих процессов.

Известно аналоговое запоминающее устройство, содержащее три усилителя, три ключа, источник сигналов, три резистора и конденсатор 1.

Данное устройство, несмотря на простоту конструктивного выполнения, имеет ограниченную область применения, так как служит для запоминания только одного значения входного сигнала.

Известно также устройство запоминания и извлечения аналоговых значений напряжения,,содержащее два устройства управления, запоминающие конденсаторы, входные и выходные ключи, входную и выходную общие щины 2.

Недостатком устройства является сложность конструктивного выполнения.

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, содержащее накопительные конденсаторы, входные и выходные переключатели, схему слежения сигналов, два блока управления, сумматоры {3 Однако это устройство обладает большой сложностью конструктивного выполнения, так как содержит два блока управления, отдельные входные и выходные переключатели, а также сложную схему коррекции.

Цель изобретения - повыщение точности устройства и его. упрощение.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее основной накопитель, выходы которого соединены с первым входом первого усилителя, блок управления, входы которого являются входами устройства, первый выход блока управления подключен к первым входам первых ключей, вторые входы которых соединены с щиной нулевого потенциала, выходы первых ключей соединены со входами основного накопителя, выход первого уси. лителя подключен к выходу устройства и через первый пассивный элемент, например первый резистор, к первому входу второго ключа, второй вход которого соединен со вторым выходом блока управления, выход второго ключа соединен через второй пассивный элемент, например второй резистор, с выходом второго усилителя, первый вход которого соединен с инфор Мационным входом устройства через третий пассивный элемент, например третий резистор, второй вход второго усилителя подключен к шине нулевого потенциала, первый вход второго усилителя со-здинен с первым входом второго ключа, введены третий ключ, дополнительный накопительный элемент, например конденсатор, и третий усилитель, вход кото- д рого- соединен с выходом первого усилителя, выход третьего усилителя подключен к одной из обкладок конденсатора, другая обкладка которого соединена с первым входом первого усилителя и с выходом третьего ключа, первый вход которого соединен с 15 выходом второго усилителя, второй вход третьего ключа соединен с третьим выходом блока управления.

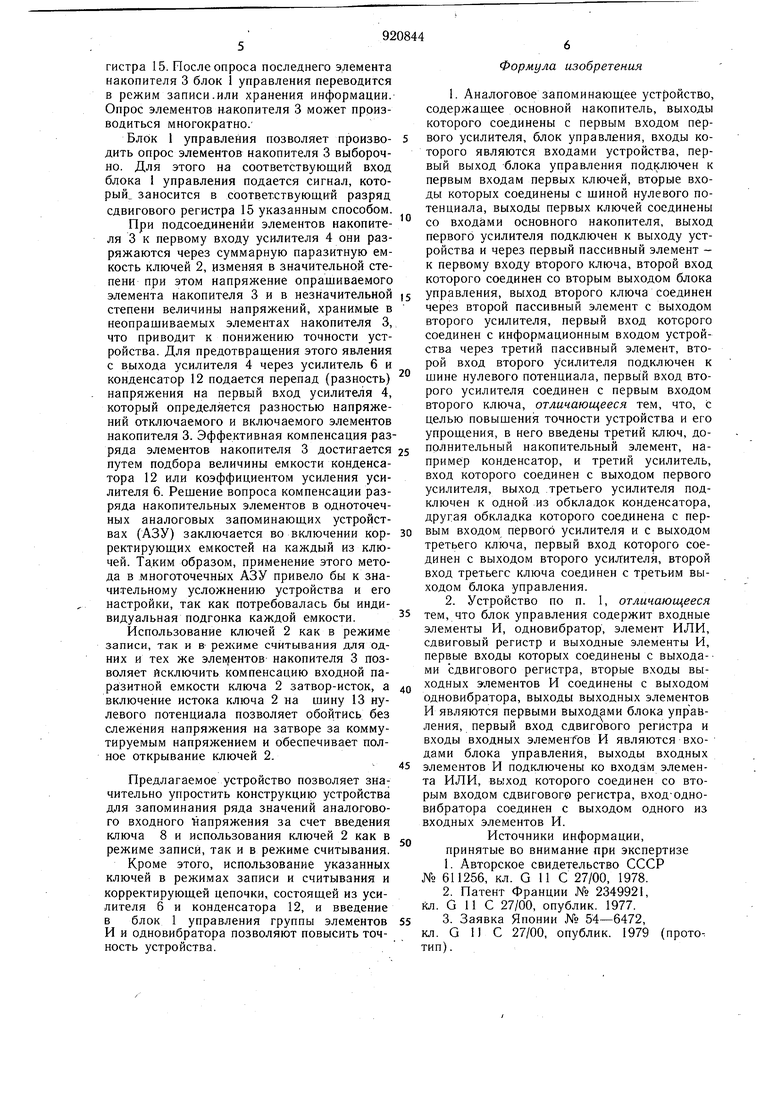

Кроме того, блок управления содержит входные элементы И, одновибратор, элемент jo ИЛИ, сдвиговый регистор и выходные элементы И, первые входы которых соединены с выходами сдвигового регистра, вторые входы выходных элементов И соединены с выходом одновибратора, выходы выходных элементов И являются первыми выходами 2 блока управления, первый вход сдвигового регистра и входы входных элементов И являются входами блока управления, выходы выходных элементов И подключены ко входам элемента ИЛИ, выход которого соединен со вторым входом сдвигового регистра, вход одновибратора соединен с вьгходом одного из входных элементов И.

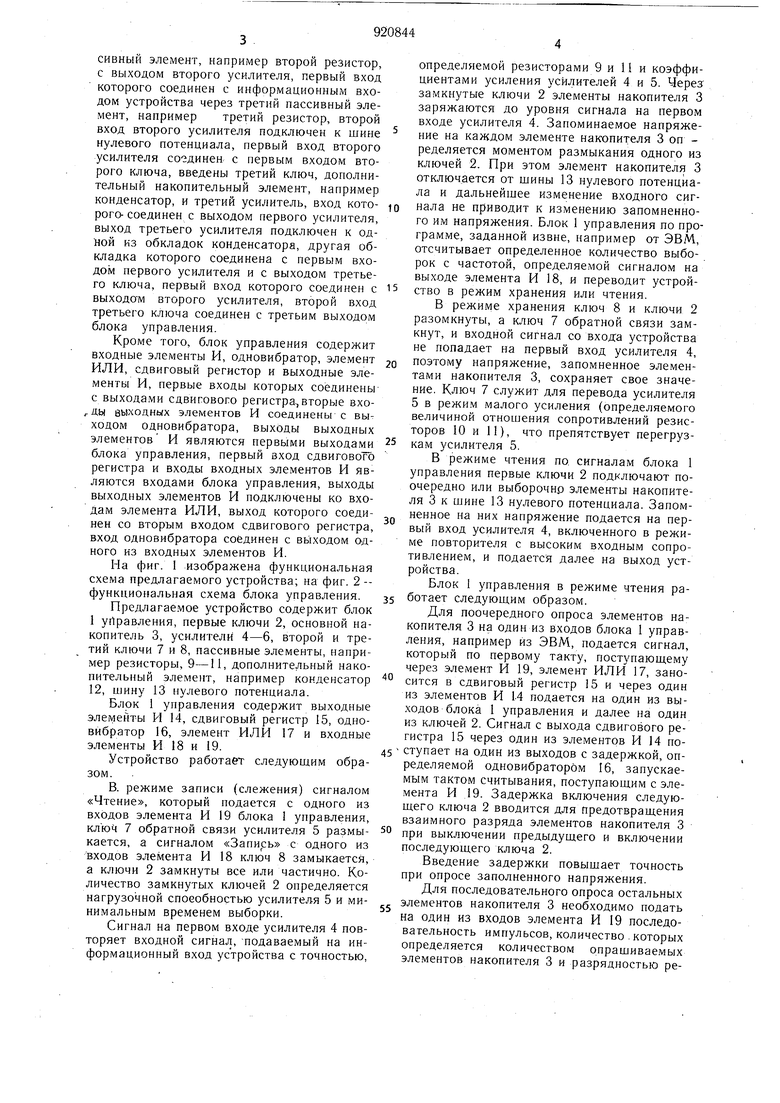

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 -функциональная схема блока управления. 35

Предлагае.мое устройство содержит блок 1 уЛравления, первые ключи 2, основной накопитель 3, усилители 4-6, второй и третий ключи 7 и 8, пассивные элементы, например резисторы, 9-11, дополнительный накопительный элемент, например конденсатор 12, шину 13 нулевого потенциала.

Блок 1 управления содержит выходные элементы И 14, сдвиговый регистр 15, одновибратор 16, элемент ИЛИ 17 и входные элементы И 18 и 19.45

Устройство работает следуюшим образом.

В. режиме записи (слежения) сигналом «Чтение, который подается с одного из входов элемента И 19 блока 1 управления, клю 7 обратной связи усилителя 5 размы- 50 кается, а сигналом «Запись с одного из входов элемента И 18 ключ 8 замыкается, а ключи 2 замкнуты все или частично. Количество замкнутых ключей 2 определяется нагрузочной способностью усилителя 5 и минимальным временем выборки.

Сигнал на первом входе усилителя 4 повторяет входной сигнал, -подаваемый на информационный вход устройства с точностью.

определяемой резисторами 9 и 11 и коэффициентами усиления усилителей 4 и 5. Через замкнутые ключи 2 элементы накопителя 3 заряжаются до уровня сигнала на первом входе усилителя 4. Запоминаемое напряжение на каждом элементе накопителя 3 оп ределяется моментом размыкания одного из ключей 2. При этом элемент накопителя 3 отключается от шины 13 нулевого потенциала и дальнейшее изменение входного сигнала не приводит к изменению запомненного им напряжения. Блок 1 управления по программе, заданной извне, например от ЭВМ, отсчитывает определенное количество выборок с частотой, определяемой сигналом на выходе элемента И 18, и переводит устройство в режим хранения или чтения.

В режиме хранения ключ 8 и ключи 2 разомкнуты, а ключ 7 обратной связи замкнут, и входной сигнал со входа устройства не попадает на первый вход усилителя 4, поэтому напряжение, запомненное элементами накопителя 3, сохраняет свое значение. Ключ 7 служит для перевода усилителя 5 в режим малого усиления (определяемого величиной отношения сопротивлений резисторов 10 и 11), что препятствует перегрузкам усилителя 5.

В режиме чтения по. сигналам блока 1 управления первые ключи 2 подключают поочередно или выборочн.0 элементы накопителя 3 к шине 13 нулевого потенциала. Запомненное на них напряжение подается на первый вход усилителя 4, включенного в режиме повторителя с высоким входным сопротивлением, и подается далее на выход устройства.

Блок 1 управ.лення в режиме чтения работает следуюшим образом.

Для поочередного опроса элементов накопителя 3 на один из входов блока 1 управления, например из ЭВМ, подается сигнал, который по первому такту, поступаюш.ему через элемент И 19, элемент ИЛИ 17, заносится в сдвиговый регистр 15 и через один из элементов И 14 подается на один из выходов блока 1 управления и далее на один из ключей 2. Сигнал с выхода сдвигового регистра 15 через один из элементов И 14 поступает на один из выходов с задержкой, определяемой одновибратором 16, запускаемым тактом считывания, поступаюшим с элемента И .19. Задержка включения следуюшего ключа 2 вводится для предотБраш.ения взаимного разряда элементов накопителя 3 при выключении предыдущего и включении последующего ключа 2.

Введение задержки повышает точность при опросе заполненного напряжения.

Для последовательного опроса остальных элементов накопителя 3 необходимо подать на один из входов элемента И 19 последовательность импульсов, количество.которых определяется количеством опрашиваемых элементов накопителя 3 и разрядностью регистра 15. После опроса последнего элемента накопителя 3 блок 1 управления переводится в режим записи.или хранения информации. Опрос элементов накопителя 3 может производиться многократно.

БлЬк 1 управления позволяет производить опрос элементов накопителя 3 выборочно. Для этого на соответствующий вход блока 1 управления подается сигнал, который заносится в соответствующей разряд сдвигового регистра 15 указанным способом.

При подсоединении элементов накопителя 3 к первому входу усилителя 4 они разряжаются через суммарную паразитную емкость ключей 2, изменяя в значительной степени при этом напряжение опращиваемого элемента накопителя 3 и в незначительной степени величины напряжений, хранимые в неопращиваемых элементах накопителя 3, что приводит к понижению точности устройства. Для предотвращения этого явления с выхода усилителя 4 через усилитель 6 и конденсатор 12 подается перепад (разность) напряжения на первый вход усилителя 4, который определяется разностью напряжений отключаемого и включаемого элементов накопителя 3. Эффективная компенсация разряда элементов накопителя 3 достигается путем подбора величины емкости конденсатора 12 или коэффициентом усиления усилителя 6. Рещение вопроса компенсации разряда накопительных элементов в одноточечных аналоговых запоминающих устройствах (АЗУ) заключается во включении корректирующих емкостей на каждый из ключей. Та.ким образом, применение этого метода в многоточечнь х АЗУ привело бы к значительному усложнению устройства и его настройки, так как потребовалась бы индивидуальная подгонка каждой емкости.

Использование ключей 2 как в режиме записи, так и в режиме считывания для одних и тех же элементов накопителя 3 позволяет исключить компенсацию входной паразитной емкости ключа 2 затвор-исток, а включение истока ключа 2 на щину 13 нулевого потенциала позволяет обойтись без слежения напряжения на затворе за коммутируемым напряжением и обеспечивает полное открывание ключей 2.

Предлагаемое устройство позволяет зна чительно упростить конструкцию устройства для запоминания ряда значений аналогового входного Напряжения за счет введения ключа 8 и использования ключей 2 как в режиме записи, так и в режиме считывания.

Кроме этого, использование указанных ключей в режимах записи и считывания и корректирующей цепочки, состоящей из усилителя 6 и конденсатора 12, и введение в блок 1 управления группы элементов И и одновибратора позволяют повысить точность устройства.

Формула изобретения

1. Аналоговое запоминающее устройство, содержащее основной накопитель, выходы которого соединены с первым входом первого усилителя, блок управления, входы которого являются входами устройства, первый выход блока управления подключен к первым входам первых ключей, вторые входы которых соединены с щиной нулевого потенциала, выходы первых ключей соединены

0 со входами основного накопителя, выход первого усилителя подключен к выходу устройства и через первый пассивный элемент к первому входу второго ключа, второй вход которого соединен со вторым выходом блока управления, выход второго ключа соединен

5 через второй пассивный элемент с выходом второго усилителя, первый вход которого соединен с информационным входом устройства через третий пассивный элемент, второй вход второго усилителя подключен к

0 шине нулевого потенциала, первый вход второго усилителя соединен с первым входом второго ключа, отличающееся тем, что, с целью повыщения точности устройства и его упрощения, в него введены третий ключ, дополнительный накопительный элемент, например конденсатор, и третий усилитель, вход которого соединен с выходом первого усилителя, выход третьего усилителя подключен к одной из обкладок конденсатора, другая обкладка которого соединена с первым входом первого усилителя и с выходом

0 третьего ключа, первый вход которого соединен с выходом второго усилителя, второй вход третьего ключа соединен с третьим выходом блока управления.

2. Устройство по п. 1, отличающееся

5 тем, что блок управления содержит входные элементы И, одновибратор, элемент ИЛИ, сдвиговый регистр и выходные элементы И, первые входы которых соединены с выходами сдвигового регистра, вторые входы выходных э-лементов И соединены с выходом

0 одновибратора, выходы выходных элементов И являются первыми выходами блока управления, первый вход сдвигового регистра и входы входных элеменГов И являются входами блока управления, выходы входных

5 элементов И подключены ко входам элемента ИЛИ, выход которого соединен со вторым входом сдвигового регистра, вход-одновибратора соединен с выходом одного из входных элементов И.

Источники информации,

0

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 611256, кл. G 11 С 27/00, 1978.

2.Патент Франции № 2349921, кл. G И С 27/00, опублик. 1977.

3.Заявка Японии № 54-6472,

5

кл. G 11 С 27/00, опублик. 1979 (прото. тип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| Устройство для кодирования электрических сигналов | 1987 |

|

SU1501269A1 |

| Устройство для контроля и регулировки положения очесывающего барабана льноуборочного комбайна | 1990 |

|

SU1821066A1 |

| Устройство для автоматического измерения шумов | 1987 |

|

SU1479896A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Демодулятор сигналов с фазово-импульсной модуляцией | 1984 |

|

SU1267605A1 |

| УСТРОЙСТВО СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079882C1 |

| Устройство контроля электромагнитных параметров гибкого магнитного диска | 1988 |

|

SU1578627A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| МНОГОЭЛЕМЕНТНЫЙ ФОТОДАТЧИК И УСТРОЙСТВО РЕГИСТРАЦИИ ИЗОБРАЖЕНИЯ | 2009 |

|

RU2417436C1 |

Авторы

Даты

1982-04-15—Публикация

1980-08-08—Подача