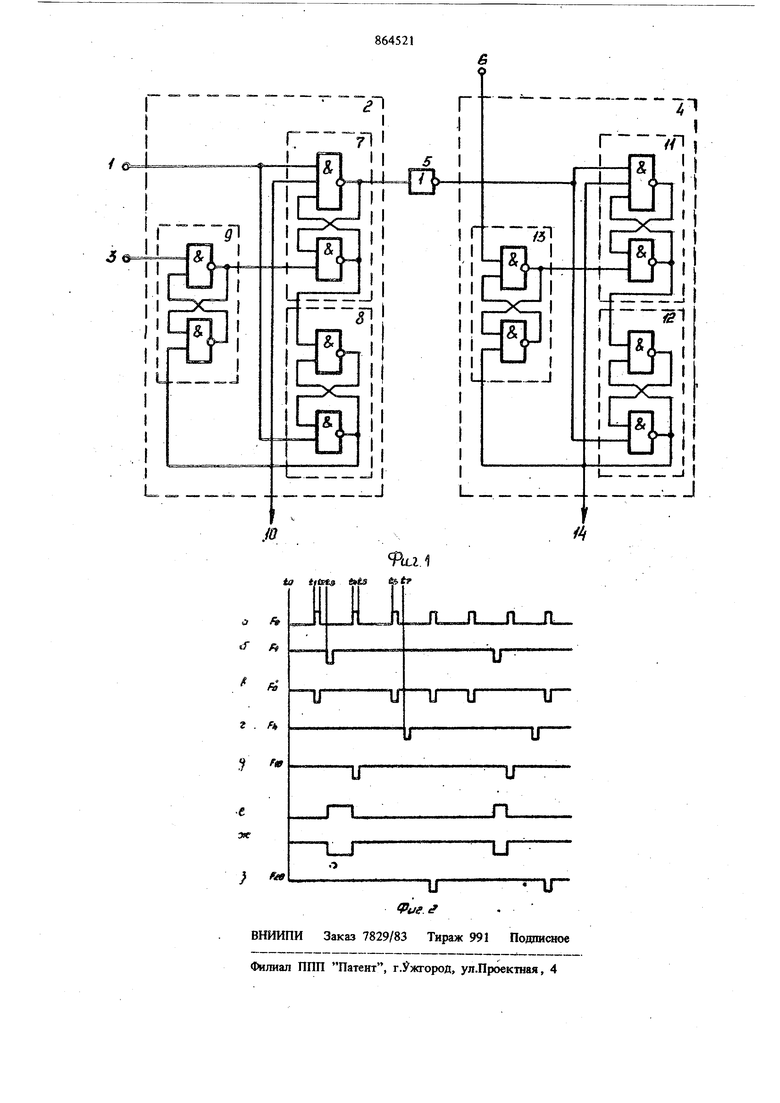

Изобретение отиосится к импульсной технике и может быть использовано в устройствах автоматики к вычислительной техники, в частности в электронных устройствах различного назначения, где требуется разнесение по фазе двух импульсных последовательностей и синхронизация их третьей, частота которой превышает синхронизируемые частоты более, чем в два раза. Известно устройство для синхронизации импульсных последовательностей, содержащее триггер-датчик опорной частоты и два делительных блока, состоящие из RS-триггеров памяти, элементов И-НЕ и входных RS-трип-еров, единичные входы которых соединены с шинами синхронизируемых последовательностей, а едншпные выходы - с первымн входами элементе И-НЕ, вторые входы которых соединены с выходами т{жггера-датчика. На выходе устройства имеют место две импульсные последовательностя фронты которых засинхронизированы импульсами опорных раздвинутых частот, никогда не совпадающих по времени 1. Недостатком данного устройства является низкая точность работы, заключающаяся в том,; что задержка импульсов синхронизированных последовательностей относительно синхронизируемых импульсов составляет 2-4 периода И1орной частоты. Наиболее близким техническим решением к изобретению является устройство дЛя синхронизации импульсных последовательностей, содержащее инвертор и триггер-датчик, включающий в себя первый, второй и третий RS-триггеры на потенциальных злементах , причем R-вход второго RS-триггера соединен с инверсным выходом третьего RS-триггера, а инверсный выход - с S-входом первого RS-триггера, инверсный выход: которого подключен к S-входу третьего RS-триггера н к первому S-входу второго RS-трнггера, второй S-вход которого соединен с R-ВХОДОМ первого RS-триггера и шиной опорной частоты, а прямой выход - со входом инвертора. Кроме того, R-вход третьего RS-триггера подключен к прямому выходу второго RS-трштера, выход инвертора сое|и нен с первым входом первого делнтельного блока и со вторым входом второго делительного блока, а инBCjKHb вход первого RS-триггера через второй инвертор подключен ко второму входу первого делительного блока и к первому входу второго делительного блока, причем третьи входы обоих делительных блоков являются входами синхро1дазируемых последовательностей, а вы- . ходы - выходами синх{юнизированных последовательностей. Преимущество данного устройства состоит в том, что у него выше точность работы, так как импульсы синхронизированных частот сдвинуты относительно синхронизируемых на 1-3 периода опорной частоты 2. Недостатком этого устройства является то, что точность его работы не обеспечивает задерж ки импульсов синхронизированных последовател ностей от соответствующих синхронизируемых импульсов, не превышающей величины одного периода опорной частоты. Кроме того, данное устройство является достаточно сложным. Цель изобретения - повышение точности син хронизации при упрощении устройства. Указанная цель достиагется тем, что в устрой ство для синхронизации импульсных последовательностей, содержащее инвертор и триггер-датчик, состоящий из трех RS-триггеров, причем R-вход первого RS-триггера соединен с прямым выходом второго RS-триггера, R-вход которого подключен к инверсному выходу третьего RS-триггера и первому S-входу первого RS-три гера, второй S-вход которого соединен с шиной так товых импульсов и R-входом третьего Я&триггер S-вход которого подключен к инверсному выходу первого RS-триггера, прямой выход которого соединен со входом инвертора, дополнительно введен такой же триггер-датчик, второй S-вход первого RS-триггера которого соединен с выходом инвертора, а R-входы вторых RS-три геров и инверсные выходь третьих RS-триггеров основного н дополнительного т|жггеров-дат чиков подключены соответственно к входным и выходаым шинам устройства. На фиг. 1 приведена принципиальная схема устройства; на фиг, 2 - временные диаграммы Устройство для синхронизшош ИАШульсных последовательностей содержит входную шину 1, подключенную к первому входу триггера-датчика 2, входную шину 3, подключенную ко второ му входу триггера-датчика 2, триггер-датчик 4, первый вход которого через инвертор S соединен с первым ВЫХОДОМтриггера-датчика 2, входную шину 6, подключенную ко второму входу триггера-датчика 4, RS-триггеры 7-9, входящие в состав триггера-датчика 2, второй выход которого подключен к выходной шине 10, RS-триггеры 11-13, входящие в состав триг гера-датчика 4, выход которого подключен к выходной шине 14. . Устройство работает следующим образом. На вход 1 устройства, являющийся первым входом триггера-датчика 2, подается опорная частота FQ (фиг. 2 а). На вход 3, являющийся вторым входом триггера-датчика 2 поступают отрицательные импульсы первой сцнхронизируемой последовательности, например частоты F (фиг. 2 б). На первый вход триггера-датчика 4 подается в качестве опорной частоты последовательность импульсов FO (фиг. 2 в), поступающая через инвертор 5 с первого выхода триггера-датчика 2. На вход 6 устройства, являющийся вторым входом триггера-датчика 4, поступают отрицательные импульсы второй синхронизируемой последовательности, например частоты Ft (фиг. 2 г) . В исходном состоянин (время to, фиг. 2) на входной ншне 1 устройства имеется низкий потенциал, позтому на прямом выходе RS-триггера 7 и инверсном выходе RS-триггера 8, а следовательно, и инверсном входе RS-триггера 9 и выходной шине 10 устройства (фиг. 2 д) высокие поте1щиалы. На входной шине 3 устройства в исходном состоянии имеется высокий потенциал. Таким образом, на обоих входах RSтрмггера 9 в момент времени to имеется высокий потенциал, а следовательно, RS-триггер 9 находится в одном из двух возможных состояний. Допустим он находится в состоянии, когда на его прямом выходе (фиг. 2 е) имеется низкий потенциал. В зтом случае на инверсном выходе RS-триггера 7 (фиг, 2 дс), а следовательно, и на S-входе RS-триггера 8 высокий потенциал. Положительный импульс, поступающий в момент времени ti на входную шину I устройства, инвертируется в RS-триггере 7 и поступа- ет на вход инвертора 5. При этом никаких изменений в состоянин устройства не происходит, и после окончания импульса в момент времени t2 устройство находится в первоначальном исходном состоянии. При поступлении отрицательного импульса частоты F| на входную шину 5 устройсша.в момент Bj eMeim tj срабатывает RS-триггер 9 и на его инверсном выходе появляется высокий потенциал. Это второе из двух возможных состояний RS-триггера 9, соответствующее моменту запоминания информации о пришедшем импульсе синхррнизируе й частоты FJ. При этом на инверсном выходе RS-трнгге 7 потенциал станет низким. Такое состояние устройства, останется и после окончания импульса частоты FI и сохранится до прихода следующего положительного импульса частоты FQ на входную шину 1 устройства в момент времени tt. Этот импульс не проходит через RS-триггер 7, так как его S-вход блокирован низким потенциалом с его инверсного выхода. На инверсном выходе RS-триггера 8 появится ннзкнй потенциал, блокирующий S-вход RS-триггера 7 и возвращающий RS-триггер 9 в первоначальное исходное состоянне. При этом на единичном выходе RS-триггера 9 появится низкнй потенциал, а на ннверсйом -выходе RS-триггера 7 - высокий потенциал. После окончания нмпульса опор-, 58 ной частоты FO в момент времени 1$ на инверс ном выходе RS-трнггера 7 сохраняется высокий потенциал, к, .следовательно, устройство возвращается в первоначальное исходное состояние, соответствующее времени to- Положительный импульс опорной частоты FO , П|ЖХОДЯЩКЙ в момент времени t, инвертируется в RS-триггере 7 и поступает на вход инвертора 5. Таким образом, каждый отрицательный импульс синхронизируемой частоты FI, поступающий на входную ишну 3 устройства устанавливает триггер-датчик 2 в состояние, при котором на его второй выход (выходная шина 10 устройства) проходит следукшдий за ним во времени импульс опорной частоты FO подаваемой на i входную щину 1 устройства. Следовательно, на выходной шине 10 устройства последовательность импульсов FIO имеет частоту, равную частоте синхронизируемой последователь ности FI и фазу импульсов опорной частоты F На первый вход триггера-датчика 4, соединен ного с первым S-входом RS-триггера 11 и R-входом RS-триггера 12, nocTjnnaeT с выхода инвертора S последовательность импульсов FQ, представляющая собой опорную частоту FQ с вырезанными импульсами синхро1шзированной частоты FIO. На второй вход триггера-датчика 4 «..являюишмся В-входом RS-триггера 13 и выход шиной 6 устройства, подаются отрицател1гные импульсы второй синхронизируемой последюательности Fj (момент времени t, фкг. 2) Так же, как в триггере-датчике 2, каждый отрицательный импульс частоты fj устанавливает триггер-датчик 4 в состояние, при котором на выходной цшне 14 устройства (фиг. 2 з) проходит следуюишй за ним по времени импульс частоты FO. На выходной Шине 14 устройства последовательность импульсов Fjo имеет частоту, равную частоте синхронизируемой последовательности Fj, и фазу импульсов частоты FO, а следовательио, и FO. Таким образом, данное ycTpdiство осуществляет синхронизацню двух последовательностей FI и FJ третьей FO, при этом синхронизированные последовательности Fjo и FJO никогда не совпадают по времени. Кроме того, задержка синхронизированных импульсов частоты FIO н FJO относительно соответствующих импульсов синхронизируемых частот FI и FJ всегда меньше периода опорной частоты, что характеризует более высокую точность работы данного устрюйства по сравнению с известными. Формула изобретения Устройство для синхронизации импульсных последовательностей, содержащее инвертор и триггер-датчик, состоящий нз трех RS-триггеров, причем R-вход первого RS-триггера соединен с )1м выходом второго RS-триггера, R-вход которого подключен к инверсному выходу третьего RS-триггера и первому S-входу первого RS-триггера, второй S-вход которого соединен с цшной тактовых импульсов и R-входом третьего RS-трнггера, S-вход которого подключен к инверсному выходу первого RS-триггера, прямой выход которого соединен со входом инвертора, отличающееся тем, что, с целью повышения точности синхронизации, в иего дополнительно введен такой же триггер-дагшк, второй S-вход первого RiS-триггера которого соединен с выходом инвертора, . а R-входы вторых RS-триггеров и инверсные выходы третьих RS-триггеров основного и дополнительного триггеров-датчиков подключены соответственно к входным и выходным шинам устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 321931, кл. Н 03 К 5/00, 1971. 2.Авторское свидетельство СССР № 611294, кл. Н 03 К 5/00, 1975. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсных последовательностей | 1981 |

|

SU961120A1 |

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| Устройство для порогового контроля частоты | 1979 |

|

SU864163A1 |

| Устройство для синхронизации импульсных последовательностей | 1975 |

|

SU611294A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1582342A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Вычитающее устройство | 1975 |

|

SU594506A1 |

| Устройство для задержки импульсов | 1980 |

|

SU921067A1 |

Авторы

Даты

1981-09-15—Публикация

1979-12-17—Подача