тии вход каждого 1-го элемента И первой группы с первого по (п-1)-ый соединен с выходом -го элемента И второй группы и с первым входом 1-го элемента И третьей группы, первый вход (п-1)-го элемента И третьей группы соединен с нулевым выходом п-го разряда первого регистра и с третьим входом (n-l)-ro элемента И первой группы, первый вход п-го элемента И третьей группы соединен с выходом п-го элемента И первой группы и с инверсным входом п.-го элемента ЗАПРЕТ, выход каждого i-го элемента И первой группы, кроме п-го, соединен со вторым входом 1-го элемента И третьей группы и с нулевым входом 1-го элемента ЗАПРЕТ, выход каждого 1-го элемента запрета, кроме {п-1)-го, соединен с нулевым входом t-ro разряда первого регистра, с единичным входом (fч-1) -го элемента ЗАПРЕТ и с третьим входом (1+1)-го элемента И третьей группы, выход (n-l)-ro элемента ЗАПРЕТ соединен со вторым входом пто элемента И третьей группы, с нулевым входом (п-1)-го разряда первого регистра°и с единичным, входом п-го элемента ЗАПРЕТ г тактовый BXO/J устройства соединен с третьим входом первого элемента И третьей группы и с единичным входом первого элемента ЗАПРЕТ, первый W .второй входы каждого i-ro элемента И второй группы, кроме {п-2)-го, соединены соответственно с выходом (1ч-1)-го элемента И второй группы и с нулевым выходом (i4t)-ro разряда первого регистра, первый и второй входы (п-2)-го элемента И второй группь соединены с ну выходами (n-l)-ro и п-го разрядов первого регистра соответственно, n-fo элемента ЗАПРЕТ соединен с нулевым входом п-го разряда первого регистра, выход кйждого го элемента И третьей группы соединен с единимным входом соответствующего разряда первого регистра.

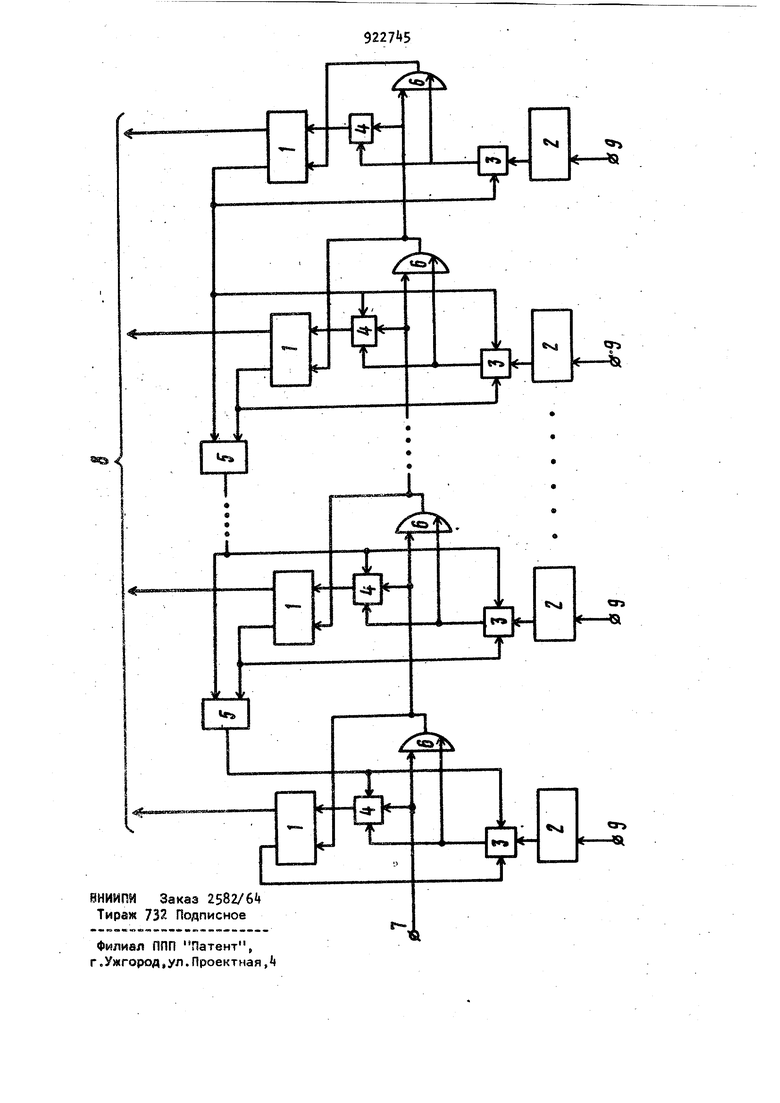

На чертеже представлена блок-.схема устройства.

Устройство содержит триггеры 1 и 2 первого и второго регистров, элементы И 3-5 и элементы 6 ЗАПРЕТ, тактовый вход 7 устройства, группу информационных выходов 8 устройства, группу кодовых входов 9 устройства.

Устройство для последовательного выделения единиц из двоичного кода работает следующим образом.

В исходном состоянии триггеры 1 и 2 находятся в нуле, в результате чего элементы И 5 всех ячеек открыты, а на одном из входов элементов И 3 и 4 присутствует разрешакйций потенциал. Кроме того, сигналами с нулевых выходов триггеров 1 открываются по второму входу элементы И 3 всех ячеек.

При выделении единиц из двоичного кода значения разрядов исходного кода подаются на соответствующие входы 9 устройства и запоминаются триггерами 2.

Если значение разряда исходного кода равно единице, то сигнал с единичного выхода триггера 2 соответствующей ячейки через открытый элемент И 3 поступает на запрещающий вход элемента ЗАПРЕТ 6 данной ячейки, одновременно открывая элемент И ,

При подаче на вход 7,устройства , тактового импульса он пройдет последовательно через все элементы 6, на нулевых входах которых нули с выходов триггеров 2, до ближайшего элемента 6, на нулевом входе которого единица , и установит через открытый элемент И триггер Т данного разряда в едиi ничное состояние. На выходе 8 устройства появится сигнал, соответствующий первой выделенной единице, при этом на всех других выходах устройства сигнал будет отсутствовать. Снятие сигнала с нулевого выхода триггера 1 данного разряда заблокирует все элементы ИЗ и 5 предшествующих разрядов, а также элемент И 3 данного разряда, в результате чего откроется элемент 6 и закроется элемент И 4 данного разряда.

Следующий тактовый импульс, пройдя через открывшийся элемент 6, перет бросит триггер 1 данного разряда снова в нулевое состояние, одновременно устанавливая в единичное состояние триггер 1 соответствующего разряда, равного единице. Произойдет выде ление след тзцей единицы из исходного кода и так далее.

После вь(деления последней единицы все тригге(1 1 устройства установятся в нуль, и устройство будет подготовлено к работе без подачи на него каких-либо установочных сигналов.

Применение изобретения позволяет повысить надежность устройства.

Формула изобретения

Устройство для последовательного выделения единиц из двоичного кода , содержащее два регистра и первую группу из п элементов И, о т личающееся тем, что, с ие: лью повышения надежности,, устройство содержит группу из п элементов ЗАПРЕТ, вторую группу из (п-2) элементов И и третью группу из п элементов И (п - число разрядов входного кода), причем группа единичных выходов первого регистра является группой информационных выходов устройства, группа единичных входов вто рого регистра является группой кодовых входов устройства, единичный выход каждого i-ro разряда второго регистра соединен с первым входом 1-го элемента И первой группы, второй вход которого соединен с нулевым выходом i-ro разряда первого регистра, третий .вход каждого -го элемента И первой группы с первого по (п-1)-ый соединен с выходом 1-го элемента И второй группы и с первым входом Г-го элемента И третьей группы, первый вход {п-1)-го элемента И третьей группы соединен с нулевым выходом п-го разряда первого регистpa и с третьим входом (n-l)-ro элемента И первой группы, первый вход п-го элемента- И третьей группы соединен с выходом п-го элемента И первой группы и с инверсным входом п-го элемента ЗАПРЕТ, выход каждого 5-го элемента И первой группы, кроме п-го соединен со вторым входом 1-го элемента И третьей группы и с нулевым входом 1-го элемента ЗАПРЕТ выход каждого 1-го элемента ЗАПРЕТ, кроме (n-l)-ro, соединен с нулевым входом J-ro разряда первого регистра, с единичным входом (п+1)-го элемента ЗАПРЕТ и с третьим входом ((+1)-го элемента И третьей группы, выход {п-1)-го элемента ЗАПРЕТ соединен со вторым входом п-го элемента И третьей группы, с нулевым входом (п-1)-го разряда первого регистра и с единичным входом п-го элемента ЗАПРЕТ, тактовый вход устройства соединен с третьим входом первого элемента И третьей группы и с единичным входом первого элемента ЗАПРЕТ, первый и второй входы каждого 1-го элемента И второй группы, кроме (п-2)-го, соединены соответственно с выходом (|+1)-го элемента И второй группы и с нулевым выходом (1+1)-го разряда первого регистра, первый и второй входы (л-2)-го элемента И второй группы соединены с нулевыми выходами (n-l)-ro, и п-го разрядов первого регистра соответственно, выход п-го элемента ЗАПРЕТ соединен с нулевым входом п-го разряда первого регистра, выход каждог 1-го элемента И третьей группы соеднен с единичным входом соответствующего разряда первого регистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 278215, кл. G Об F 5/02, 19692.Авторское свидетельство СССР № , кл. G Об F 7/06, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перебора перестановок | 1987 |

|

SU1418733A1 |

| Устройство для исследования графов | 1985 |

|

SU1290345A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1982 |

|

SU1070555A1 |

| Устройство для перебора сочетаний | 1986 |

|

SU1370655A1 |

| Устройство для сравнения весов кодов | 1979 |

|

SU798810A1 |

| Устройство циклического приоритета | 1990 |

|

SU1716516A1 |

| Устройство для нормализации избыточных кодов | 1984 |

|

SU1256009A1 |

| Устройство для суммирования @ -разрядных последовательно поступающих чисел | 1982 |

|

SU1075260A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Преобразователь двоичного кода в число-импульсный код | 1980 |

|

SU943704A1 |

Авторы

Даты

1982-04-23—Публикация

1980-09-26—Подача