Изобретение относится к вычисительной технике и может бытьисользовано в устройствах статистиеской обработки информации.

Известно устройствоДЛЯ суммироания m п-разрялных чисел, содеращее п су;ммирующих блоков, каждый з которых содержит L многовходовых дноразрядных сумматоров с сохранением переносов TlJ.

Недостаток устройства - сложность и ограниченные функциональные возможности: при изменении хотя бы одного из m чисел массива необходимо вводить и суммировать весь ассив m чисел, что затрудняет использование данного устройства для статистической обработки непрерывно-поступающей последовательности чисел.

Наиболее близким по технической сущности к изобретению является параллельный накапливающий сумматор, содержащий в каждом разряде триггер, элемент И и элемент ИЛИ, выход которого подключен к счетному входу триггера соответствующего разряда, а вход подключен к выходу элемента И этого же разряда и единично1 1У выходу триггера предьодуще-. го разряда сумматора, первые входы элементов И подключены к информационным входам устройства, тактовый вход устройства подключен к вторым входам элементов И четных разрядов сумматора непосредственно, а нечетных разрядов - через элемент задержки 2 З

Недостатком этого сумматора являются ограниченные функциональные возможности, так как этот сумматор вычисляет сумму всех поступивших на его входы чисел и не обеспечивает вычисление суммы m последних поступивших чисел.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения вычисления суммы последних m чисел из поступающей последовательности.

Цель достигается тем, что в устройство для суммирования m п-разрядных последовательно поступающих чисел,содержащее группу из п счетных триггеров, первую группу из п эле-, ментов И, группу из п элементов ИЛИ и первый элемент задержки, причем первые входы J-x элементов И первой группы, где ,4,...,n соединены между собой и с входом первого элемента задержки, выход которого соединен с первыми входами {j-l)-x элементов И первой группы, выход i-ro элемента И первой группы, где ,2,...,п, соединен с первым входом i-ro элемента ИЛИ группы, выход которого соединен со

четным входом i-ro счетного триг- ера,единичный выход которого явлif e.т , ся 1-м выходом устройства и соединен с вторым входом (1-«-1)-го элемента ИЛИ группы, введены группа из

п т-разрядных сдвигающих регистров, вторая группа из п элементов И, первый и второй элементы И, элемент запрета, элемент ИЛИ, второй, третий и четвертый элементы задержки,

причем i-й информационный вход устройства соединен с первым входом 1-го элемента И второй группы, выход которого соединен с информационным входом i-ro сдвигающего регистра и третьим входом i-ro элемента ИЛИ группы, инверсный выход i-ro сдвигающего регистра соединен с вторым входомi-ro элемента И первой группы и с i-м входом первого

элемента И, выход которого соединен с первым входом второго элемента И и с инверсным входом элемента запрети, выход которого соединен с первым входом первого элемента ИЛИ

группы и входом второго элемента задержки, выход которого соединен с входом первого элемента задержки, выход которого соединен с входом третьего элемента задержки, выход которого соединен с первым входом

элемента ИЛИ, выход которого соединен с входом четвертого элемента задержки, вторыми входами J-x элементов И второй группы и управляющими входами J-X сдвигающих регист- ров, тактовый вход устройства соединен с прямым входом элемента запрета я вторым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, а выход

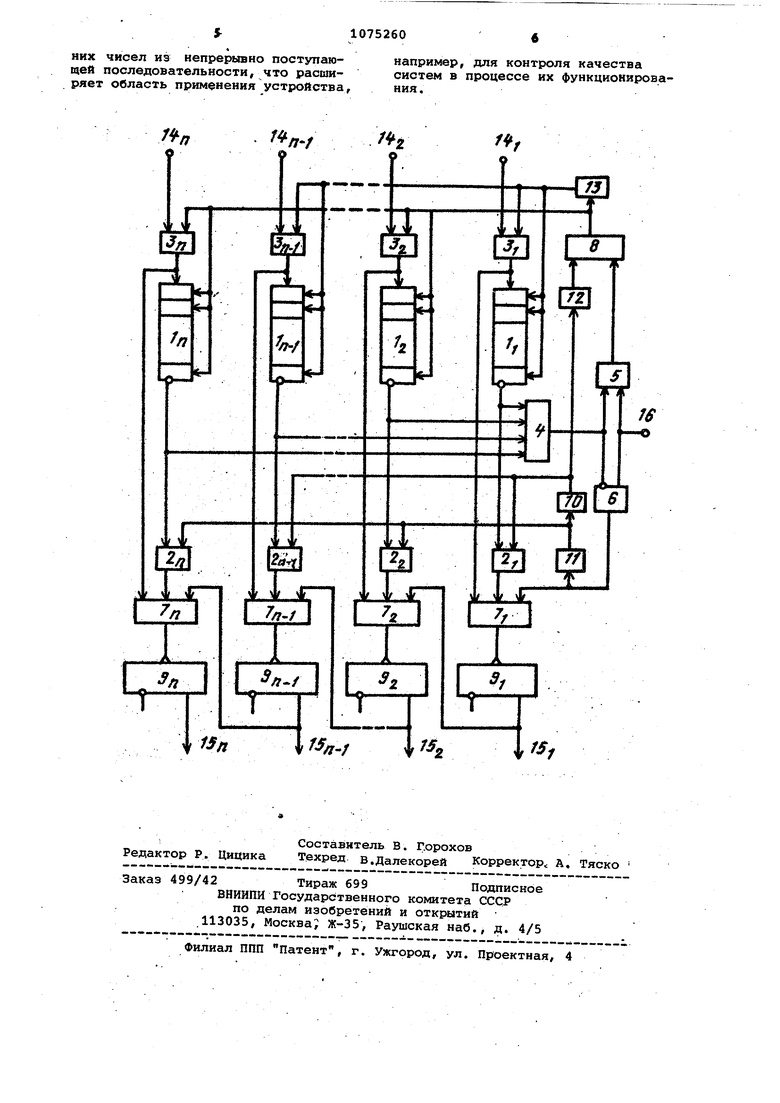

четвертого элемента задержки соединен с вторыми входами {j-l)-x элементов И второй группы и управляющшли входами ( J -1) -X сдвигающих реги стров. ; На чертеже показана схема устройства.

Устройство содержит сдвигающие регистры , группы элементов И и , элементы И.4 и 5, элемент запрета б, группу элементов

ИЛИ , элемент ИЛИ 8, группу счетных триггеров , элементы задержки 10-13, информационные входы li-14 t выходы разрядов суммы, тактовый вход .16.

Устройство работает следующим

образом.

В исходном состоянии в регистрах записаны нули, следовательно, по одному входу открыт элемент И 5, триггеры 9i-9f,- в нулевом состоянии. Первый импульс, посту пающий на тактовый вход 16 через элементы И 5 и ИЛИ 8, поступает на вторые входы элементов И ,, четных -разрядов, производит сдвиг в

регистрах l2-ln четных разрядов и запись четных разрядов первого чис ла в эти регистры, а также через элементы ИЛИ 72-7 - в триггеры 9А-9.Д. Этот же импульс через элемент задержки 13 поступает на первые входы элементов И 3.-3 нечетных разрядов, производит сдвиг в регистрах ,нечетных разрядов и запись нечетных разрядов пер вого числа в эти регистры, а также через элементы ИДИ 7 -7й. - в тригг ры 9 -fti-y .Следовательно, в первых разрядах регистров 1) -1л и в триггерах 9, -9п,. записывается первое чи ло из непрерывно поступающей последовательности чисел. Второй тактовый импульс через элементы И 5 и ИЛИ 8 поступает на вторые входы элементов И , чет ных разрядов, производит сдвиг в р гистрах 1:„-1. и запись четных разрядов второго числа в эти регистры а также обеспечивает их -поступление через элементы ИЛИ 72-7, на счетные входы триггеров , четных разрядов. При поступлении четны разрядов второго числа происходит их сложение с четными разрядами пер вого числа, записанного в триггерах 9j-9 следующим образом: при поступ лении О. состояние триггера не мёняется, а при поступлении 1 состо яние триггера изменяется на противо положное, причем при переходе триггера из единичного в нулевое состоя ние на единичном выходе этого триггера появляется сигнал переноса в следующий разряд, который суммируется со значением этого разряда, и т.д. Затем второй тактовый импульс через элем1ент задержки 13 поступает на вторые входы элементов И нечетных разрядов, производит сдвиг 5 регистрах 1;,-1,ечетных разряIдов и запись нечетных разрядов второго числа в эти регистры, а также обеспечивает их поступление через элементы ИЛИ . нечетных разрядов на счетные входы триггеров .нечетных- разрядов и сложение с нечетными разрядами числа, записанного в триггерах 9 -9f,(no аналогии со сложением четных разрядов Например, пусть в триггерах 9v,-9 записано число 0111, а поступает число ООН. Тогда после первого сложения (четных разрядов) в триггерах записывается число 1001, а после второго сложения (нечетных разрядов) - сумма 1010. При поступлении тактовых импульсов с третьего по устройство работает аналогично. После m-ro тактового импульса в триггерах записывается сумма m чисел, а в регистрах li,-l. - вся последовательность поступивших m чисел, причем в k-x разрядах регистров 1-,-, где ,2,...,m, записывается (m-k+l)-e число поступившей последовательности чисел. Если первое число из последовательности нуль, то на инверсных выходах всех региртров единицы, элемент И 4 открыт я (т+1)-й такт работы устройства аналогичен предьщущим тактам. Если «е первое число не нуль, то элемент И 4 закрывается и открываете элемент запрета 6. (т-«-1)-й тактовый импульс через элемент запрета 6, элемент ИЛИ 7 поступает на счетный вход триггера 9, т.е. к младшему разряду суммы, находящейся в триггерах , прибавляется единица. Этот же импульс через элемент задержки 11 поступает на вторые входы элементов И f четных разрядов и обеспечивает поступление четных разрядов первого числа в обратном коде через элементы ИЛИ на счетные входы триггеров 92-9„ и их сложение с суммой, находящейся в триггерах . Далее этот же импульс через элемент задержки 10 поступает на первые входы элементов И нечетных, разрядов и обеспечивает поступление нечетных разрядов первого числа в обратном коде через элементы ИЛИ 7t|-7 на.счетные входы триггеров .нечетных разрядов и их сложение с , находящейся в триггерах . Далее этот же сигнал через элемент задержки 12 поступает на первый вход элеменгга ИЛИ 8 и производится запись следующего числа в регистры 1 -i -1 , и сложение с суммой, находящейся в. триггерах , четных разрядов (т+1)-го Числа, а также их поступление через элементы ИЛИ 72-7, на счетные входы триггеров 92-9п , и т.д. как описано. Таким образом, при поступлении (т)-го тактового импульса из суммы m чисел вычитается .Е-е из поступающих Чисел (путем сложения суммы m чисел с числом, дополнительным к f-му) и прибавляется вновь поступившее (m+f)-e число. Следовательно, в триггерах ,, всегда находится сумма m последних чисел из поступающей последовательности. Технико-экономический эффект зобретения заключается в расширеии функциональных возможностей стройство обеспечивает нахождение yt4Mtt т последних чисел без неободимости постоянного пересчета уммы всех т. чисел. Это йрзволяет перативно вычислять сумму m последних чисел из иепрерьшно поступающей последовательности, что расширяет область применения устройства.

например, для контроля качества систем в процессе их функционирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования @ -разрядных последовательно поступающих чисел | 1990 |

|

SU1764065A1 |

| Устройство для перебора перестановок | 1986 |

|

SU1397933A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для сглаживания сигналов | 1987 |

|

SU1437877A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Вероятностный (1-п)полюсник | 1973 |

|

SU443378A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ m п-РАЗРЯДНЫХ ПОСЛЕДОВАТЕЛЬНО ПОСТУПАКХЦИХ ЧИСЕЛ, содержащее группу из п счетных триггеров, первую группу из п элементов И, группу на п элементов ИЛИ.и первый элемент задержки, причем первые входы элементов И первой группы, где j 2,4,..., п, соединены между собой и с входом первого элемента задержки, выход которого соединен с пер- выми входами {j-l)-x элементов И первой группы, выход i-ro элемента И первой группы, где ,2,..., п, соединен с первым входом 1-го элемента ИЛИ группы, выход которого соединен с счетным входом i-ro счетного триггера, единичный выход которого является i-M выходом устрой- ства и соединен с вторым входом (i+l)-ro элемента ИЛИ группы,о т ли чающееся тем, что, с целью расширения функциональных возможностей путем обеспечения вычисления суммы последних m чисел из поступающей последрвательности, ; оно содержит группу из п т-разрядЙНХ сдвигающих регистров, вторую группу из п элементов И, первый-и второй элементы И, элемент запрета, элемент ИЛИ, второй, третий i чет; вертый элементы задержки, причем i-й информационный вход устройства соединен с первым входом i-ro элемента И второй группы, выход кото;рого соединен с информационным входом i-ro сдвигающего регистра и третьим входом i-ro элемента ИЛИ группы, инверсный выход 1-го сдвига,ющего регистра соединен с вторым входом i-ro элемента И первой группы и с i-M входом первого элемента И, выход которого соединен с первым входом второго элемента И и с инверсным входом ЗЛемента запрета, выход § которого соединен с первым входом первого элемента ИЛИ группы и входом второго элемента задержки, выход которого соединен с входом первого элемента задержки, выход которого соединен с входом третьего элемента задержки, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом четвертого элемента задержки, вторыми входг1ми J-X элементов И вторбй груп пы и управляющими входами j-x сдвигаСП ((яцих регистров, тактовый вход устройto ства соединен с прямым входом элемента запрета и вторым входом .второго а ;элемента И, выход которого соединен с вторым входбм элемента ИЛИ, а выход четвертого элемента задержки соединен с вторыми входами (J-1)-Х элементов И второй группы и управляющими входами {J-1)-X сдвигающих регистров.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для суммирования N @ -разрядных чисел | 1979 |

|

SU920707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Параллельный накапливающий сумматор | 1975 |

|

SU581470A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-13—Подача