(5) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ЧИСЛО-ИМПУЛЬСНЫЙ код

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

1

Изобретение относится к автомати ке и цифpoвo 1 вычислительной технике и может быть -использовано при построении преобразователей в устройствах приема и передачи дискретных сообщений, а также в измерительных устройствах.

Известен преобразователь двоичного кода в последовательность импульсов, содержащий регистр, элементы И, одновибраторы, дифференцирующие цепочки, общий элемент ИЛИ, выходные элементы ИЛИ, триггеры памяти и управления 1.

Недостатками известного преобразователя являются его сложность и большой объем аппаратуры.

Наиболее близким к изобретению по технической сущности и схемному построению является преобразователь двоичного кода в число-импугьсный код, содержащий счетчик, каждый разряд которого имеет основной и вспомогательный триггеры, триггер режима

и элемент И. Кроме того, известный преобразователь содержит триггер запрета 2.

Недостатками данного преобразователя являются сложность управления с устройством и невысокая надежность что обусловлено большим количеством внешних связей.

Цель изобретения - упрощение уст(о ройства и повышение его надежности.

Поставленная цель достигается тем, что преобразователь двоичного кода в число-импульсный код, содержащий счетчик, каждый разряд которого имеет основной и вспомогательный триггеры, триггер режима, элемент И, первый вход которого подключен к единичному выходу триггера режима, второй вход соединен с тактовым входом преобразователя, с тактовым входом триггера режима и с тактовым входом основного триггера нулевого разряда счетчика, выход элемента И является вьГходом преобразователя, нулевой и единичный выходы основного триггера 1-го разряда счетчика {i 0-п), где п - число разрядов входного кода, соединены соответственно с первым единичным и нулевым входами, вспомогательного триггера i-ro разряда счетчика, единичный и нулевой входы основного триггера i-ro разряДа соединены соответственно с единичным и нулевым, выходами вспомогательного три|- гера i-ro разряда, единичный выход основного триггера п-го разряда счечика соединен с управляющим входом триггера режима, дополнительно содержит два входных элемента И-НЕ, группу из п элементов 2И-ИЛИ и элемент И-НЕ обнуления., выход которого соединен с входами сброса основных триггеров с 1-го по п-ый разряды, с входом начальной установки единиц основного триггера нулевого разряда входом начальной установки нуля вспо могательного триггера нулевого разряда, входами начальной установки единицы вспомогательных триггеров с 1-го по п-ый разряды и входом сброса триггера режима, нулевой выход которого соединен с первыми входами элементов 2И-ИЛИ группы и первыми входами первого и второго входных элементов И-НЕ, вторые вход которых являются информационными входами преобразователя, а выходы соединены соответственно с вторым нулевым и вторым единичным входами вспомогательного триггера нулевого разряда, тактовый вход которого соединен с тактовым входом преобразователя и с вторыми входами элементов 2И-ИЛИ группы, третьи входы которых соединены с единичным выходом триггера режима, четвертый вход j-ro (j 1 - n) элемента 2И-ИЛИ гру пы соединен, с единичным выходом основного триггера (j-l)-ro разряда, с вторым единичным входом вспомогательного триггера j-ro разряда и с j-ым входом элемента И-НЕ обнуления, а выход j-ro элемента 2И-ИЛИ группы соединен с тактовыми входами основного и вспомогательного три| геров j-ro разряда, нулевой выход основного- триггера {j-)-ro разряда соединен с вторым нулевым входом вспомогательного триггера j-ro разряда.

В предложенном преобразователе вспомогательный триггер содержит

первый и второй элементы И-ИЛИ-НЕ, выходы которых являются единичным и нулевым выходами вспомогательного триггера и соединены соответственно с первыми входами второго и первого элементов И-ИЛИ-НЕ, вторые входы которых объединены и являются тактовым входом вспомогательного триггера, третьи входы первого и второго элементов И-ИЛИ-НЕ являются соответственно первыми единичным и нулевым входами вспомогательного триггера, четвертые входы первого и второго элементов И-ИЛИ-НЕ являются вторыми

единичным и нулевым входами вспомогательного триггера, пятый и шестой входы первого элемента И-ИЛИ-НЕ объе-г динены и являются входом начальной установки вспомогательного триггера.

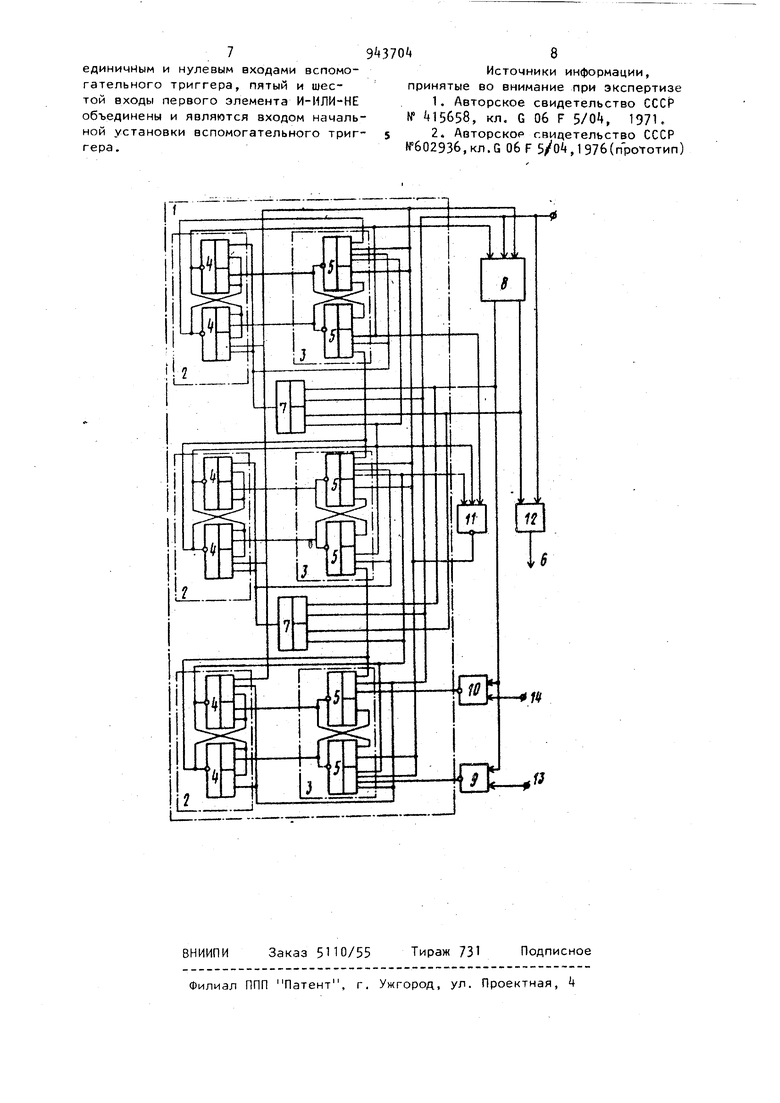

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь двоичного кода в число-импульсный код содержит счетчик 1, каждый разряд которого состоит из основного триггера 2 и вспомогательного триггера 3. Основной и вспомогательный триггеры состоят из двух элементов И-ИЛИ-НЕ и 5. Результат преобразования поступает

на выход 6 преобразования. Между разрядами счетчика 1 включена группа элементов 2И-ИЛИ 7. Кроме того, преобразователь содержит триггер режима 8, входные элементы И-НЕ 9-10, элемент И-НЕ 11 обнуления, элемент И 12, информационные входы 13-1 преобразователя.

Преобразователь кода в число импульсов работает следующим образом.

В исходном состоянии нулевой разряд счетчика 1 находится в единичном состоянии, а остальные разряды счетчика 1 и триггер переключения 8 находятся в нулевом состоянии, разречиая при этом прохождение информации, которая поступает на входы 13 и 14 в парофазном Последовательном коде, через входные элементы И-НЕ 9 и 10 на информационные входы счетчика 1 и устанавливая последний в режим сдвигового регистра. Поступающая информация сдвигается по тактовым си1- налам, причем при приеме последнего разряда информации единица, записанная в нулевой разряд счетчика 1 в

исходном состоянии, дойдя до старшего разряда, разрешает переключиться триггеру режима типа защелка, который переключаясь по заднему фронту тактового сигнала, запрещает прохождение информации на вход счетчика 1, переключает последний в режим счета и разрешает прохождение сигналов тактовой частоты.на выход преобразователя. Как только количество прошедших импульсов на выходе преобразователя достигает величины равной значению обратного кода, когда записанного в счетчике 1, все разряды счетчика 1 устанавливаются в единичное состояние, и на выходе элемента И-НЕ обнуления 11 сформировывается сигнал низкого уровня, который устанавливает элементы преобразоЪателя в исходное состояние, подготавливая его тем самым к приему нового кода информации.

Предлагаемый преобразователь кода в число импульсов по сравнению с прототипом позволяет уменьшить количество корпусов ИМС при 8-разрядном счетчике с 37 до 27 в случае построения преобразователя на ИМС серии , а также уменьшить количество входов и упростить управление прербразователем.

Формула изобретения

ности лреобра зователя, он содержит два входных элемента И-НЕ, группу . из п элементов 2И-ИЛИ и элемент И-НЕ обнуления, выход которого соединен с входами сброса основных триггеров с 1-го по п-ый разряды, с входом начальной установки единицы основного триггера нулевого разряда, входом начальной.установки нуля вспомогательного триггера нулевого разряда, с входами начальной установки единицы вспомогательных триггеров с 1-го по п-ый разряды и входом сброса триггера режима, нулевой выход которого соединен с первыми входами элементов 2И-ИЛИ группы и первыми входами первого и второго входных элементов И-НЕ вторые входы которых являются инфбрмационными входами

преобразователя, а выходы соединены соответственно с вторым нулевым и единичным входами вспомогательного триггера нулевого разряда, тактовый вход которого соединен с тактовым

.входом преобразователя и с вторыми входами элементов 2И-ИЛИ группы, третьи входы которых соединены с единичным выходом триггера режима, четвертый вход j-ro () элемента

2И-ИЛИ группы соединен с единичным выходом основного триггера (j-l)-ro разряда, с вторым единичным входом вспомогательного триггера j-ro разряда и с j-ым входом элемента И-НЕ обнуления, а выход J-ro элемента 2И-ИЛИ группы соединен с тактовыми входами основного и вспомогательного триггеров j-ro разряда, нулевой выход основного триггера (j)ro разряда .

- соединен с вторым нулевым входом, вспомогательного триггера j-ro разряда .

единичным и нулевым входами вспомогательного триггера, пятый и шестой входы первого элемента И-ИЛИ-НЕ объединены и являются входом началь ной установки вспомогательного триг гера.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-07-15—Публикация

1980-10-08—Подача