1

Изобретение относится к электро-г связи и может быть использовано в системах передачи цифровых данных.

По основному авт.- св. N «95779 известно устройство для фазовой синхронизации в системах передачи данных, содержащее последовательно соединенные двухполупериодный выпрямитель, компаратор, триггер, первый переключатель, интегратор со знакопеременным весом интегрирования, дифференциатор, элемент И, триггер направления фазы, второй переключатель.первый интегратор, накопитель и фазосдвигающий узел, выход которого подключен к второму входу триггера,а к второму входу фазосдвигающего узла подключен выход генератора тактовой частоты, а также источник опорного напряжения и узел установки начальной фазы синхронизации, выход которого подключен к второму .входу накопителя , при этом выходы источника опорного напряжения подключены к

вторым входам первого и второго переключателей , а выход генератора низкой частоты подключен к второму входу элемента И и входу блока задержки, выход которого подключен к второму входу дифференциатора, второй вход которого,объединен со вторым входом коммутатора ll.

Однако известное устройство обладает низкой точностью установки синхронизации при перерывах в каналах связи.

Цель изобретения - повышение точности установки фазы синхронизации при перерывах в каналах связи.

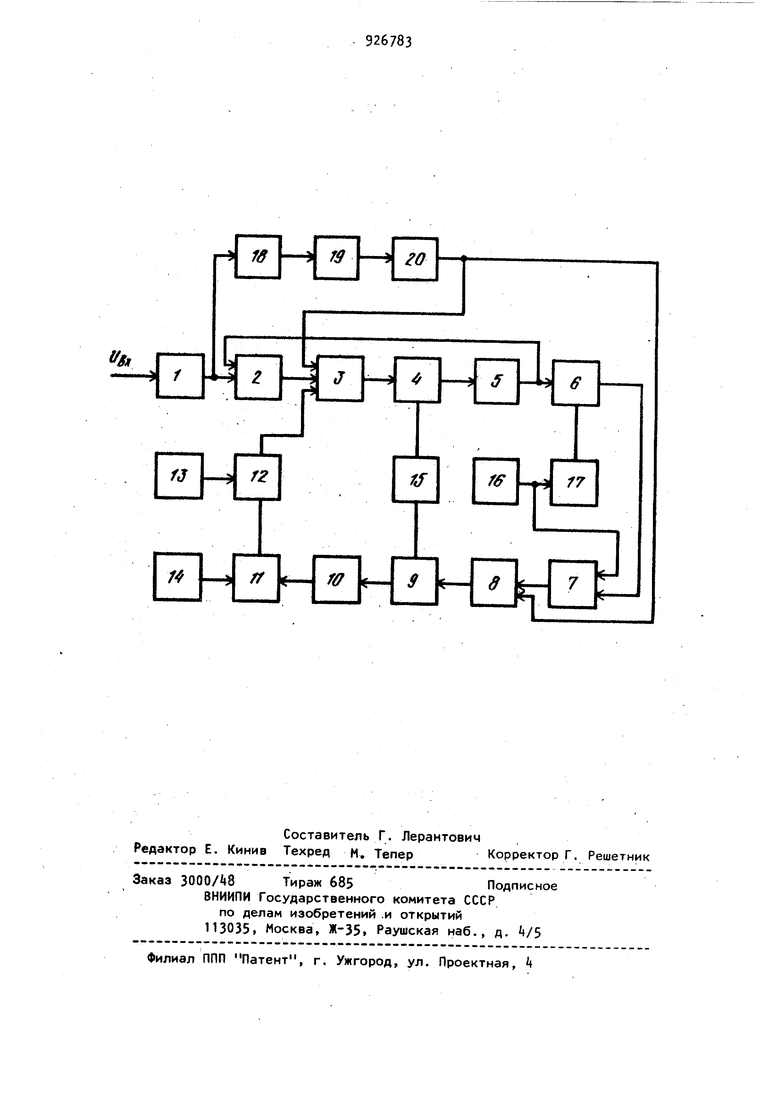

Для достижения указанной цели в устройство для фазовой синхронизации в системах передачи данных введены последовательно соединенные фиксатор нулевого уровня, второй интегратор и датчик значащего сигнала, выход которого подключен к третьему входу триггера и второму входу триггера направления фазы, при этом выход двухполупериодного .выпрямителя подключен к входу фиксатора нулевого уровня. На чертеже представлена структурная электрическая схема устройства. Устройство для фазовой синхрониза ции в системах передачи данных содер жит двухполупериодный выпрямитель 1, компаратор 2, триггер 3 первый переключатель 4, интегратор 5 со знакопеременным весом интегрирования, дифференциатор 6, элемент И 7 триггер 8 направления фазы, второй переключаteль 9 первый интегратор 10, накопитель 11, фазосдеигающий узел 12, генератор 13 тактовой частоты, узел И начальной установки фазы синхрони зации, источник 15 опорного напряжения, генератор 16 низкой частоты, блок 17 задержки, фиксатор 18 нулевого уровня, второй интегратор 19 датчик 20 значащего сигнала. Устройство работает следующим обра Сигнал данных Ufix поступающий на вход двухполупериодного выпрямителя 1, выпрямляется им и поступает на компаратор 2, где сравнивается с пороговым уровнем, выдаваемым интегратором 5 со знакопеременным весом интегрирования. Компаратор 2 выдает зна чащий выходной сигнал, если сигнал данных превышает пороговый уровень. Сигнал на выходе компаратора 2 управляет триггером 3$ который.синхронизирован частотой генератора 13 тактовой частоты. Триггер 2 приводив в действие первый переключатель 4, который подключает от источника 15 опорного напряжения напряжение положительной полярности, если триггер 3 находится в состоянии 1, и отрицательной полярности, если он находится в состоя нии О, на вход интегратора 5 со знакопеременным весом интегрирования Интегратор 5 со знакопеременным весом интегрирования устроен таким образом,, что напряжение положительной полярности интегрируется с весом в раз большим, чем напряжение отри цательной полярности, где п количест во уровней сигнала данных. Это обусловлено тем, что сигнал данных прини мает значение верхнего уровня в п-1 раз меньше, чем в сумме значения все остальных .уровней. Вследствие этого напряжение отрицательной полярности по времени будет в п-1 раз больше 92 воздействовать на интегратор 5 со знакопеременным весом интегрирования, чем напряжейие положительной полярности.. Переменный пороговый уровень,выдаваемый интегратором 5 со знакопеременным весом интегрирования, поступает на компаратор 2 и дифференциатор 6. Увеличение порогового уровня указывает на уменьшение искажения сигнала данных, в противном случае не увеличение. Дифференциатор 6 выдает сигнал О при увеличении порогового уровня от выборки к выборке и сигнал 1 - при уменьшении усредняя одновременно эти значения. Выходной сигнал дифференциатора 6 через элемент И 7 управляет триггером 8 направления фазы. Второй вход элемента И 7 подключен к выходу генератора 16 низкой частоты, частота которого может иметь период порядка нескольких секунд, тогда как период выборки сигнала данных измеряется в миллисекундах. Выходной сигнал генератора 16 низкой частоты через блок 17 задержки устанавливает в исходное состояние дифференциатор 6. Триггер 8 направления фазы управляет вторым переключателем Э- Если триггер 8 направления фазы находится в состоянии 1, то второй переключатель 9 подает на вход первого интегратора 10 положительное напряжение от источника 15 опорного напряжения и в состоянии о отрицательное напряжение. Первый интегратор 10 управляет через накопитель 11 фазосдвигающим узлом 12 таким образом, что вызывает увеличивающийся сдвиг фазы выходного сигнала генератора 1.3 тактовой частоты в направлении уменьшения искажения сигнала данных. Узел I начальной установки фазы синхронизации используется для запуска системы через накопитель 11 и обеспечивает начальную установку фазы синхронизации, которая определяется на основе предварительного значения системы или на основе специальных сигналов пуска. При перерыве в канале связи с выхода двухполупериодного выпрямителя 1 на входы компаратора 2 и фиксатора 18 нулевого уровня поступает сигнал с нулевым уровнем. Фиксатор 18 нулевого уровня по этому сигналу выдает положительное напряжение на 5 второй интегратор 19. Если в течение заданного времени на второй интегратор 19 поступает положительное напря жение, то с выхода второго интегратора 19 выдается сигнал, который включает датчик 20 значащего сигнала. При поступлении на фиксатор 18 нулевого уровня сигнала данных прек ращается выдача положительного напря жения на второй интегратор 19, который сбрасывается в исходное состояние, и выключается датчик 20 значащего сигнала. Включенный датчик 20 значащего сигнала -генерирует периодическую последовательность значащего сигнала, которая поступает на третий вход триггера 3 и второй вход триггера 8 направления фазы, осуществляя его реверс с приходом каждого импульса, Дпительность значащего сигнала должна быть равна или больше периода следования сигналов тактовой частоты генератора 13 тактовой частоты. Это обеспечивает установку в состояние 1 триггера 3 за время длитель ности значащего сигнала. Длительност промежутков в последовательности,генерируемой датчиком 20 значащего сиг нала, должна быть в п-1 раз больше длительности значащего сигнала, что обеспечивает нахождение триггера 3 в состояние О в п-1 раз дольше,чем в состоянии 1. Генерируемая датчиком 20 значащего сигнала за время перерыва в канал связи последовательность периодически устанавливает триггер 3 в состояние 1 и реверсирует триггер 8 направления фазы, которые управляют пе реключателями 4 и 9 соответственно. Переключатели Ц и 9 в соответствии с состоянием триггеров 3 и 8 подключаю к интеграторам 5 и 10 то положительное, то отрицательное напряжение. С выхода интегратора 5 со знакопеременным весом интегрирования в не значительных пределах будет отклоняться в положительную или отрицательную сторону от значения порогово 83 го уровня, предшествовавшего перерыву в канале связи. С выхода первого интегратора 10 также выдается аналогичный уровень напряжения. Этот уровень управляет через накопитель 11 фазосдвигаощим узлом 12, что вызывает незначительное колебание фазы относительно значения фазы синхронизации, предшествовавшей перерыву в канале связи. Таким образом, после окончания перерыва в канале связи пороговый уровень на входе компаратора 2 и фаза синхронизации практически совпадают с пороговым уровнем и фазой синхронизацией до перерыва. Так ка-к поступают щий после перерыва на вход устройства сигнал данных имеет такие же уровни и фазу, как и до перерыва, поскольку генерируется одним и тем же источником, то сбои фазы синхронизации в устройстве из-за перерывов будут исключены, что обеспечивает высокую точность установки фазы синхронизации устройства. Формула изобретения Устройство для фазовой синхронизации в системах передачи данных по авт. св. tf 95779 о т л и ч а ю щ е е с я тем, что, с целью повышения точности установки фазы синхрони зации при перерывах в каналах связи, введены последовательно соединенные фиксатор нулевого уровня, второй интегратор н датчик значащего сигнала, выход которого подключен к третьему входу триггера и второму входу триггера направления фазы, при этом выход двухполупериодного выпрямителя подключен к входу фиксатора нулевого уровня. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № J 95779, кл. НО L 7/02, 197 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фазовой синхронизации в системах передач данных | 1974 |

|

SU495779A1 |

| Устройство для взвешивания ковшадРАглАйНА | 1979 |

|

SU804775A1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1983 |

|

SU1142859A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| Устройство для защиты от токов утечки в электрической сети с изолированной нейтралью | 1987 |

|

SU1453509A1 |

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ СВЧ-ИЗЛУЧЕНИЙ | 1993 |

|

RU2040005C1 |

| Устройство для обнаружения юза колесных пар подвижного состава | 1987 |

|

SU1532349A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

Авторы

Даты

1982-05-07—Публикация

1980-08-14—Подача