I

Изобретение относится к электросвязи.

Известно устройство для детектирования фазоманипулированных сигналов, содержащее формирователе опорно го сигнала; выход которого соединен с первыми .входами канальных перемножителей, вторые и третьи входы которых соединены с выходами усилителя , а выходы соединены с первыми входами интеграторов, выходы которых соединены с входами блока сканирования, выходы которого соединены с входами блока вычисления разности фаз, подключенного к блоку декодирования, последовательно соединенные блок синхронизации и управления, формирователь огибающий и групповой перемножитель 1 .

Однако в известном устройстве недостаточная помехоустойчивость.

Цель изобретения - повышение помехоустойчивости путем компенсации аппаратурной помехи.

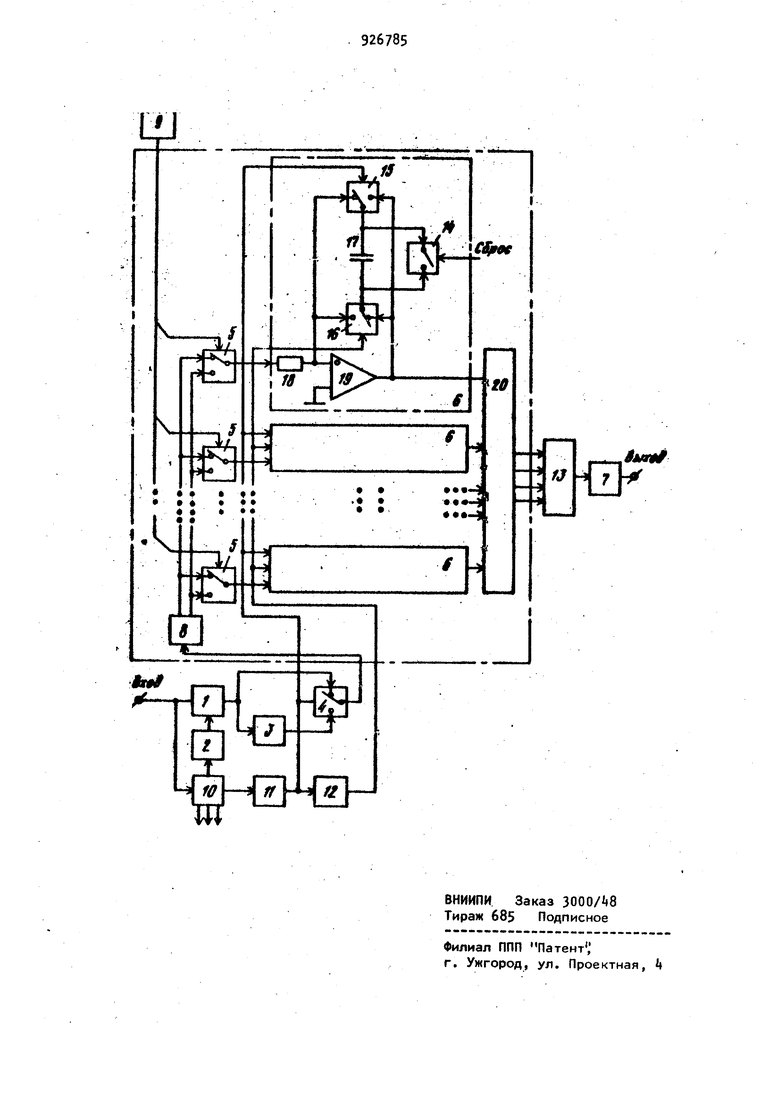

Указанная цель достигается reif, что в устройство для детектирования фазоманипулированных сигналов,, содержащее формирователь опорного сигнала, выход которого соединен с первыми входами канальных перемножителей, вторые и третьи входы которых соединены с выходами усилителя, а выходы соединены с первыми входами интеграторов, выходы которых соединены с входами блока сканирования, выходы которого соединены с входами блоксв вычисления разности фаз, подключённого к блоку декодирования, последовательно соединенные блок синхронизации и управления, формирователь огибающей и групповой перемножитель, введены формирователь импульсов переключе.ния, два инвертора и переключатель, причем другой вход группового перемножителя соединен с входом блока синхронизации и управления, выход которого через последовательно соеди- ; ненные формирователь импульсов пере39ключения и один инвертор соединен с вторыми входами интеграторов, третьи входы которых соединены с выходом формирователя импульсов переключения подключенного к первому входу переключателя, выход группового перемножителя соединен с вторым входом пере ключателя и через другой инвертор с третьим входом переключателя, выход которого соединен с входом усилителя. Интегратор состоит из резистора, операционного усилителя, конденсаfopa и трех переключателей,, причем выход резистора соединен с одним BXO дом операционного усилителя и первыми входами первого и второго переключателей, вторые входы которых сое динены с выходом операционного усилителя, а выходы - с обкладками кондендатора и первым и-вторым входами третьего переключателя, причем вход резистора является первым входом интегратора, третьи входы первого и второго переключателей являются вторым и третьим входами интегратора. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство содержит групповой перемножитель 1, формирователь 2 огиба йщей, инвертор 3, переключатель t, канальные перемножители 5, интеграторы 6, блок 7 декодирования, усилитель 8, формирователь 9 опорного сигнала, блок 10 синхронизации и управления, формирователь 11 импульсов переключения, инвертор 12, блок 13 вычисления разности фаз, интегратор 6 состоит из переключателей l4-1 конденсатора 17, резистора 18 и операционного усилителя 19, а также блок 20 сканирования. Устройство работает следующим образом. Групповой сигнал поступает на вхо ды группового перемножителя 1 и блок 10 синхронизации и управления. Этот сигнал может поступать либо непосред ственно от приемной аппаратуры радио связи, либо при необходимости автома тической подстройки частоты (АПЧ) че рез систему АПЧ демодулятора. Блок 10 синхронизации выявляет границы по сылок (элементов) сигнала и по импульсам из блока 10 в формирователе 2 формируется напряжение соответству ющей формы. 5 В групповом перемножителе 1 групповой сигнал умножается на это напряжение и результат перемножения в прямом или инвертированном виде в зависимости от положения переключателя 4 поступает на вход интегратора 6. В усилителе 8 формируются два противофазных напряжения, которые поступают на входы канальных перемножителей 5Результат перемножения интегрируется в интеграторах 6. Неидентичность (конечная длительность переключения) канальных перемножителей 5 и нелинейность их характеристик проводимости приводят к тому, что для одной vHaпример, положительной) полярности группового сигнала канальный перемножитель 5 оказывает меньшее сопротивление, чем для другой полярности. В результате на выходе канальных перемножителей 5 возникает паразитная постоянная составляющая, величина которой определяется амплитудой группового сигнала (суммой сигнала и помехи). Эта постоянная составляющая интегрируется в интеграторе 6 и создает аппаратную помеху. Некоторый вклад в величину аппаратурной помехи вносят также входной ток операционногб усилителя 19 (вернее разность входных токов) и разность вход ных напряжений. Правда в новых типах операционных усилителей 19 значения указанных токов и напряжений значительно уменьшены и теперь основной вклад в аппаратурную помеху вносят перемножители. Для компенсации аппаратурной поме « предлагаемом устройстве производится переключение конденсатора 17 переключателями 15 и 1б. 3 первой половине интервала интегрирования положение переключателей 15 и 16 соответствует показанному на чертеже, верхняя обкладка присоединена к входу, а нижняя к выходу операционного усилителя 19, при этом на верхней обкладке накапливается, например, положительный потенциал аппаратурной помехи. Зо второй половине посылки положение переключателей 15 и 1б меняется на противоположное и теперь положительный потенциал аппаратурной помехи будет накапливаться на нижней обкладке конденсатора. Вследствие симметричности огибающей группового сигнала происходит полная компенсация аппаратурной помехи. Для того, чтобы не происходила компенсация результата накопления сигнала, одновременно с переключением обкладок конденсатора 17 производится изменение полярности (инвертирование) группового сигнала с помощь переключателя k и инвертора 3Результат интегрирования сигнала поступает для дальнейшей обработки через блок 20 сканирования в блок 13 вычисления разности фаз и затем в блок 7 декодирования, в котором происходит выделение и браковка символо пораженных сосредоточенной помехой, и выдача на выход устройства информа ционных символов с максимальным прав доподобием, т.е. реализуется за счет информационной избыточности высокая помехоустойчивость. Формула изобретения 1. Устройство для детектирования фазоманипулированных сигналов, содер жащее формирователь опорного сигнала которого соединен с первыми вх дами канальных перёмножителей, вторы и третьи входы которых соединены с выходами усилителя, а выходы соедине ны с первыми входами интеграторов,вы ходы которых соединены с входами бло ка сканирования, выходы которого сое динены с входами блока вычисления разности фаз, подключенного к блоку декодирования, последовательно соеди ненные блок синхронизации и управления , формирователь огибающей и групповой перемножитель, отличающееся тем, что, с целью повышения помехоустойчивости путем компен856сации аппаратурной помехи, введены формирователь импульсов переключения, два инвертора и переключатель, причем другой вход группового перемножителя соединен с входом блока синхронизации и управления, выход которого через последовательно соединенные формирователь импульсов переключения и один инвертор соединен с вторыми входами интеграторов, третьи входы которых соединены с выходом формирователя импульсов переключения, подключенного к первому входу переключателя , выход группового перемножителя соединен с вторым входом переключателя и через другой инвертор с третьим входом переключателя, выход которого соединен с входом усилителя. 2. Устройство по п. 1, 6 т л и чающееся тем, что,интегратор состоит из резистора, операционного усилителя, конденсатора и трех переключателей , причем выход резистора соединен с одним входом операционного усилителя и первыми входами первого и второго переключателей, вторые входы которых соединены с выходом операционного усилителя, а выходы - с обкладками конденсатора и первым и вторым входами третьего переключателя, причем вход резистора является первым входом интегратора, третьи входы,первого и второго переключателей являются вторым и третьим входами интегратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке If 2683036/09, . кл. Н Oi L 27/22, 09.11.78 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1061287A2 |

| Устройство для детектирования фазоманипулированных сигналов | 1978 |

|

SU788427A1 |

| Коррелятор | 1980 |

|

SU875403A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1042203A1 |

| ПРЕОБРАЗОВАТЕЛЬ МОЩНОСТИ В ЧАСТОТУ | 1992 |

|

RU2057349C1 |

| Демодулятор многочастотных сигналов с фазоразностной модуляцией | 1981 |

|

SU995367A1 |

| Устройство для моделирования спиральной развертки | 1982 |

|

SU1062729A1 |

| Аналоговое вычислительное устройство | 1985 |

|

SU1297081A1 |

| УСТРОЙСТВО СВЯЗИ СЛУЧАЙНЫМИ ЭЛЕКТРИЧЕСКИМИ СИГНАЛАМИ | 1980 |

|

SU1840271A1 |

Авторы

Даты

1982-05-07—Публикация

1980-02-19—Подача