Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является рас- ширение класса решаемых задач.

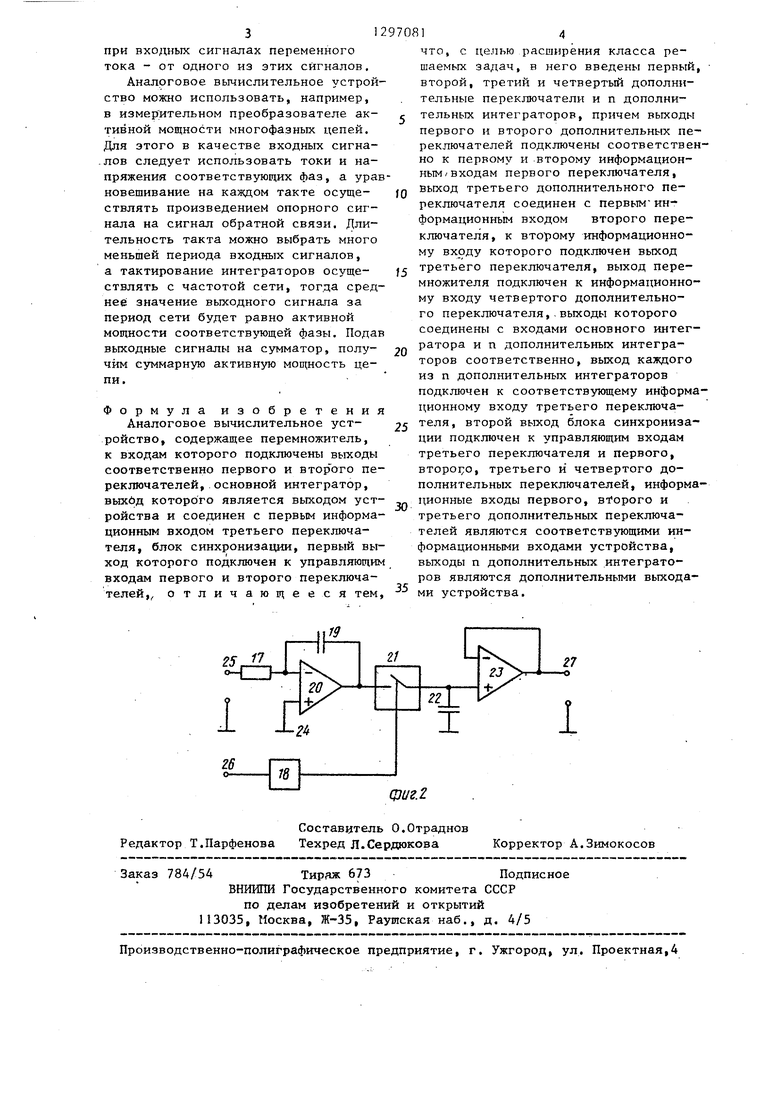

На фиг. 1 изображена функциональная схема аналогового вычислительного устройства; на фиг. 2 - вариант функциональной схемы интегратора

На чертежах обозначены перемножитель I, первый, второй и третий переключатели 2-4, первый, второй, третий и четвертый дополнительные переключатели 5-8, основной ин тегратор 9, дополнительные интеграторы 10 ,,,..,10, блок синхронизации

1 1 , входы 12,12п, 1 3, , 1 3, 1Д, ,.

14 устройства, выход 15, дополнительные выходы 1 6 I16 , масшта

бньй резистор 17, формирователь импульсов 18, накопительный конденсатор 19, первьй операционный усилитель 20, ключ 21, запоминающий конденсатор 22, второй операционный усилитель 23, шина нулевого потенциала 24, информационный вход 25, тактовый вход 26, выход 27.

Аналоговое вычислительное устройство работает следующим образом.

Период.работы состоит из п тактов, задаваемых блоком синхронизации П.. На время одного такта подвижные контакты третьего переключателя 4, первого, второго, третьего и четвер- того дополнительных переключателей 5-8 подключаются к соответствующим неподвижным контактам, а в первом и ВТОРОМ переключателях 2 и 3 подвижные контакты поочередно подключают- ся к цервому и второму неподвижным контактам.

Возможны варианты управления переключателями, когда продолжительность замкнутого состояния соответ- ствующих контактов третьего переключателя 4, первого, второго, третьего и четвертого дополнительных переключателей 5-8 во много раз больше (или меньше) периода работы первого и второго переключателей 2 и 3.

Удобно выбрать длительность тактов, равной периоду работы первого и второго переключателей 2 и 3, а продолжительность переключения их - одинаковой.

Для устойчивой работы необходимо обеспечить отрицательный знак обратной связи.

Положим, что входные сигналы за время такта остаются постоянными.

В первом такте к неподвижным контактам первого и второго переключателей 2 и 3 подключены сигналы со входов 12, 13,, 14 и сигнал обратной связи с выхода 15. Установив- тийся режим работы будет достигнут тогда, когда среднее значение на выходе интегратора 9 за период работы переключателей 2 и 3 станет равным нулкз. Отсюда

7 Slit. 1 А.

(1)

где Z - среднее значение сигнала на выходе 15;

X, ,У

1

j - средние значения сигналов . с входов 12, 13, 14,.

Аналогичный вид сигналов будет и на остальных выходах 16 ,...,16 . В случае, когда интегратор имеет большую постоянную времени при отключении его от источника входного сигнала напряжение на его выходе не изменяется до следующего подключения. В этом случае можно к одному из входов, например первого дополнительного переключателя 5 подключить сигнал с выхода 15. Тогда на- выходе 16 сигнал равен

2 .Za.

(2)

или

.С.,

(3)

где X,y,, сигналы с входов 12

13, 14.

Для повышения быстродействия и уменьшения пульсаций выходного сигнала в устройстве можно использовать интегратор с тактируемым запоминанием вариант функциональной схемы которого приведен на фиг. 2. На первом операционном усилителе 20 собран интегратор, к выходу которого подключено устройство аналоговой памяти, состоящее из ключа 21, запоминающего конденсатора 22 и повторителя на втором операционном .усилителе 23„ Ключ 21 периодически замыкается короткими импульсами, поступающими с выхода формирователя импульсов 18. При сигналах постоянного тока тактирование осуществляется от блока синхронизации 11, а

3

при входных сигналах переменного тока - от одного из этих сигналов.

Аналоговое вычислительное устройство можно использовать, например, в измер;ительном преобразователе ак- тивной мощности многофазных цепей. Для этого в качестве входных сигна- .лов следует использовать токи и напряжения соответствующих фаз, а урановешивание на каукцом такте осуще- ствлять произведением опорного сигнала на сигнал обратной связи. Длительность такта можно выбрать много меньшей периода входных сигналов, а тактирование интеграторов осуще- ствлять с частотой сети, тогда среднее значение выходного сигнала за период сети будет равно активной мощности соответствующей фазы. Пода выходные сигналы на сумматор, полу- чйм суммарную активную мощность цепи.

Формула изобретения

Аналоговое вычислительное устройство, содержащее перемножитель, к входам которого подключены выходы соответственно первого и вторЪто переключателей, основной интегратор, выхйд которо го является выходом устройства и соединен с первым информационным входом третьего переключателя, блок синхронизации, первый выход которого подключен к управляющим входам первого и второго переключателей,, отличающееся тем.

Редактор Т.Парфенова

фиг.г

Составитель О.Отраднов Техред Л.Сердюкова

Заказ 784/54 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раутская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

o 5 0

5

0

5

что, с целью расширения класса решаемых задач, в него введены первый, второй, третий и четвертый дополнительные переключатели и п дополнительных интеграторов, причем выходы первого и второго дополнительных переключателей подключены соответственно к первому и второму информационным / входам первого переключателя, выход третьего дополнительного переключателя соединен с первым информационным входом второго переключателя, к второму информационному входу которого подключен выход третьего переключателя, выход перемножителя подключен к информационному входу четвертого дополнительного переключателя,.выходы которого соединены с входами основного интегратора и п дополнительных интеграторов соответственно, выход каждого из п дополнительных интеграторов подключен к соответствующему информационному входу третьего переключателя, второй выход блока синхронизации подключен к управляющим входам третьего переключателя и первого, BTOpoi;o, третьего и четвертого дополнительных переключателей, информационные входы первого, второго и третьего дополнительных переключателей являются соответствующими информационными входами устройства, выходы п дополнительных интеграторов являются дополнительными выходами устройства.

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения энергии | 1987 |

|

SU1575120A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Устройство для синхронизации шумоподобных сигналов | 1982 |

|

SU1022326A1 |

| Интеллектуальный счетчик электрической энергии | 2021 |

|

RU2786977C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Кодек адаптивного дельта-модулятора | 1986 |

|

SU1378063A1 |

| Устройство для деления аналоговых сигналов | 1990 |

|

SU1795479A1 |

| Многоканальный преобразователь угол-код | 1983 |

|

SU1117304A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является расширение класса решаемых задач. Аналоговое вычислительное устройство содержит перемножитель 1, ко входам которого подключены выходы первого 2 и второго 3 переключателей, основной 9 и дополнительные 10 интеграторы, третий переключатель 4, включенньй в цепь отрицательной обратной связи, первый 5, второй 6 и третий 7 дополнительные переключатели, входы которых являются входами устройства, четвертый дополнительный переключатель 8, включенный меязду выходом перемножителя 1 и входами интеграторов 9 и 10, блок синхронизации 11. Работа устройства тактируется сигналами блока синхронизации 11, а за время тактов осуществляется перемножение входных сигналов и сигналов обратной связи. 2 ил. Q 16 (Л

| Широтно-импульсное множительное устройство | 1980 |

|

SU868783A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналоговое вычислительное устройство | 1981 |

|

SU1137485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-17—Подача