(Б) ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Способ тактовой синхронизации приемника двоичного частотно-модулированного сигнала и устройство для его осуществления | 1980 |

|

SU1361727A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1998 |

|

RU2136114C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

| Цифровой демодулятор сигналов относительной фазовой манипуляции | 1986 |

|

SU1374443A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| Цифровой когерентный частотный демодулятор | 1984 |

|

SU1322412A1 |

| Цифровой демодулятор сигналов с фазовой манипуляцией | 1983 |

|

SU1124447A1 |

I

Изобретение относится к технике связи и может использоваться в системах обмена дискретными сообщениями для приема сигналов относительной фазовой манипуляции.

Известен цифровой демодулятор сигналов относительной фазовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены ко входам дешифратора, первый выход которого соединен с первым входом триргера, а также генератор опорной частоты, выход которого подключен к тактовым входам блока выделения тактовой частоты и первого счетчика ,1 .

Однако такой демодулятор обладает низкой помехоустойчивостью при различных уровнях помех в линии связи.

Цель изобретения - повышение помехоустойчивости при различных уровнях помех в линии связи. .

Цель достигается тем, что в цифровой демодулятор сигналов относительной фазовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены к входам дешифратора, первый выход которого соединен с первым входом триггера, а также генератор

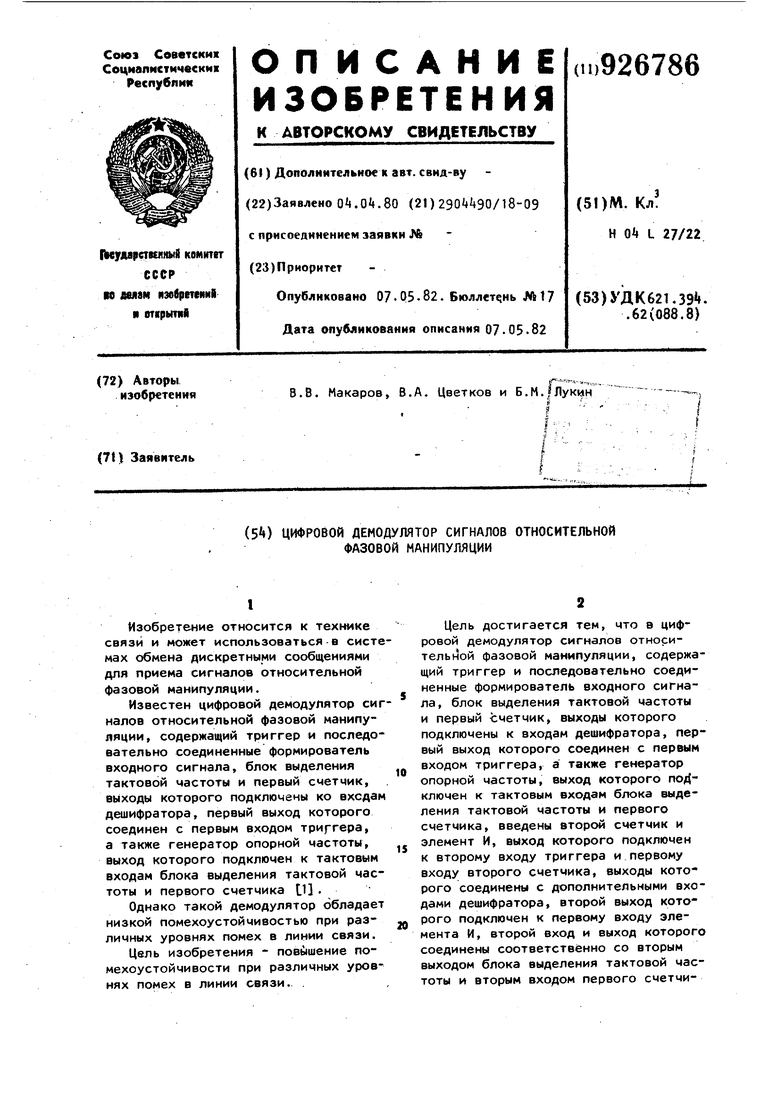

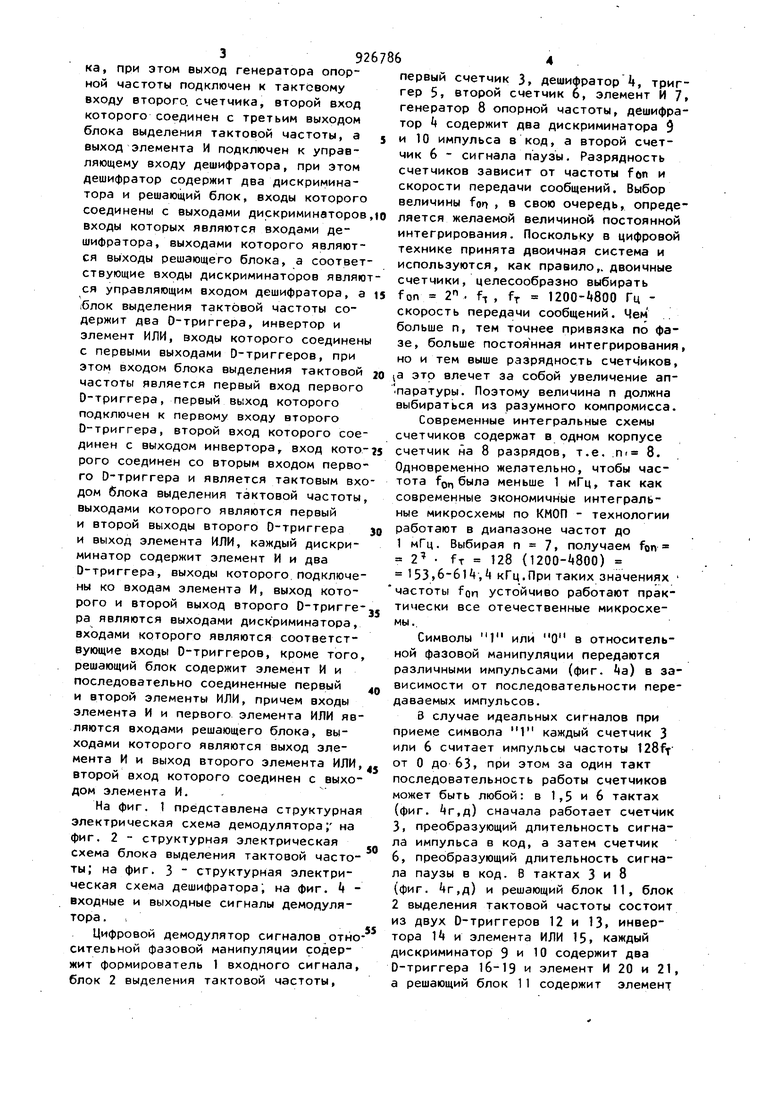

10 опорной частоты, выход которого nori ключен к тактовым входам блока выделения тактовой частоты и первого счетчика, введены второй счетчик и элемент И, выход которого подключен

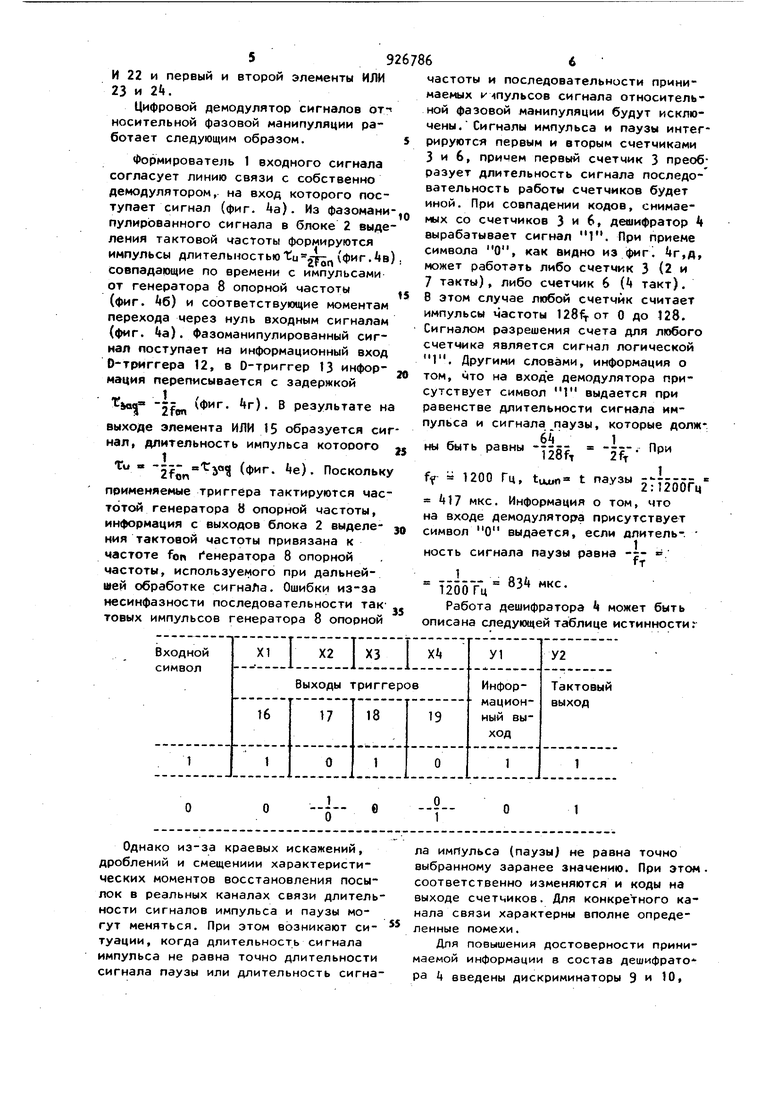

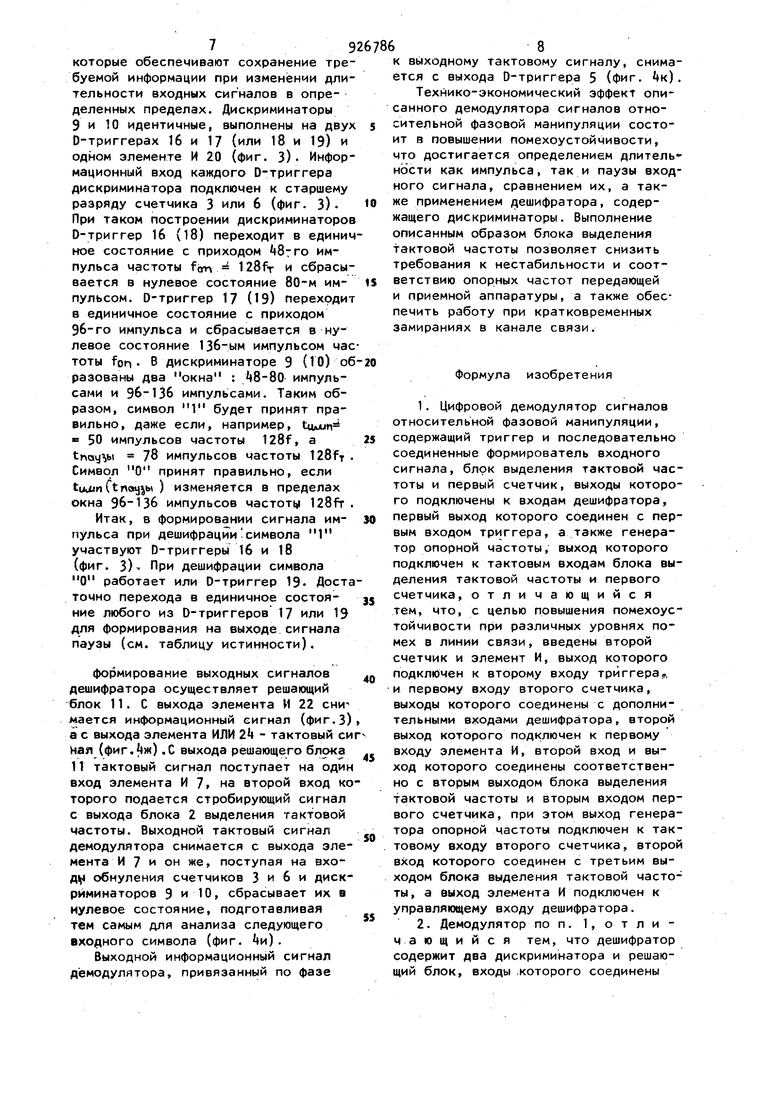

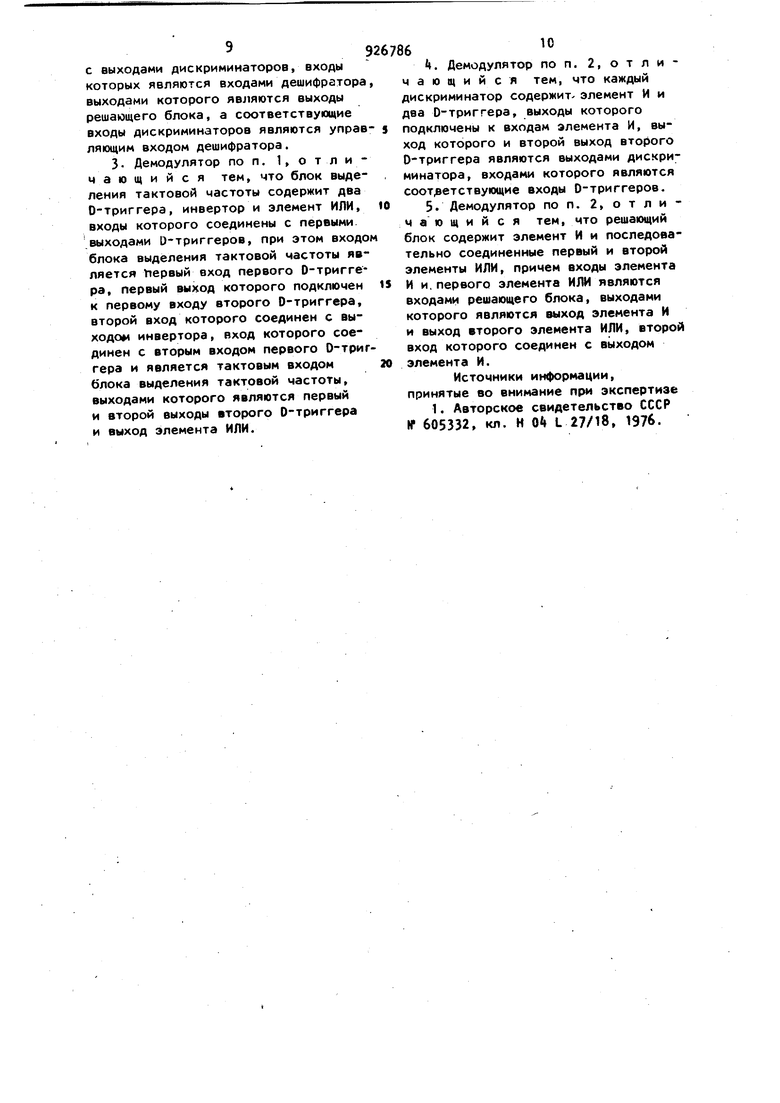

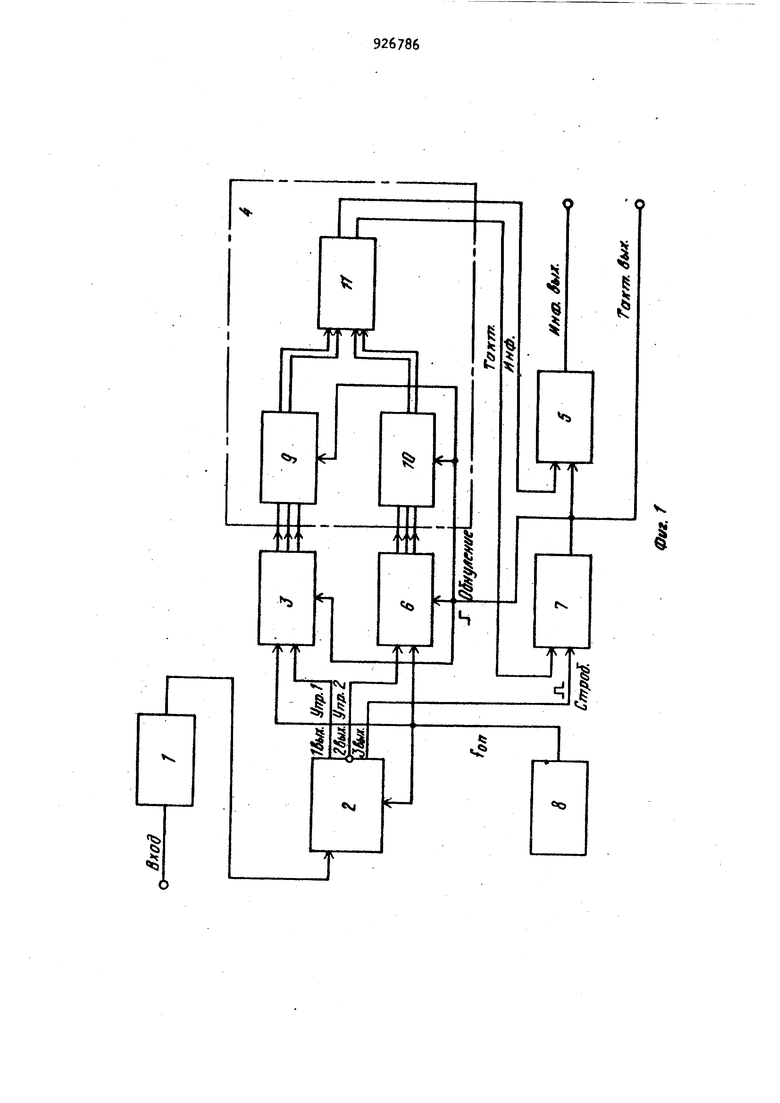

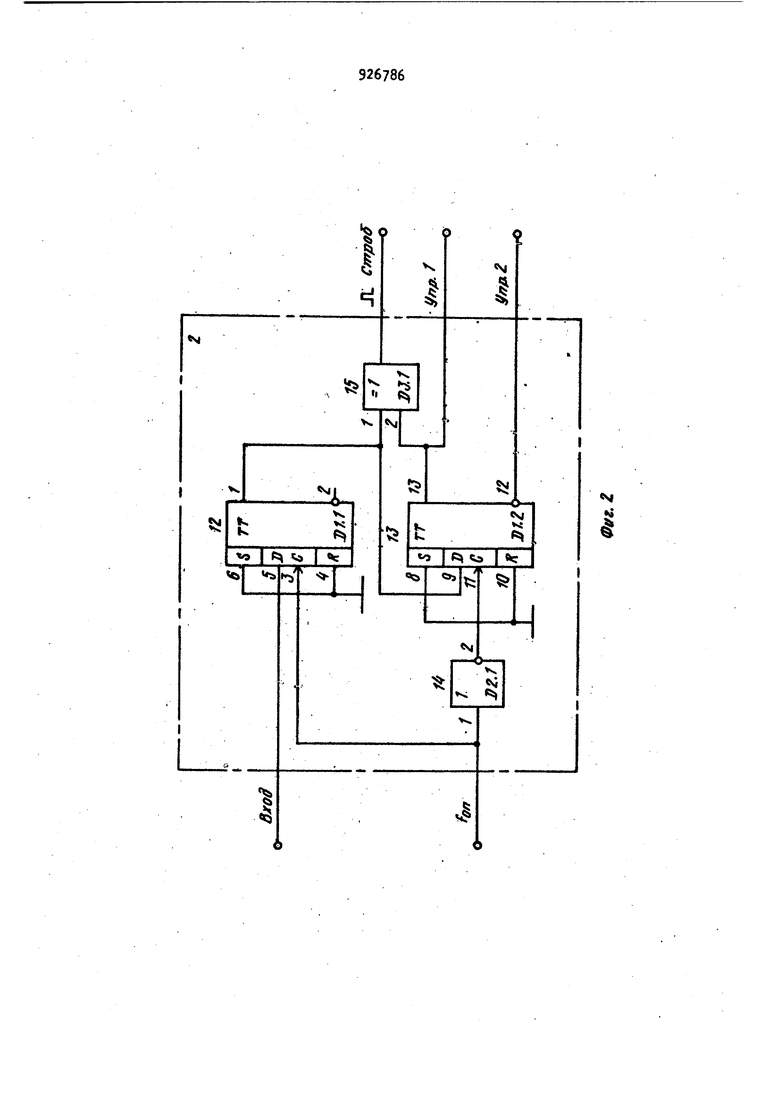

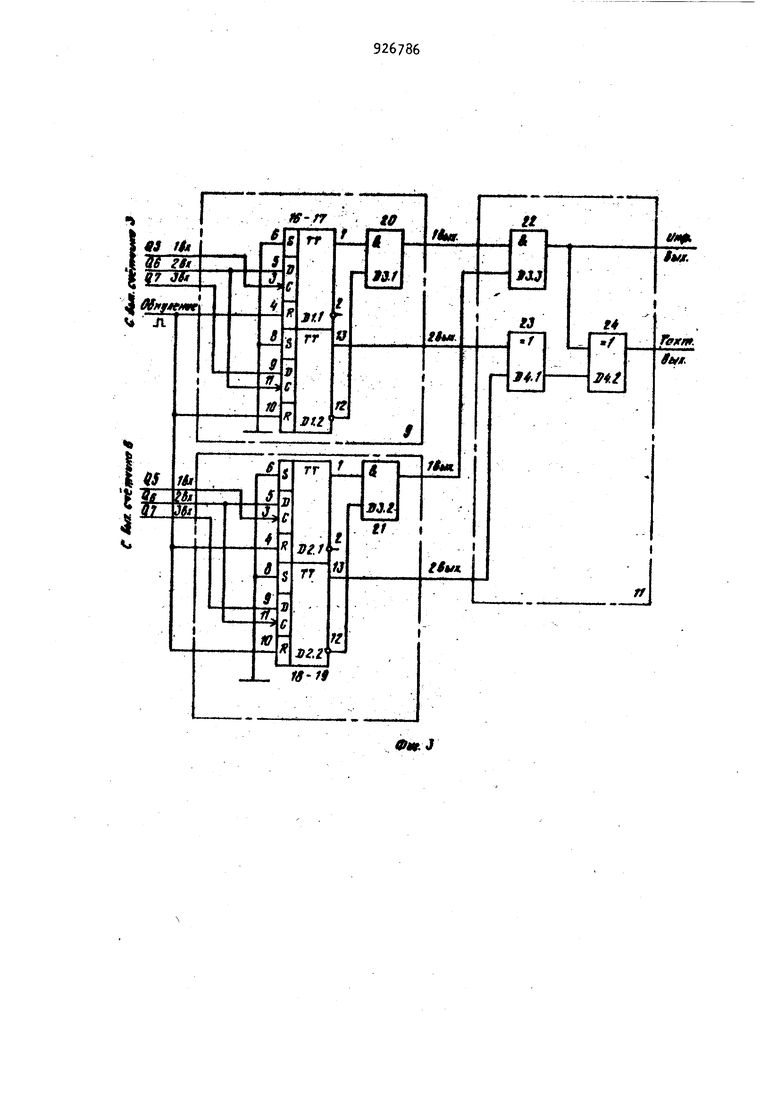

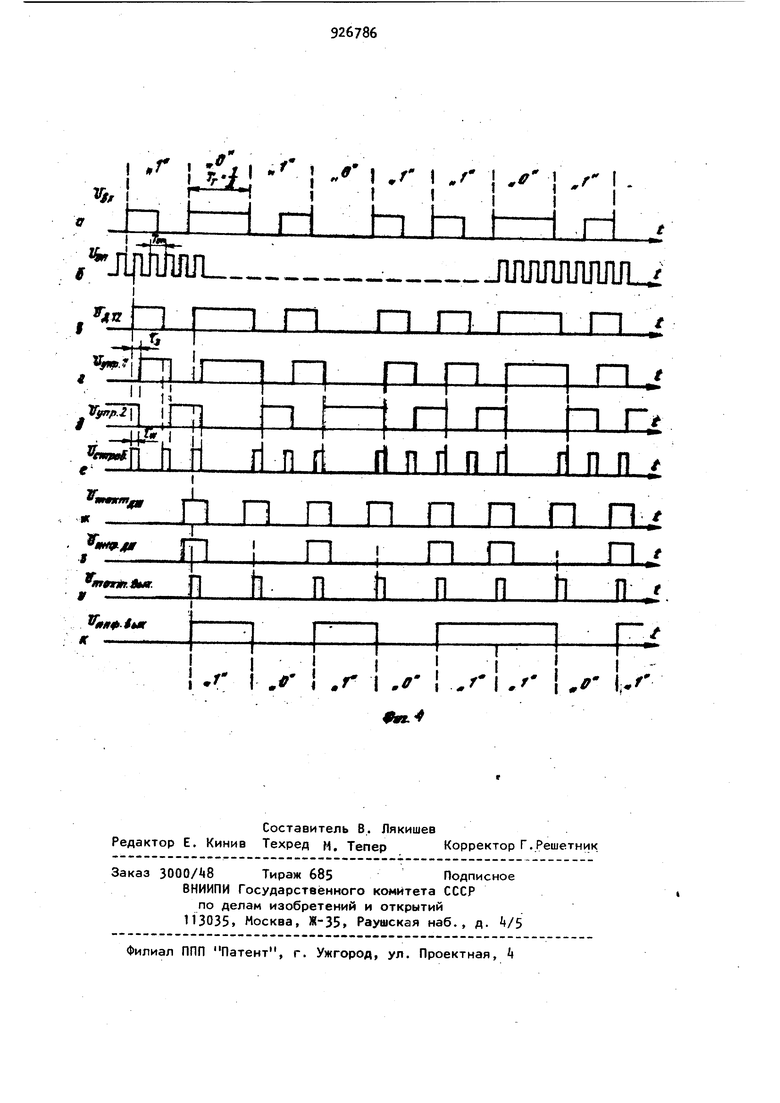

15 к второму входу триггера и первому входу второго счетчика, выходы которого соединены с дополнительными входами дешифратора, второй выход кото рого подключен к первому входу эле20мента И, второй вход и выход которого соединены соответственно со вторым выходом блока выделения тактовой частоты и вторым входом первого счетчи392678ка, при этом выход генератора опорной частоты подключен к тактовому входу второго, счетчика, второй вход которого соединен с третьим выходом блока выделения тактовой частоты, а выход элемента И подключен к управляющему входу дешифратора, при этом дешифратор содержит два дискриминатора и решающий блок, входы которого соединены с выходами дискриминаторов,о входы которых являются входами дешифратора, выходами которого являются выходы решающего блока, а соответствующие входы дискриминаторов являют ся управляющим входом дешифратора, а «блок выделения тактовой частоты содержит два 0-триггера, инвертор и элемент ИЛИ, входы которого соединены с первыми выходами О-триггеров, при этом входом блока выделения тактовой частоты является первый вход первого D-триггера, первый выход которого подключен к первому входу второго О-триггера, второй вход которого соединен с выходом инвертора, вход которого соединен со вторым входом первого О-триггера и является тактовым вхо дом блока выделения тактовой частоты, выходами которого являются первый и второй выходы второго О-триггера и выход элемента ИЛИ, каждый дискриминатор содержит элемент И и два О-триггера, выходы которого,подключены ко входам элемента И, выход которого и второй выход второго О-тригге ра являются выходами дискриминатора, входами которого являются соответствующие входы О-триггеров, кроме того решающий блок содержит элемент И и последовательно соединенные первый и второй элементы ИЛИ, причем входы элемента И и первого элемента ИЛИ яв ляются входами решающего блока, выходами которого являются выход элемента И и выход второго элемента ИЛИ второй вход которого соединен с выходом элемента И, На фиг. 1 представлена структурная электрическая схема демодулятора; на фиг. 2 - структурная электрическая схема блока выделения тактовой частоты; на фиг. 3 структурная электрическая схема дешифратораi на фиг, k входные и выходные сигналы демодулятора , Цифровой демодулятор сигналов отно сительной фазовой манипуляции содержит формирователь 1 входного сигнала блок 2 выделения тактовой частоты. 5 первый счетчик 3, дешифратор Ч, триггер 5, второй счетчик 6, элемент И 7 генератор 8 опорной частоты, дешифратор содержит два дискриминатора 9 и 10 импульса в код, а второй счетчик 6 - сигнала паузы. Разрядность счетчиков зависит от частоты fftn и скорости передачи сообщений. Выбор величины fort , в свою очередь, определяется желаемой величиной постоянной интегрирования. Поскольку в цифровой технике принята двоичная система и используются, как правило,, двоичные счетчики, целесообразно выбирать fon 2 . f-, , fт 1200- 800 Гц скорость передачи сообщений. Чем . больше п, тем точнее привязка по фазе, больше постоянная интегрирования, но и тем выше разрядность счетчиков. 3 это влечет за собой увеличение аппаратуры. Поэтому величина п должна выбираться из разумного компромисса. Современные интегральные схемы счетчиков содержат в одном корпусе счетчик на 8 разрядов, т.е, .П 8. Одновременно желательно, чтобы частота fp была меньше 1 мГц, так как современные экономичные интегральные микросхемы по КМОП - технологии работают в диапазоне частот до 1 мГц. Выбирая п 7 получаем fon 2 ft 128 {1200-А800) 153 6-6lt, кГц.При таких значениях частоты ffln устойчиво работают практически все отечественные микросхеСимволы 1 или О в относительной фазовой манипуляции передаются различными импульсами (фиг, а) в зависимости от последовательности передаваемых импульсов, В случае идеальных сигналов при приеме символа 1 каждый счетчик 3 или 6 считает импульсы частоты 128fT от О до 63, при этом за один такт последовательность работы счетчиков может быть любой: в 1,5 и 6 тактах (фиг, 4г,д) сначала работает счетЧик 3| преобразующий длительность сигнала импульса в код, а затем счетчик 6, преобразующий длительность сигнала паузы в код. В тактах 3 и 8 (фиг. ,д) и решающий блок 11, блок 2 выделения тактовой частоты состоит из двух О-триггеров 12 и 13, инвертора 1 и элемента ИЛИ 15, каждый дискриминатор 9 и 10 содержит два О-триггера 16-19 и элемент И 20 и 21, а решающий блок 11 содержит элемент 59 И 22 и первый и второй элементы ИЛИ 23 и 2. Цифровой демодулятор сигналов от- носительной фазовой манипуляции работает следующим образом. Формирователь 1 входного сигнала согласует линию связи с собственно демодулятором, на вход которого поступает сигнал (фиг. 4а). Из фазомани пулированного сигнала в блоке 2 выделения тактовой частоты формируются импульсы длительностью tu-ff(фиг.4в совпадающие по времени с импульсами от генератора 8 опорной частоты (фиг. б) и соответствующие моментам перехода через нуль входным сигналам (фиг. ka), Фазоманипулированный сигнал поступает на информационный вход 0-триггера 12, в О-триггер 13 информация переписывается с задержкой tsae 2fon ) результате на выходе элемента ИЛИ 15 образуется сиг нал, длительность импульса которого 2fon° (фиг. tie). Поскольку применяемые триггера тактируются частотой генератора 8 опорной частоты, информация с выходов блока 2 выделения тактовой частоты привязана к частоте fon Генератора 8 опорной частоты, используемого при дальнейшей обработке сигнала. Ошибки из-за несинфазности последовательности тактовых импульсов генератора 8 опорной

Однако из-за краевых искажений, дроблений и смещениии характеристических моментов восстановления посылок в реальных каналах связи длительности сигналов импульса и паузы могут меняться. При этом возникают ситуации, когда длительность сигнала импульса не равна точно длительности сигнала паузы или длительность сигнала импульса (паузы) не равна точно выбранному заранее значению. При этом соответственно изменяются и коды на выходе счетчиков. Для конкретного канала связи характерны вполне определенные помехи.

Для повышения достоверности принимаемой информации 8 состав дешифрато ра i введены дискриминаторы 9 и 10, 6 частоты и последовательности принимаемых (-«пульсов сигнала относительной фазовой манипуляции будут исключены. Сигналы импульса и паузы интегрируются первым и вторым счетчиками 3 и 6, причем первый счетчик 3 преобразует длительность сигнала последовательность работы счетчиков будет иной. При совпадении кодов, снимаемых со счетчиков 3 и 6, дешифратор 4 вырабатывает сигнал 1. При приеме символа О, как видно из фиг г,д, может работать либо счетчик 3 (2 и 7такты), либо счетчик 6 С такт). 8этом случае любой счетчик считает импульсы частоты 128fT от О до 128. Сигналом разрешения счета для любого счетчика является сигнал логической 1. Другими словами, информация о том, что на входе демодулятора присутствует символ 1 выдается при равенстве длительности сигнала импульса и сигнала паузы, которые долж (,ц ны быть равны Tpgf ff 1200 Гц, tuMrt t паузы 27Т20бГц if 17 МКС. Информация о том, что на входе демодулятора присутствует символ О выдается, если длитель-. ность сигнала паузы равна -;- . 83 МКС. 1200 Гц Работа дешифратора k может быть описана следующей таблице истинности: которые обеспечивают сохранение тре буемой информации при изменении длительности входных сигналов в определенных пределах. Дискриминаторы 9 и 10 идентичные, выполнены на двух D-триггерах 16 и 17 (или 18 и 19) и одном элементе И 20 (фиг. З) Инфор мационный вход каждого D-триггера дискриминатора подключен к старшему разряду счетчика 3 или 6 (фиг. З) При таком построении дискриминаторов D-триггер 16 (18) переходит в единич ное состояние с приходом 487 го импульса частоты fim - 128fT и сбрасывается в нулевое состояние 80-м импульсом. D-триггер 17 (19) переходит в единичное состояние с приходом 96-го импульса и сбрасывается в нулевое состояние 136-ым импульсом час тоты fon В дискриминаторе 9 (10) об разованы два окна : импульсами и 96-136 импульсами. Таким образом, символ 1 будет принят правильно, даже если, например, tuvun 50 импульсов частоты 128f, а )bi 78 импульсов частоты Символ О принят правильно, если tuvjun Ct nayjbt ) изменяется в пределах окна 96-136 импульсов частоту 128fr Итак, в формировании сигнала импульса при дешифрациисимвола 1 участвуют О-триггерЫ 16 и 18 (фиг. 3) При дешифрации символа О работает или D-триггер 19- Доста точно перехода в единичное состояние любого из D-триггеров 17 или 19 для формирования на выходе сигнала паузы (см. таблицу истинности). формирование выходных сигналов дешифратора осуществляет решающий блок 11. С выхода элемента И 22 сни мается информационный сигнал (фиг.З) а с выхода элемента ИЛИ 2k - тактовый си Нал (фиг.|(ж) .С выхода решающего блока 11 тактовый сигнал поступает на один вход элемента И 7, на второй вход ко торого подается стробирующий сигнал с выхода блока 2 выделения тактовой частоты. Выходной тактовый сигнал демодулятора снимается с выхода элемента И 7 и он же, поступая на вход обнуления счетчиков 3 и 6 и дискриминаторов 9 и 10, сбрасывает их в нулевое состояние, подготавливая тем самым для анализа следующего входного символа (фиг. ) . Выходной информационный сигнал демодулятора, привязанный по фазе К выходному тактовому сигналу, снимается с выхода О-триггера 5 (фиг. ) . Технико-экономический эффект описанного демодулятора сигналов относительной фазовой манипуляции состоит в повышении помехоустойчивости, что достигается определением длительности как импульса, так и паузы входного сигнала, сравнением их, а также применением дешифратора, содержащего дискриминаторы. Выполнение описанным образом блока выделения тактовой частоты позволяет снизить требования к нестабильности и соответствию опорных частот передающей и приемной аппаратуры, а также обеспечить работу при кратковременных замираниях в канале связи. Формула изобретения 1.Цифровой демодулятор сигналов относительной фазовой манипуляции, содержащий триггер и последовательно соединенные формирователь входного сигнала, блок выделения тактовой частоты и первый счетчик, выходы которого подключены к входам дешифратора, первый выход которого соединен с первым входом триггера, а также генератор опорной частоты, выход которого подключен к тактовым входам блока выделения тактовой частоты и первого счетчика, отличающийся тем, что, с целью повышения помехоустойчивости при различных уровнях помех в линии связи, введены второй счетчик и элемент И, выход которого подключен к второму входу триггера,, и первому входу второго счетчика, выходы которого соединены с дополнительными входами дешифратора, второй выход которого подключен к первому входу элемента И, второй вход и выход которого соединены соответственно с вторым выходом блока выделения тактовой частоты и вторым входом первого счетчика, при этом выход генератора опорной частоты подключен к тактовому входу второго счетчика, второй вход которого соединен с третьим выходом блока выделения тактовой частоты, а выход элемента И подключен к управляющему входу дешифратора. 2.Демодулятор по п. 1, о т л и чающийся тем, что дешифратор содержит два дискриминатора и решающий блок, входы .которого соединены с выходами дискриминаторов, входы которых являются входами дешифратора выходами которого являются выходы решающего блока, а соответствующие входы дискриминаторов являются управ ляющим входом дешифратора. 3. Демодулятор поп, 1, отличающийся тем, что блок выделения тактовой частоты содержит два 0-триггера, инвертор и элемент ИЛИ, входы которого соединены с первыми, выходами D-триггеров, при этом входо блока выделения тактовой частоты является 11ервый вход первого 0-триггера, первый выход которого подключен к первому входу второго D-триггера, второй вход которого соединен с выходов инвертора, вход которого соединен с вторым входом первого D-триг гера и является тактовым входом блока выделения тактовой частоты, выходами которого являются первый и второй выходы второго О-триггера и выход элемента ИЛИ. 6 k. Демодулятор по п. 2, отличающийся тем, что каждый дискриминатор содержиТ элемент И и два D-триггера, выходы которого подключены к входам элемента И, выход которого и второй выход второго 0-триггера являются выходами дискриминатора, входами которого являются соответствующие входы О-триггеров. 5. Демодулятор по п. 2, отличающийся тем, что решающий блок содержит элемент И и последовательно соединенные первый и второй элементы ИЛИ, причем входы элемента И и.первого элемента ИЛИ являются входами решающего блока, выходами которого являются выход элемента И и выход второго элемента ИЛИ, второй вход которого соединен с выходом элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР (Г 605332, кл. Н L 27/18, 1976.

«ммммммм

w-rr

$

rr

V

stf

13

rr

ГГ

Mr

Ш.

u Ж

J)t1 13

Tf

иг.г

18-19

It

AftMT

t SMT.

Л

IJW

и

14

Tffxm.

./

/

/AV:

Mf 94.f

Itm.

SS.I

J

IftfM.

Авторы

Даты

1982-05-07—Публикация

1980-04-04—Подача