1 13224122

Изобретение относится к радиотех-в,г,д,е) поступают на первые входы

нике и используется в радиосвязи,элементов И -- на вторые входы

радиотелеграфии и проводных системахкоторых поступают приходящий ЧМНФ

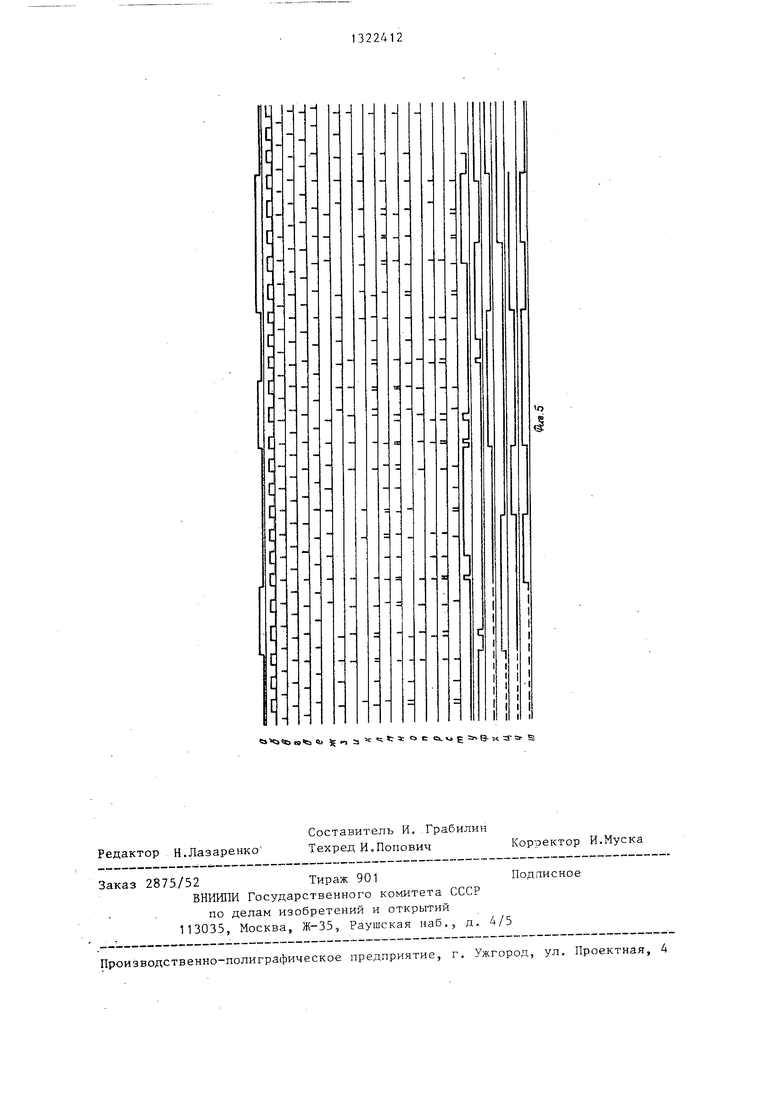

передачи данных для обработки час-сигнал (фиг. 5,8,6). тотно-манипулированных с непрерывной Процедура демодуляции производитфазой (ЧМНФ) сигналов.ся в два этапа. Это связано с тем,

Цель изобретения - повышение поме-что на приемной стороне имеет место

хоустойчивости..неопределенность начальной фазы (О

На фиг. 1 представлена структур-или П) приходящего сигнала. Поэтоная электрическая схема цифрового ко- tOму на первом этапе определяется нагерентного частотного демодулятора;чальная фаза 0 приходящего сигнала

на фиг. 2 - структурная электричес-по алгоритму

кая схема формирователя пачки сдвину- . . „ „ ,. .

. А-, ; +А -,, +Б 1 ; +В, . -(.А. - т-Д, .,.+

тых ВО времени импульсов-, на фиг.З - „ ДгЛ

структурная электрическая схема ком- 15 2,i 7., мутатора; на фиг. 4 - структурная где , А, . - корреляционные электрическая схема решающего бло- значения на i-м и (i+1)-M тактовых ка; на фиг. 5 - временные диаграммы интервалах для опорной частоты fо,, , напряжений, поясняюш,их работу цифро- и 6 О, В , , В ;. - корреляционные вого когерентного частотного демодуля-20 значения на i-м и (1+1)-м тактовых тора.интервалах для опорной частоты fon.2

Цифровой когерентньй частотный де- и Э Л , Aj, , - В, , Bj - модулятор содержит (фиг.1) формирова- аналогичные значения корреляционных тели 1 и 2 опорного сигна-па, опорньш интегралов, но для 6 Д , генератор 3, элементы И 4.,-А, блок 25 Корреляционные значения (1) полу- 5 тактовой синхронизации, формирова- чаем на выходах реверсивных счетчи- тель 6 пачки сдвинутых во времени им- ков 9 и 9 (фиг.5, у, ф). пульсов, элементы ИТШ 7 и 7 , комму- На втором этапе производится соб- татор 8, реверсивные счетчики (PC) ственно демодуляция приходящего 9 и 9 , дополнительные реверсивные 30 ЧМНФ сигнала с учетом апосторифной счетчики (ДРС) 9 и 9, элементы 10 информации о начальной фазе, получа- и lOj Задержки и решакаций блок 11. емой согласно алгоритму (1). При этом

Формирователь б содержит (фиг.2) обработка начинается с (i+1)-ro так- инверторы 12 -12g5 элементы И тового интервала и определяется сим- 13,, элементы И-НЕ 14 и 14, элемент вол на (1+1)-м тактовом интервале по 15 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ результатам обработки на двух такто- 16, счетчик 17, дешифратор 18. вых интервалам по алгоритму.

Коммутатор 8 содержит (фиг.З) элементы ИЛИ , элементы 2И-ИЛИ 2(А, j,-В , ;. )+(А, . -ьВ,)- и элемент 21 задержки. 40 сл +R П О)

Решающий блок 11 содержит (фиг.4) i, i. -t

элемент 2И-Ш1И 22, элементы ИСКЛЮЧАЮ- Корреляционные значения (2) полу- ЩИЕ ИЛИ 23 и 23,,, элемент 24 задерж- чаем на выходах дополнительных ревер- ки инвертор 25, Ь-триггер 26.сивных счетчиков 9, и 9. Так как

Цифровой когерентный частотный де- принятие решения о символе (i+1)-ro модулятор работает следующим образом. тактового интервала производится в

Б двух каналах производится корре- конце (i+2)-ro тактового интервала, ляционная обработка приходящего ЧМНФ то для корреляционных значений (1) сигнала с индексом манипуляции 0,5. необходима задержка на тактовый ин- Каждьй из корреляторов содержит циф- Q тервал, которая производится элемен- ровые перемножители - элементы И 4у- тами 10 и 10„ задержки (фиг, 5, х, ц). 4 , подключенные через коммутатор 8 Решения о начальной фазе и символе реверсивные счетчики 9 и 9 и допол- приходящего сигнала производится ре- нительные реверсивные счетчики 9. и шающим блоком 11. Последовательность 9 образуют корреляторы первого и вто- принятия решения и всех функциональ- рого каналов. Опорные сигналы форми- ных операций обеспечивается формиро- руются для каждой из манипулируемых вателем 6 пачки сдвинутых во време- частот формирователями 1 и 2 опорно- ки импульсов (фиг.2), на вход которого сигнала и в противофазе (фиг.З, го поступают счетные импульсы с опор1

3 .13

ного генератора 3 и тактовые импульсы с блока 5 тактовой синхронизации. С первого управляющего выхода формирователя 6 поступает незадержанный тактовый импульс, с второго управля- ющего выхода величина задержки определяется инвертором 12 , С первого по четвертьш установочных выходов производится временная привязка к счетным импульсам опорного генерато- ра 3, которая осуществляется последовательно соединенными элементом И 13 счетчиком 17, дешифратором 18, первый и второй выходы которого подключены к инверторам 12., 12г- а третий выход подключен к второму входу элемента И 13 . Дополнительная временная задержка тактовых импульсов при осуществлении временной привязки к счетным импульсам производится последовательно соединенными элементом 15 задержки и элементом ИСКПЮЧАЩЕЕ ИЛИ 16, при этом тактовые импульсы поступают также непосредственно с выхода инвертора 12j на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и на первые входы элементов И 13 и И-НЕ 14, . Таким образом, временная задержка первого установочного выхода определяется импульсом с выхода, инверто- .ра 124, подключенного к первому входу элемента И 13 , на второй вход которого поступает тактовый импульс с выхода инвертора 12j. Одновременно с выхода инвертора 12 тактовый импульс поступает на первый вход элемента И-НЕ 14 , и временная задержка второго установочного выхода формирователя 6 определяется импульсом с выхода инвертора 12, поступающим на второй вход элемента 14,.Вр еменная задержка третьего установочного выхода формирователя 6 определяется поступающим на второй вход элемента И 13, импульсом с выхода инвертора 12, а задержка четвертого установочного выхода формирователя 6 определяется импульсом с инвертора 12j,поступающим на второй вход элемента И-НЕ 14. . Установочные вькоды форми- рователя 6 производят установку нуля реверсивных счетчиков 9 и 9 и через элементы ИЛИ 7 и 7 дополнительных ре }ерсивных счетчиков 9, и 9 .

Коммутатор 8 (фиг.З) производит коммутацию сигналов с выходов элементов И (фиг.5,ж,3,и,к) на реверсивные счетчики 9 и 9 (фиг.З,

224

JO )5 20 25 3040 - 45 50

.55

124

л,м,н,о) и дополнительные реверсивные счетчики 9, и 9 (фиг. 5,п,р,с,т), причем на реверсивные счетчики 9 и 9j - через элементы ИЛИ 19, 19 коммутатора 8, на суммирующий вход дополнительного реверсивного счетчика 9, - через элемент 21 задержки коммутатора 8. Сигналы на суммирующий и вычитающий входы дополнительного реверсивного счетчика 9 и вычитающий вход дополнительного реверсивного счетчика 9 поступают с выходов элементов 2И-ИЛИ , коммутатора 8 по сигналам управления, поступающим на первые входы элементов 2И-ИЛИ 20 -20, с первого и второго управляющих выходов формирователя 6, а на вторые входы элементов 2И-ИЛИ 20 -20 поступают сигналы с выходов элементов ИЛИ коммутатора 8.

Решающий блок 11 (фиг.4) производит принятие решения о начальной фазе и символах приходящего ЧМНФ сигнала, причем сигналы с вьгходов элементов задержки 10 и 10 поступают на первые входы элемента 2И-Ш1И 22, на вторые входь которого поступает сигнал управления с первого и второго управляющих выходов формирователя 6. Последовательность демодулированных символов (О или 1) с выхода D-триг- гера 26 (фиг.5,ш) определяется сигналами подключенного к D-входу D-триг- гера 26 элемента исключающее ИЖ 23 , первый вход которого подключен к выходу элемента 2 И-ШШ 22, а второй вход подключен к выходу дополнительного реверсивного счетчика 9. (фиг.З, ч),. Переключение D-триггера 26 производится по сигналам на С-входе, который подключен к второму управляющему входу формирователя 6 через последовательно соединенные элемен,т 24 задержки ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и инвертор 25, причем второй вход элемента ИСКЛЮЧАЮЩЕЕ timi 23 подключен непосредственно к второму управляющему входу формирователя 6. Таким образом, посредством дв тсэтапной процедуры принятия решения по алгоритмам (1) и (2) интервал обработки равен трем тактовым интервалам,что повышает помехоустойчивость процедуры демодуляции.

Формула изобретения

Цифровой когерентный частотный демодулятор, содержащий два канала.

5 132241 каждый из которых состоит из формирователя опорного сигнала, первого и второго элементов И и последова-i тельно соединенных реверсивного счетчика и элемента задержки, причем пер- с вьй и второй выходы формирователя опорного сигнала каждого канала соединены соответственно с первьми входами первого и второго элементов И этого же канала, а вторые входы пер- fO вого и второго элементов И обоих каналов объединены и соединены с первым входом формирователей опорных сигналов обоих каналов и являются входом цифрового когерентного частот- f5 ного демодулятора, а также общие для обоих каналов блок тактовой синхронизации, коммутатор и решающий блок, .выход которого является выходом цифрового когерентного частотного демо- 20 дулятора, отличающийся тем, что, с целью повышения его помехоустойчивости, введены формирователь пачки сдвинутых во времени импульсов, первый и второй управляющие выходы 25 которого соединены соответственно с первым и вторьм входа1уги управления коммутатора и соответственно с первым и вторым входами управления решающего блока, опорный генератор, выход ЗО которого непосредственно и через блок тактовой синхронизации соединен соответственно со счетным и сижрони- зирующим входами формирователя пачки сдвинутых во времени импульсов, пер- -,г вый и второй элементы ИЛИ, входы которых соединены соответственно с первым, вторым, третьим и четвертым установочными выходами формирователя пачки сдвинутых во времени импульсов , первый 40 и второй дополнительные реверсивные счетчики, причем выход опорного гене26

ратора соединен со счетными входами формирователей опорного сигнала, управляющие вр 1ходы которых соединены соответственно с первым и вторым синхронизирующими входами блока тактовой синхронизации, выходы первого и второго элементов И первого и второго каналов соединены соответственно с первым, вторым третьим и четвертым информационными входами коммутатора, первый и второй, третий и четвертый, пятый и шестой, седьмой и восьмой информационные выходы которого соответственно соединены с входами сложения и вычитания реверсивных счетчиков первого и второго каналов, второго и первого дополнительных реверсивных счетчи- ков 5 а входы установки нуля реверсивных Счетчиков первого и второго каналов, первого и второго дополнительных реверсивных счетчиков соединены соответственно с третьим и четвертым устано- вечными выходами формирователя пачки сдвинутых во времени импульсов, с выходом первого элемента ИЛИ и с выходом второго элемента ИЛИ, при этом входы синхронизации элементов задержки первого и второго каналов соединены соответственно с первым и вторым уста новочными выходами формировате/1Я пачки сдвинутых во времени импульсов разрядные выходы первого дополнительного реверсивного сЧетчика соединены с информационными входами второго дополнительного реверсивного счетчика, а выходы элементов задержки первого и второго каналов и выход второго дополнительного реверсивного счетчика соединены соответственно с первым и вторым сигнальными входами и информационным входом решающего блока.

n-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска шумоподобных сигналов | 1983 |

|

SU1125751A1 |

| Цифровой когерентный частотный демодулятор | 1981 |

|

SU985967A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| СИСТЕМА РАДИОСВЯЗИ | 1999 |

|

RU2168864C2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Устройство для измерения ошибки сведения лучей цветного кинескопа | 1987 |

|

SU1497767A1 |

| Устройство для обработки сигналов допплеровского измерителя скорости | 1979 |

|

SU873175A2 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости. Демодулятор содержит формирователи 1 и 2 опорного сигнала, опорный г-р 3, эл-ты И 4, блок 5 тактовой синхронизации, формирователь 6 пачки сдвинутых во времени импульсов, эл-ты ИЛИ 7, коммутатор 8, реверсивные счетчики 9, эл-ты задержки 10 и решающий блок 11. В двух каналах демодулятора производится корреляционная обработка приходящего частотно-манипулированного с непрерывной фазой сигнала. Процедура демодуляции производится в два этапа. Посредством двухэтапной процедуры принятия решения по заданным алгоритмам интервал обработки равен трем тактовым интервалам, что повышает помехоустойчивость процедуры демодуляции. Даны ил. выполнения формирователя 6, коммутатора 8 и решающего блока 11. 5 ил. (Л со to to 4: to

Фиг л

с

««и, (S) к,з «:« 1 г «: а.чЕа,©..я-а-а

Редактор Н.Лазаренко

Составитель И, Грабилин

Техред И.Попович Корректор И.Муска

Заказ 2875752Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-355 Раушская наб., д, А/5

п.. .,.... -------------- ------------------------ ---- --- ------------- - -- - Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1

о

Авторы

Даты

1987-07-07—Публикация

1984-10-18—Подача