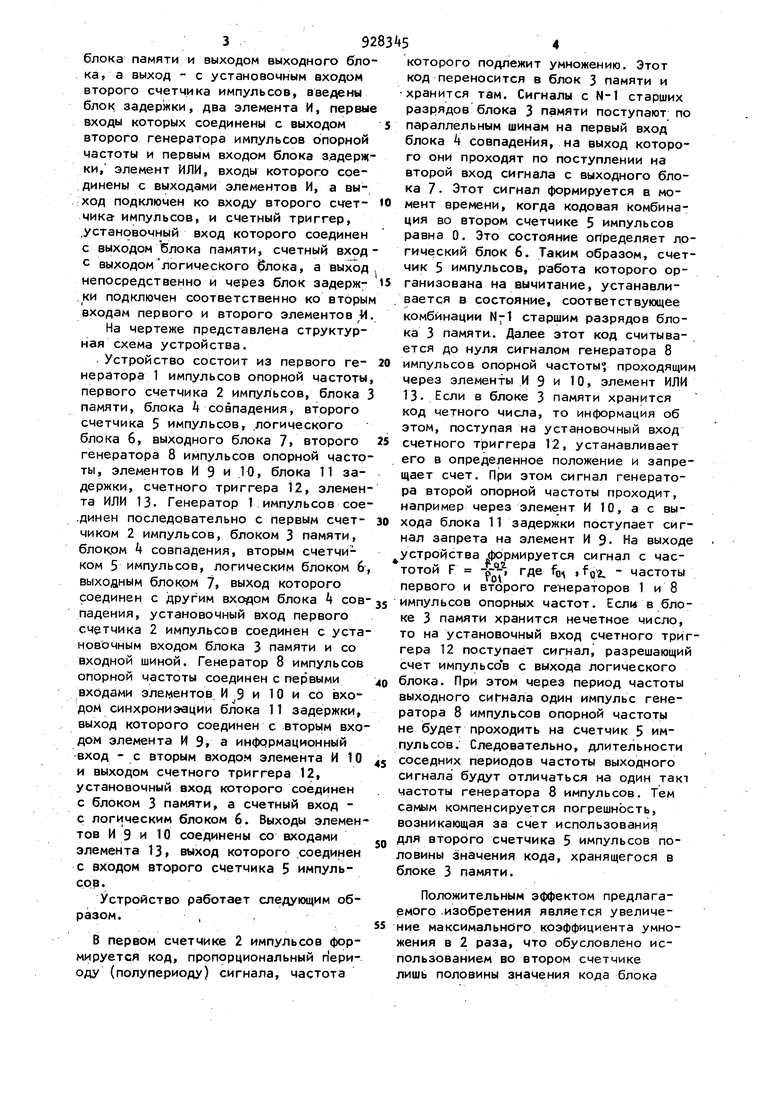

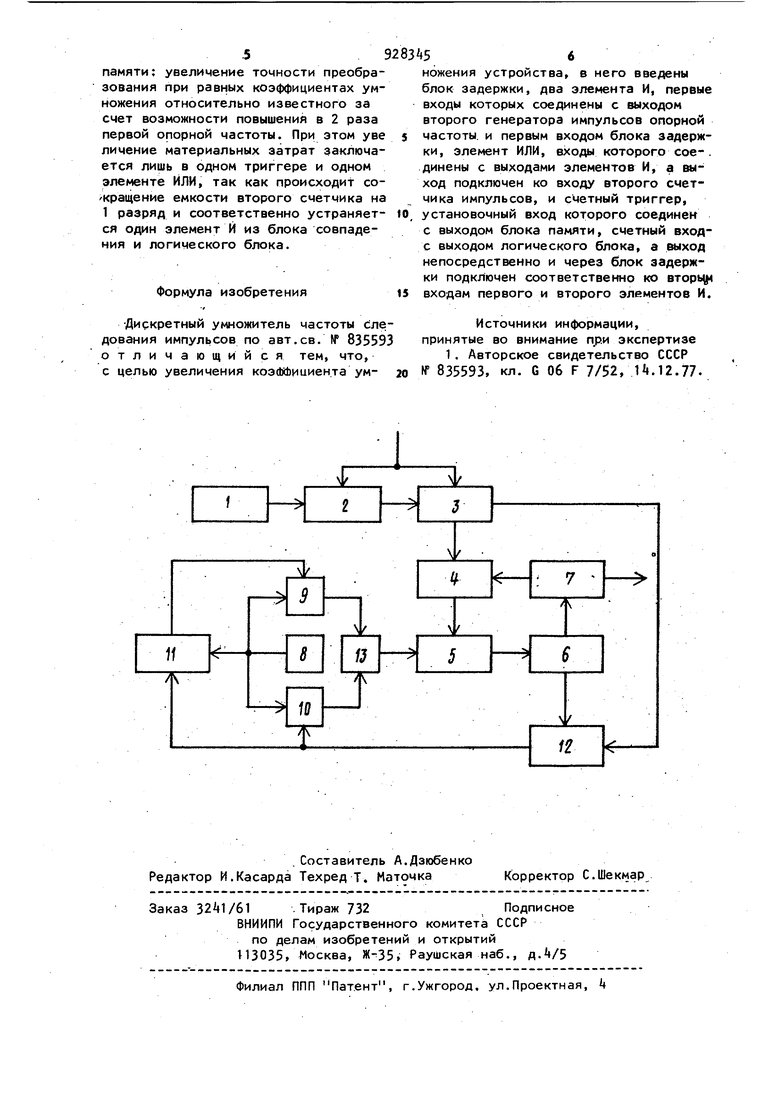

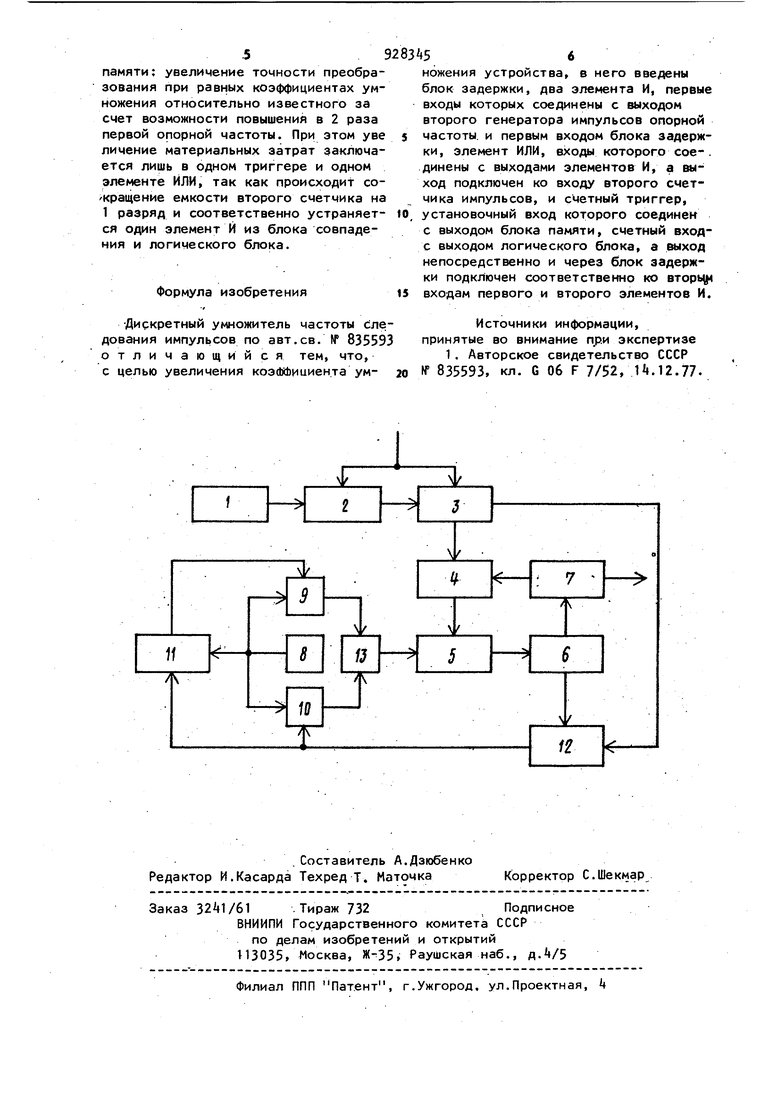

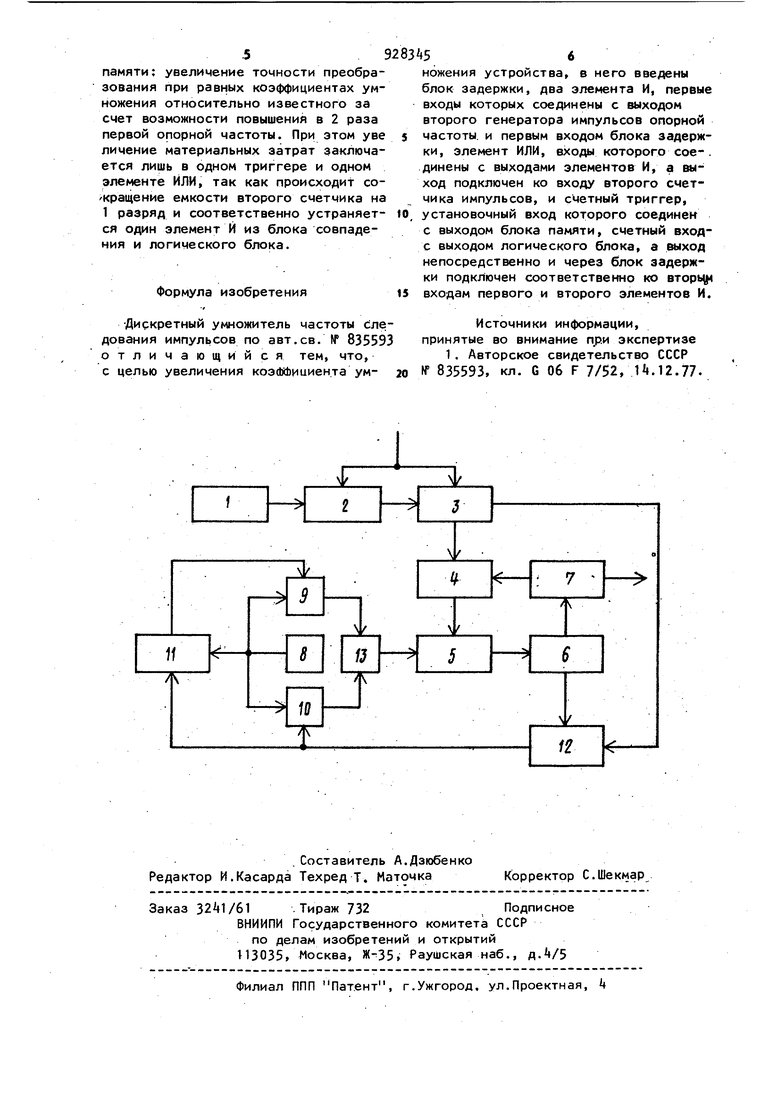

Изобретение предназначено для использования в системах автоматики и контрольно-измерительной техники, в частности для увеличения девиации частоты следования импульсов в системе контроля. По основному авт.св. № 835593 известен дискретный умножитель, частоты следования импульсов, содержащий первый и второй генератор импульсов опорной частоты, выходы ко торых подключены соответственно к выходам первого и второго счетчиков импульсов, блок памяти, управляющий вход которого соединен с установочным входом первого счетчика импульсов и со входной шиной, а вход - с, выходом первого счетчика импульсов, и выходной блок, вход которого через логический блок соединен с выходом второго счетчика импульсов, и блок совпадения, входы которого соединены с выходом блока памяти и выходом выходного блока, а выход - с установоч ным входом второго счетчика импульсов Недостатком этого устройства является ограниченность коэффициента умножения частоты, определенного отношением опорных частот и ограниченного необходимой точностью преобразоват ния и быстродействием элементной базы. Цель изобретения - увеличение коэффициента умножения устройства. Поставленная цель достигается тем, что в дискретный умножитель частоты следования импульсов, содержащий первый и второй генераторы импульсов опорной частоты, выход первого из которых подключен соответственно ко входу первого счетчика импульсов, блок памяти, управляющий вход которого соединен с установочным входом первого счетчика импульсов и со входной шиной, а вход - с выходом первого счетчика импульсов, и выходной блок, вход которого через логический блок соединен с выходом второго счетчика импульсов, и блок совпадения, входы которого соединены с выходом 392 блока памяти и выходом выходного блока, а выход - с установочным входом второго счетчика импульсов, введены блок задержки, два элемента И, первые входы которых соединены с выходом второго генератора импульсов опорной частоты и первым входом блока з.адерж ки, элемент ИЛИ, входы которого соединены с выходами элементов И, а выход подключен ко входу второго счетчика- импульсов, и счетный триггер, установочный вход которого соединен с выходом блока памяти, счетный входс выходомлогического блока, а выход непосредственно и через блок задерж- 15 КИ подключен соответственно ко вторы входам первого и второго элементов И На чертеже представлена структурная схема устройства. Устройство состоит из первого генератора 1 импульсов опорной частоты первого счетчика 2 импульсов, блока памяти, блока А совпадения, второго счетчика 5 импульсов, логического блока 6, выходного блока 7 второго генератора 8 импульсов опорной часто ты, элементов И 9 и 10, блока 11 задержки, счетного триггера 12, элемен та ИЛИ 13. Генератор 1 импульсов сое .динен последовательно с первым счетчиком 2 импульсов, блоком 3 памяти, блоком Ц совпадения, вторым счетчиком 5 импульсов, логическим блоком 6 выходным блоком 7 выход которого соединен с другим входом блока k сов падения, установочный вход первого счетчика 2 импульсов соединен с уста новочным входом блока 3 памяти и со входной шиной. Генератор 8 импульсов опорной частоты соединен с первыми входами элементов И 9 и 10 и со входом синхронизации блока 11 задержки, выход которого соединен с вторым вхо дом элемента И 9 а информационный вход - с вторым входом элемента И 10 и выходом счетного триггера 12, установочный вход которого соединен с блоком 3 памяти, а счетный вход с логическим блоком 6. Выходы элемен тов И 9 и 10 соединены со входами элемента 13, выход которого соединен с еходом второго счетчика 5 импульсов. Устройство работает следующим образом. , В первом счетчике 2 импульсов формируется код, пропорциональный г{ериоду (полупериоду) сигнала, частота которого подлежит умножению. Этот код переносится в блок 3 памяти и хранится там. Сигналы с N-1 старших разрядов блока 3 памяти поступают по параллельным шинам на первый вход блока 4 совпадения, на выход которого они проходят по поступлении на второй вход сигнала с выходного блока 7. Этот сигнал формируется в момент времени, когда кодовая комбинация во втором счетчике 5 импульсов 0. Это состояние определяет логический блок 6. Таким образом, счетчик 5 импульсов, работа которого организована на вычитание, устанавливается в состояние, соответствующее комбинации Nrl старшим разрядов блока 3 памяти. Далее этот код считывается до нуля сигналом генератора 8 импульсов опорной частоты проходящим через элементы И 9 и 10, элемент ИЛИ 13- Если в блоке 3 памяти хранится код четного числа, то информация об этом, поступая на установочный вход счетного триггера 12, устанавливает его в определенное положение и запрещает счет. При этом сигнал генератора второй опорной частоты проходит, например через элемент И 10, а с выхода блока 11 задержки поступает си|- нал запрета на элемент И 9. На выходе устройства формируется сигнал с частотой F -р, где тo, где Ц ог. частоты первого и второго генераторов 1 и 8 импульсов опорных частот. Если в блоке 3 памяти хранится нечетное число, то на установочный вход счетного триггера 12 поступает сигнал, разрешающий счет импульсов с выхода логического блока. При этом через период частоты выходного сигнала один импульс генератора 8 импульсов опорной частоты не будет проходить на счетчик 5 импульсов. Следовательно, длительности соседних периодов частоты выходного сигнала будут отличаться на один такт частоты генератора 8 импульсов. Тем самым компенсируется погрешность, возникающая за счет использования для второго счетчика 5 импульсов похранящегося в ловины значения кода, блоке 3 памяти. Положительным эффектом предлагаемого .изобретения является увеличение максимального коэффициента умножения в 2 раза, что обусловлено использованием во втором счетчике лишь половины значения кода блока

памяти; увеличение точности преобразования при равных коэффициентах умножения относительно известного за счет возможности повышения в 2 раза первой опорной частоты. При этом уве личение материальных затрат заключается лишь в одном триггере и одном элементе ИЛИ, так как происходит соКращение емкости второго счетчика на 1 разряд и соответственно устраняется один элемент И из блока совпадения и логического блока.

Формула изобретения

Дидкретный умножитель частоты Сле-Источники информации,

дования импульсов по авт.св. № 835593принятые во внимание пр.и экспертизе отличающийся тем, что,1. Авторское свидетельство СССР

с целью увеличения коэсЬФиииента ум- jo№ 835593, кл. G Об F 7/52, f.12.77.

ножения устройства, в него введены блок задержки, два элемента И, первые входы которых соединены с выходом второго генератора импульсов опорной частоты, и первым входом блока задержки, элемент ИЛИ, входы которого сое-. динены с выходами элементов И, а выход подключен ко входу второго сметчика импульсов, и счетный триггер, установочный вход которого соединен с выходом блока памяти, счетный входс выходом логического блока, а выход непосредственно и через блок задержки подключен соответственно ко вторц)4 входам первого и второго элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Устройство для определения объемного расхода жидкости | 1989 |

|

SU1723440A1 |

| Устройство для масштабирования марок времени при обработке сейсмической информации | 1980 |

|

SU962966A1 |

| Устройство для диагностирования шин | 1987 |

|

SU1444640A1 |

| Устройство для дискретного регулирования разности фаз сигналов | 1977 |

|

SU721767A1 |

| Устройство для суммирования частотно-импульсных сигналов | 1977 |

|

SU708361A1 |

| Умножитель частоты следования импульсов | 1974 |

|

SU513510A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭЛЕКТРОМАГНИТНОЙ ОБСТАНОВКИ | 1995 |

|

RU2126975C1 |

Авторы

Даты

1982-05-15—Публикация

1980-01-07—Подача