(5) ЦИФРОВОЙ УМНОНИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Цифровой умножитель частоты следования импульсов | 1984 |

|

SU1226604A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство отождествления | 1991 |

|

SU1803910A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

1

Изобретение относится к автоматике, контрольно-измерительной и вычислительной технике и может быть, в частности, использовано для формирования сетки опорных сигналов в устройстве проверки преобразователя кодов

Известен дискретный умножитель частоты, содержащий два генератора опорных частот, генератор переменной частоты, два счетчика импульсов, запоминающее устройство, ()лок ср авнения кодов, буферное устройство,- селектор режимов работы 1.П .

Недостатками такого умножителя частоты являются сложность конструкции, обусловленная наличием блока сравнения кодов, низкая точность умножения частоты, связанная с отсутствием коррекции выходного сигнала.

Известен также дискретный умно хитель частоты, содержащий два генератора опорной частоты, два счетчика

импульсов, блок памяти, дифференцирующий блок, блок сравнения кодов и элемент ИЛИ. Наличие дифференцирующего блока и элемента ИЛИ повышает точность умножения частоты 12 ,

Однако наличие в нем блока сравнения кодов обусловливает сложность конструкции. ,.

Наиболее близким к предлагаемому является цифровой умножитель

10 частоты, содержащий первый и второй делители частоты, генератор опорной частоты, первый и второй счетчик, регистр, дешифратор нуля, элементы И, причем выход генератора опорной

15 частоты соединен с информационным входом первого делителя частоты, выход которого соединён с счетным входом первого счетчика, выходы разрядов которого соединены с вхо20дами разрядов регистра, выходы разрядов которого соединены с управляющими входами второго делителя частоты, выходы разрядов первого

делителя частоты соединены с входами разрядов второго счетчика, выходы разрядов которого соединены со: входами дешифратора нуля, инверсный и прямой выходы которого соедииены с первыми входами первого и второго элементов И, соответственно выход первого из которых соединен со счетным входом второго счетчика, вход цифрового умножителя частоты соединен с входом записи регистра, установочными входами первого и второго счетчиков и входом выдачи разрядных значений первого делителя частоты, при этом второй делитель частоты содержит счетчик, схему сравнения и буферный формиро-, ватель импульсов, первый выход которого является выходом второго делителя частоты и соединен с выходом цифрового умножителя частоты, и второй, выход - с вторыми входами элементов И, счетный вход счетчика второго дeлиteля частоты является информационным входом второго делителя частоты и соединен с выходом генератора опорной частоты, выходы разрядов счетчика второго делителя частоты соединены с входами первой группы схемы сравнения, входы второй группы которой соединены с управляющими входами второго делителя частоты, а выход подключен ко входу буферного формирователя импульсов, выходы первого и второго элементов И соединены с входами установки счетчика второго делителя частоты в состояние -1 и О соответственно 3 Недостатком этого цифрового умножителя частоты является его сложность, связанная со сложностью исползуемого в нем довольно специфичного второго .делителя частоты.

Цель изобретения - упрощение конструкции цифрового умножителя частоты.

Поставленная цель достигается тем что цифровой умнох итель частоты, содерма1 |йй первый и второй делители частоты, генератор опорной частоты, первый и второй счетчики, регистр, элемент И, дешифратор нуля, причем выход генератора опорной частоты сое динен с информационным входом первого делителя частоты, выход которого соединен с счетным входом первого счетчика, выходы разрядов которого соединены с входами разрядов регистра, выходы разрядов которого соединены с управляюи1ими входами второго делителя частоты, выходы разрядов первого делителя частоты соединены с входами разрядов второго счетчика, выходыразрядов которого, соединены с входамидешифратора нуля выход которого соединен с первым входом элемента И, выход которого соеди;нен с счетным входом второго счетчика, вход цифрового умножителя частоты соединен с входом записи регистра, установочными входами первого и второго счетчиков и входом выдачи разрядных значений первого делителя .частоты, при этом второй делитель частоты содержит сметчик и буферный формирователь импульсов, первый выход которого является выходом второго делителя частоты и соеДинен с выходом цифрового умножителя частоты, а счетный вход счетчика является информационным входом второго делителя частоты и соединен с выходом генератора опорной частоты, нулевые установочные входы разрядов счетчика второго делителя частоты соединены с выходом элемента И, дополнительно содержит D-триггер, информационный вход которого соединен с выходом дешифратора нуля, нулевой установочный вход - с выходом второго делителя частоты, тактовый вход - с выходом генератора опорной частоты, а выход - с вторым входом элемента И, кроме того, второй делитель частоты содержит дешифратор нуля и группу элементов И, первые входы которых соединены с управляющими входами второго делителя частоты, вторые входы - с вторым выходом буферного формирователя импульсов, а выходы соответственно с единичными установочными входами разрядов счетчика второго делителя частоты,/ выходы разрядов этого счетчика соединены с входами дешифратора нуля второго делителя частоты, выход дешифратора нуля второго делителя частоты соединен с входом буферного формирователя импульсов, при этом в разряде счетчика второго делители частоты использованы триггеры, имеющие при одновременной подаче сигналов на единичный и нулевой установочные входы сигналы на прямом и инверсном выходах.

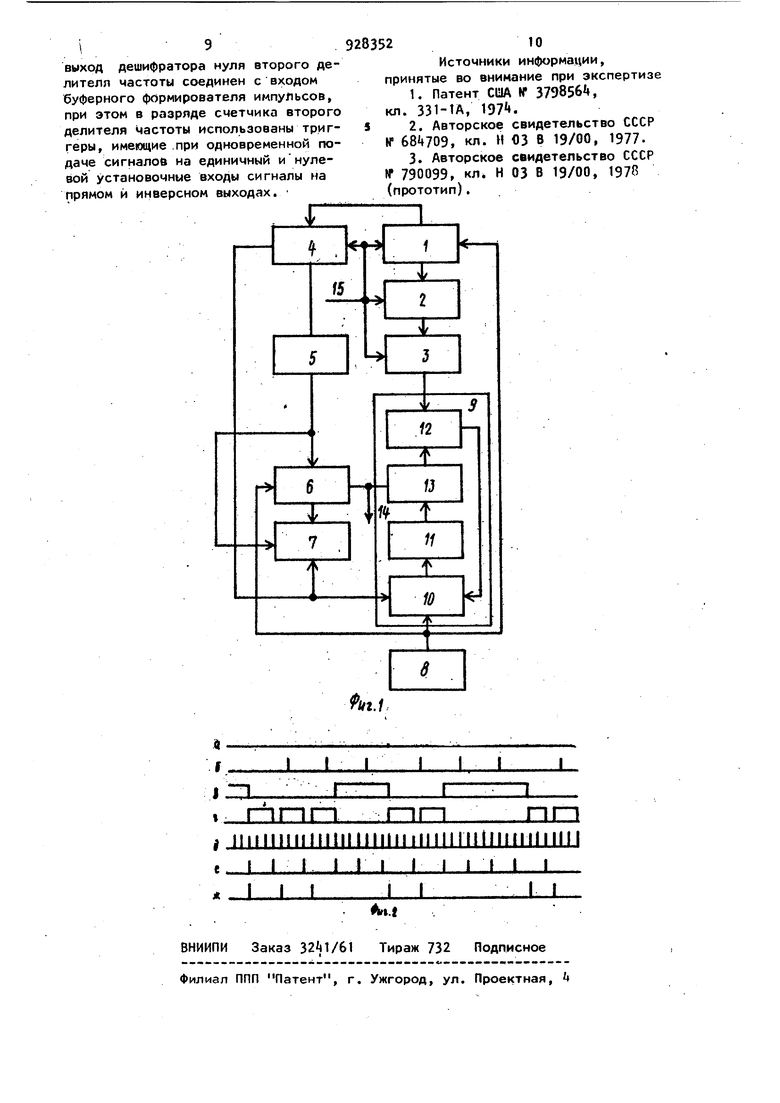

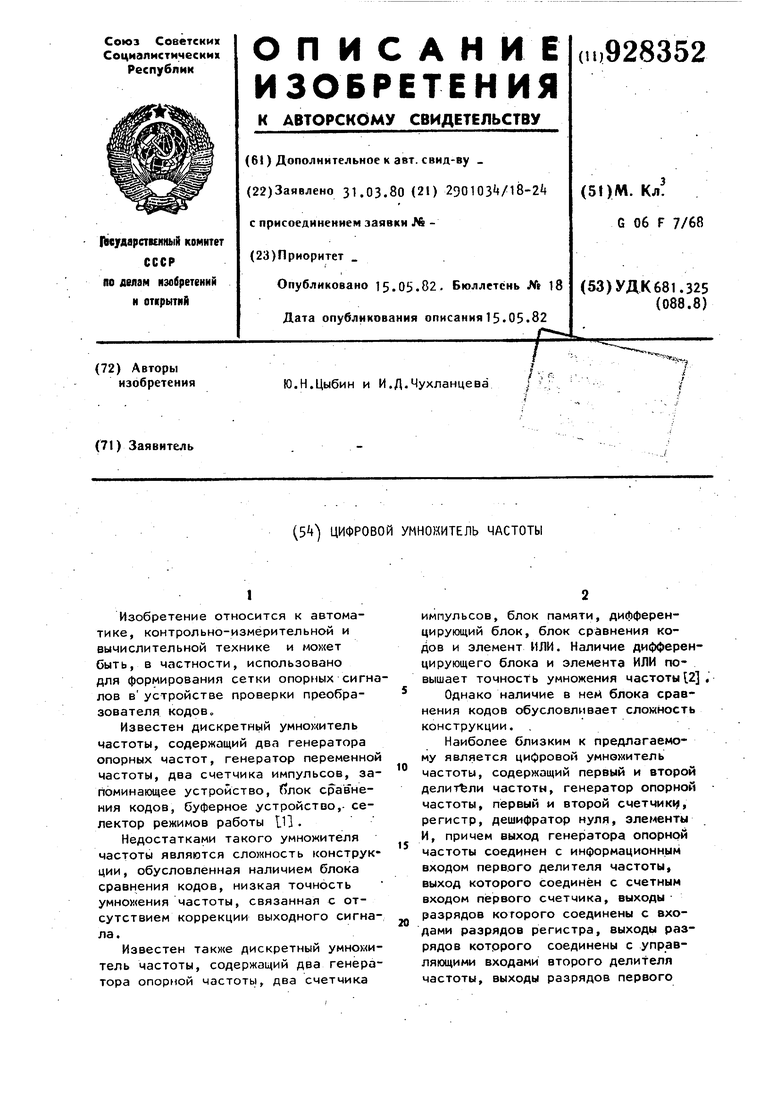

На фиг.1 представлена структурная схема цифрового умножителя частоты; .на фиг. 2 - диаграммы его работы. Цифровой умножитель частоты соде жит делитель 1 частоты, счетчик 2, регистр 3| счетчик k, дешифратор 5 нуля, D-триггер 6, элемент И 7, ген ратор 8 опорной частоты, делитель 9 частоты, содержащий счетчик 10, дешифратор 11 нуля, группу элементов И 12, буферный формирователь 13 импульсов. Выход генератора 8 соединен с входами делителей 1 и 9 часто ты, выходы которых соединены с счетным входом счетчика 2 (примирую щего) и выходом И цифрового умножителя частоты, соответственно выходы разрядов счетчика 2 соединены с входами разрядов регистра 3. выходы разрядов которого соединены с управляющими входами делителя 9 частоты. Выходы разрядов делителя 1 частоты (выполненного на счетчике) соединены с входами разрядов счетчика k (вычитающего) , выходы разрядов которого подключены к входам ;дешифратора 5 нуля, инверсный выход которого подключен к информационному (О-входу) D-триггера 6 и входу элемента И 7, ДРУгой вход которого соединен с выходом D-триггера 6, нулевой установочный (R-) вход которого соединен с выходом делителя 9 частоты, а тактовый (Свход - с выходом генератора 8, Счет ный вход счетчика и нулевой установочный вход счетчика 10 (вычитающего) соединены с выходом элемента И 7- Счетный вход счетчика 10 соединен с выходом генератора 8, а выходы разрядов счетчика 10 - с вхо дами дешифратора 11 нуля, выход которого подключен к входу формирователя 13, один выход которого подключен к выходу делителя 9 частоты, а другой - к входам элементов И 12, другие входы которых соединены с управляющими входами делителя 9 час тоты, а выходы - с установочными входами разрядов счетчика 10. Вход 15 цифрового умнокштеля час тоты подключен к входу записи регистра 3, установочным входам счетчиков 2 и 4 и входом выдачи разрядных значений делителя 1 частоты. Цифровой умножитель частоты работает следующим образом. При поступлении сигнала, частота которого подлежит умножению, на вхо 15 в счетчике 2 формируется код, пропорциональный периоду следования импульсов входного сигнала (фиг.2,а). Этот код заносится в регистр 3 и хранится там. Опорным сигналом для счетчика 2 служат импульсы (фиг,2,б) с выхода делителя 1 частоты, выполненного в виде счетчика импульсов с переполнением. В делителе 1 частоты, коэффициент деления которого определяет коэффициент умножения N устройства, также формируется код, пропорциональный погрешности измерений периода следования импульсов входного сигнала счетчиком 2. Этот крд, который может изменяться в пределах от О до N, по поступлении входного сигнала записывается в счетчик k, работающий на вычитание и предназначенный для коррекции периода следования импульсов выходного сигнала цифрового умножителя частоты,обеспечивающий повышение точности преобразователя частотц. В момент«формирования в счетчике 10, работающем на вычитание, нулевой кодовой комбинации дешифратор 11 вырабатывает Потенциал разрешения, который через формирователь 13 поступает на соответствующие входы элементов И 12, .разрешая запись кода с регистра 3 в счетчик 10. Далее код считывается до нуля и процесс повторяется. Коррекция периода выходного сигнала осуществляется следующим образом. При наличии в счетчике f ненулевой кодовой комбинации, соответствующей ошибке измерения периода входного сигнала счетчиком 2, дешифратор 5 вырабатывает сигнал, например низкого уровня (фиг.2,в), поступающий на информационный вход D-триггера 6. В момент формирования выходного импульса цифрового умножителя частоты (фиг.2,е), последний поступает с Ьыхода формирователя 13 на вход установки D -триггера 6 в нулевое состояние. Выходной сигнал b -триггера 6 через элемент И 7 поступает на входы установки в нуль счетчика. 10, на входы установки в единицу которого в это время воздействуют сигналы с выходов элемен тов И 12. Такая запрещенная комбинация установочных сигналов переводит счетчик 10.в состояние неопределенности. Однако счетчик 10 при этом находится в статическом состоянии и не реагирует на счетные импульсы (фиг. 2,д) генератора В опорной частоты. Это состояние длится в течение одного периода сигнала генератора 8, так как по заднему фронту первого его импульса после установки D -триггера 6 в нулевое состояние, последний опрокидывается в состояние единичного уровня (фиг;2,г), вследствие чего снимается состояние неопределенности счет чика -10 и в него записывается установочный код с регистра 3. Таким образом, при этом осуществляется задержка формирования кода в счетчике 10 на один период генератора 8 ; опорной частоты (фиг.2,ж). Перепад потенциала И -триггера 6 фиксируется также счетчиком 4, код которого уменьшается при этом на единицу Далее процесс повторяется до тех пор, пока в счетчике t не образуется нулевая кодовая комбинация. При этом на выходе дешифратора Б формируется сигнал высокого уровня, поступающий на вход элемента И 7, на выходе которого появляется сигнал, разрешающий работу счетчика 10 без задерж ки. С поступлением очередного импуль са входного сигнала (фиг.2,а) процес повторяется. Преимуществами предлагаемого цифрового умножителя с{астоты по сравнению с известным являются упрощение конструкции, что обусловлено заменой ,D составе второго делителя частоты блока сравнения кодов на группу элементов И и дешифратор нуля. Данный эффект достигается за счет того что блок сравн ения кодов требует для своей реализации Зп двухвходовых элементов И-НЕ и п-входового элемента И. В предлагаемом умножителе функцию дополнительного дешифратора выполняет п-входовый элемент И, а группа элементов И состоит из п двух входовых элементов .И. Таким образом экономится 2п двухвходовых логических элементов Указанные преимущества достигаются при сохранении точностных характеристик известного умножителя частоты . Формула изобретения Цифровой умножитель частоты, содерхощий первый и второй делители частоты, генератор опорной частоты, первый и второй счетчики, регистр, элемент И, дешифратор нуля, причем выход генератора опорной частот-ы соединен с информационным входом первого делителя частоты, выход которого соединен со счетным входом первого счетчика, выходы разрядов которого соединены с входами разрядов регистра, выходы разрядов которого соединены с управляющими входами второго делителя частоты, выходы разрядов первого делителя частоты соединены с входами разрядов второго счетчика, выходы разрядов которого соединены с входами дешифратора нуля, выхрд которого соединен с первым входом элемента И, выход которого соединен со счетным входом второго счетчика, вход цифрового умножителя частоты соединен с входом записи регистра, установочными входами первого и второго счетчиков и входом выдачи разрядных значений первого делителя частоты, при этом второй делитель частоты содержит счетчик и буферный формирователь импульсов, первый выход которого является выходом второго делителя частоты и соединен с выходом цифрового умножителя частоты, а счетный вход счетчика является информационным входом второго делителя частоты и соединен с выходом генератора опорной частоты, нулевые установочное входы разрядов счетчика втораго делителя частоты соединены с выходом элемента И, отличающийся тем, что, с целью упрощения конструкции, цифровой умножитель частоты содеркит D -триггер, информационный вход которого соединен с выходом дешифратора нуля, нулевой установочный вход - с выходом второго делителя частоты, тактовый вход - с выходом генератора опорной частоты, а выход - с вторым входом элемента И, кроме того, второй делитель частоты содеркшт дешифратор нуля и группу элементов И, первые входы которых соединены с управляющими входами второго делителя частоты, вторые входы - с вторым выходом буферного формирователя импульсов, а выходы - соответственно с единичными установочными входами разрядов счетчика второго делителя частоты, выходы разрядов этого счетчийа соединены с входами дешифратора нуля второго делителя частоты.

выход дешифратора нуля второго делителя частоты соединен с входом буферного формирователя импульсов, при этом в разряде счетчика второго делителя частоты использованы триггеры, имеющие .при одновременной подаче сигналов на единичный инулевой установочные входы сигналы на прямом и инверсном выходах.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-05-15—Публикация

1980-03-31—Подача