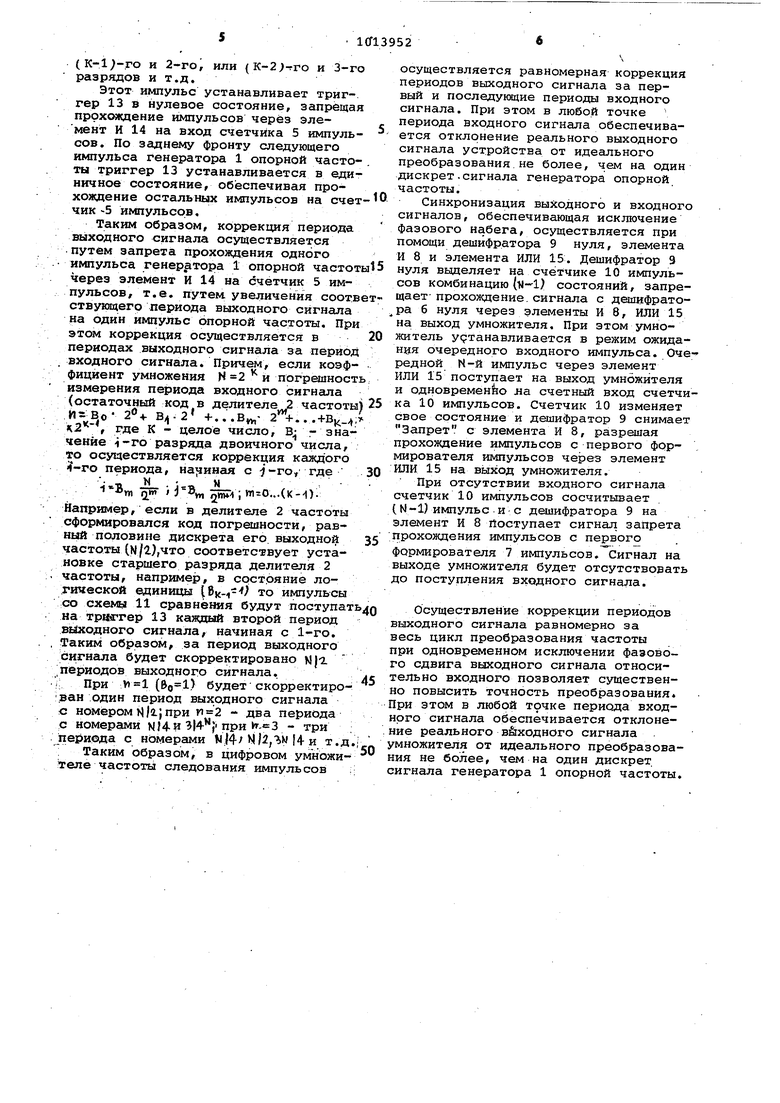

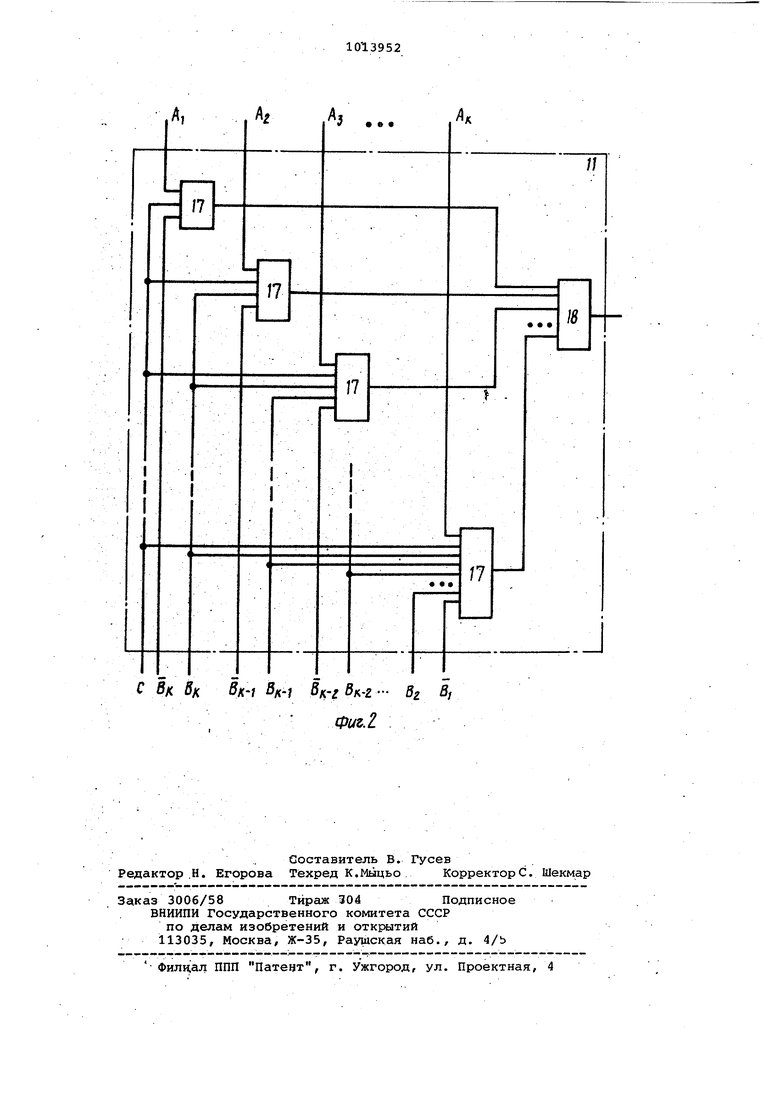

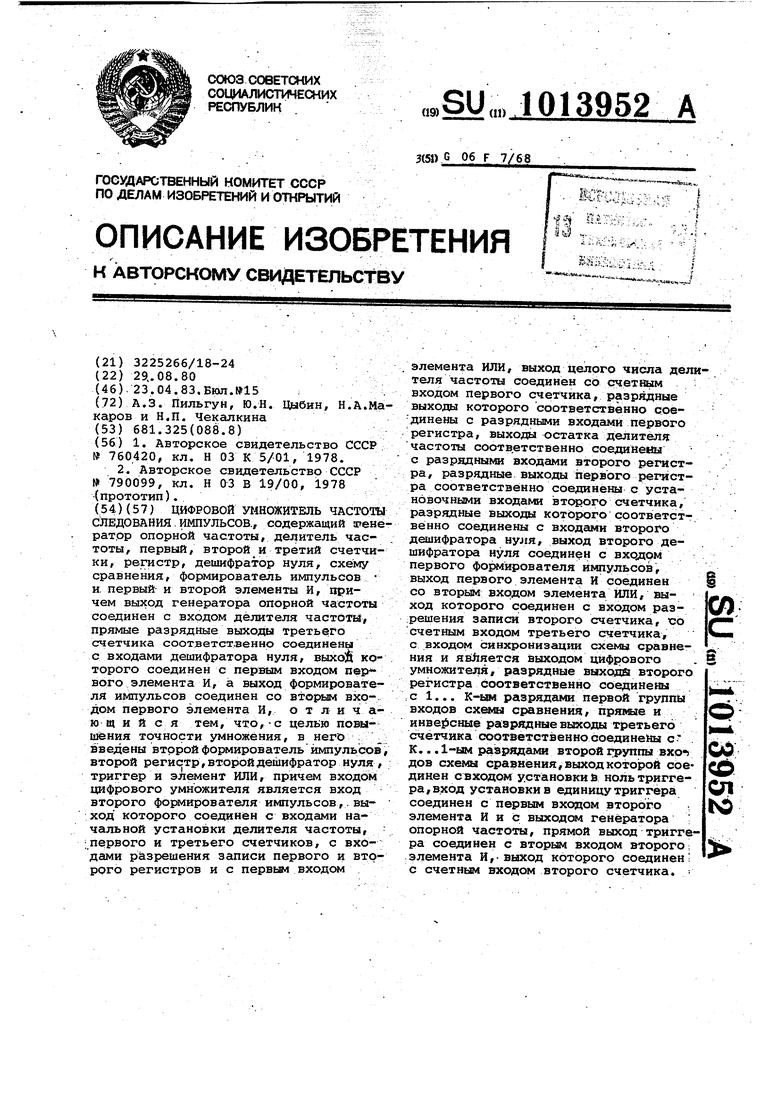

Изобретение относится к автомати и вычислительной технике и может бы использовано, в частности, в устрой ствах проверки точности преобразова ния угол - код. Известен умножитель частоты, содержащий входной формирователь импу сов, блок управления, первый и втор делители частоты, схему сравнения, первый, второй и третий счетчики, триггер, элементы И, ИЛИ 1J. Недостатком умножителя является отсутствие промежуточного блока памяти кода умножения, в результате чего происходит потеря информации об изменении частоты входного сигна ла. Наиболее близким к предлагаемому является цифровой умножитель частоты следования импульсов, содержащий генератор опорной частоты, делитель частоты, первый, второй и третий счетчики, регистр,, дешифратор нуля, cxeiviy сравнения, формирователь импульсов и первый и второй элементы И, причем выход генератора опорной частоты соединен с входом делителя частоты, прямые разрядные выходы третьего счетчика соединены с входами дешифратора нуля, выход которого соединён с первым входом первого элемента И, а выход формирователя . импульсов соединен со вторым входом первого элемента И . Недостатком данного умножителя является недостаточно высокая точт ность преобразования, поскольку коррекция выходных сигналов осуществляется лишь в первых у периодах выходного сигнала и - погрешность измерения входного сигнала). Кроме того,1в связи с неравномерностью кор рекции, образуется фазовый сдвиг выходного сигнала относительно входного внутри периода выходного сигнала. Целью изобретения является повышение точности умножения частоты Поставленная цель достигается тем что в цифровой умножитель частоты следования импульсов, содержащий генератор опорной частоты, делитель частоты, первый, второй и третий счетчики, регистр, дешифратор нуля, схему сравнения, формирователь импульсов и первый и второй элементы И причем выход генератора опорной частоты соединен с входом делителя частоты, прямые разрядные выходы тре тьего счетчика соединены с входами дешифратора нуля, выход которого сое динен с первым входом первого элемента И,а Ьнход формирователя им-. пульсов соединен со вторым входом первого элемента И, введены второй формирователь импульсов,второй регист второй дешифратор, нуля, триггер и эл мент ИЛИ, причем входом цифрового умножителя является вход второго формирователя импульсов, выход которого соединен с входами начальной установки делителя частоты, первого и третьего счетчиков, с входами разрешения записи первого и второго регистров и с первым входом элемента ИЛИ, выход целого числа делителя частоты соединен со счетным входом первого счетчика, разрядные выходы которого соответственно соединены с разрядными входами первого регистра, выходы остатка делителя частоты соответственно соединены с разрядными входами второго регистра, разрядные выходы первого регистра соединены соответственно с установочными входами второго счетчика, разрядные выходы которого соответственно соединены с входами второго дешифратора нуля, выход второго дешифратора нуля соединен со входом первого формирователя импульсов, выход первого элемента И соединен со вторым входом элемента ИЛИ, выход которого соединен с входом разрешения .записи второго счетчика, со счетным входом третьего счетчика, с входом синхронизации схемы сравнения и является выходом цифрового умножителя, разрядные выходы второго регистра соответственно соединены с 1...К-ым разрядами первой группы входов схемы сравнения, и инверсные разрядные выходы третьего счетчика соответст- венно соединены с К...1-ым разрядами второй группы входов схемы сравнения, выход которой соединен с входом установки в ноль триггера, вход установки в единицу триггера соединен с первым входом второго элемента И и с выходом генератора опорной частоты, прямой выход триггера соединен со вторым входом второго элемента И, выход которого соединен со счетньом входом второго счетчика. На фиг.1 изображена структурная схема цифрового умножителя частоты следования импульсов на фиг.2 пример выполнения схемы сравнения. Цифровой умножитель частоты следования импульсов содержит генератор 1 опорной частоты, делитель 2 .частоты, первый счетчик 3 (импульсов) , первый регистр 4, второй счетчик 5 (импульсов , первый дешифратор б нуля, первый формирователь 7 импульсов, первый элемент И 8, второй дешифратор 9 нуля, третий счетчик 10 импульсов .схему 11 сравнения,, второй регистр 12, триггер 13, второй элемент И 14, элемент ИЛИ 15 и второй формирователь 16 импульсов, причем выход генератора 1 опорной частоты соединен с первым входом второго элемента И 14, с входом установки в единицу триггера 13 и с входом делителя 2 частоты, входом умножителя является вход второго формирователя 16 импульсов, выход которого соединен с входами начально установки делителя 2 частоты и перво го и. третьего счетчиков 3 и 10 импул сов, с входами разрешения записи пер вого и второго регистров 4,12 и с пе вым входом элемента ИЛИ 15, выход которого является выходом умножителя Выход целого числа делителя 2 час тоты соединен со счетным входом первого счетчика 3 импульсов, разрядные выходы которого соответственно соединены с-разрядными входами первого регистра 4, разрядные выходы первого регистра 4 соответственно соединены с установочными входами второго счет чика 5 импульсов, разрядные выходы которого соответственно соединены с входами первого дешифратора б нуля , выход первого дешифратора б нуля через первый формирователь 7 импульсов соединен со вторым входом первог элемента И 8, выход которого соедине со вторым входом элемента ИЛИ 15, вы ходы остатка делителя 2 частоты соот ветственно соединены с разрядными входами второго регистра 12, разрядные выходы которого соответственно соединены с 1...к-ым разрядами перво группы входов схемы 11 сравнения, прямые и инверсные разрядные выходы третьего счётчика 10 импульсов соответственно соединены с К..,1-ым разрядами.второй группы входов схемы 11 сравнения, выход которой соединен с входомустановки в ноль триггера 13, прямой выход триггера 13 соединен со вторым входом второго элемента И 14, выход которого соединен со счетным входом второго счетчика Б импульсов, прямые выходы третьего счетчика 10 импульсов соответственно соединены с входами второго дешифратора 9 нуля, выход которого соединен с первым входом первого элемента И 8, выход элемента ИЛИ 15 соединен с входом разрешения записи второго счетчика 5 импульсов, со счетным входом третьего счетчика 10 импульсов и с входом синхронизации схемы 11 сравнения. Схема 11 сравнения может, например; содержать К элементов И 17 (по числу разрядов) и многовходовой эле lyieHT ИЛИ 18, причем первые входы К элементов И объединены и соединены С входом синхронизации, вторые входы К элементов И являются первой группой входов схемы 11 сравнения, третьи входы К элементов И являются инверсными разрядами второй группы вхо дов схемы 11 сравнения, остальные j5-l), входы $-го элемента И (..K являются прямыми К... -ыми разрядам второй группы входов схемы 11 сравнения, где t K-S+2. Выходы К элемен- тов И соединенысоответственно, с К входами многовходовогсг элемента ИЛИ, выход которого является выходом схемы 11 сравнения. Умножитель работает следующим образом. На входную шину поступает перио- дический входной сигнал, из которого вторым формирователем 16 импульсов формируются узкие управляющие импульсы, обеспечивающие синхронизацию-работы делителя 2 частоты,счетчиков 3 и 10 импульсов, регистров 4 и 12. Сигнал генератора 1 опорной частоты через делитель 2 частоты поступает на вход счетчика 3 импульсов, в . котором формируется код, пропорциональный периоду входного сигнала. Этот код записывается в регистр 4 и хранится там в течение периода входного сигнала. В счетчик 5 импульсов записывается код предыдущего периода умножаемой частоты, хранившейся в регистре 4. Для обеспечения надежной работы умножителя предпочтительно применение реверсивного счетчика 5 импульсов и дешифратора 6 нуля. В этом случае код, переписанный из регистра 4, считывается до нуля при пометим сигналов генератора 1 опорной частоты, поступающих через элемент И 14 на вычитающий вход счетчика 5, дешифратор б нуля формирует сигнал разрешения записи и далее процесс повторяется. Так как на счетчик 3 импульсов поступает сигнал с частотой в Ы раз меньшей, чем частоты генератора 1 опорной частоты, то на выходе умножителя формируются импульсы, период следования которых в Н раз меньше периода входного сигнала, частота которого подлежитумножению, т.е. коэффициент умножения К умножителя определяется коэффициентом деления делителя 2 частоты. I , По окончании периода входного сигнала в делителе 2 частоты формируется код, пропорциональный ошибке измерения Vi периода входного сигнала счетчиком 3 импульсов. Этот код записывается в регистр 12. Входным сигналом счетчик 10 импульсов устанавливается в исходное состояние, а затем считает выходные импульсы устройства. Формирующийся в счетч.ике 10 К-разрядный код по параллельным шинам подается на вторую группу входов схемы 11 сравнения, на первую группу входов которого поступает К-разрядный код с регистра 12. На выходе схемы 11 сравнения формируется узкий импульс в момент совпадения К-го разряда регистра 12 и 1-го разряда счетчика 10 импульсов или {K-i;-.ro и , или (К-2;-гго и 3-г разрядов и т.д. Этот импульс устанавливает триггер 13 в нулевое состояние, запреща прохс кдение импульсов через элемент И 14 на вход счетчика 5 импуль сов. По заднему фронту следующего импульса генератора 1 опорной часто ты триггер 13 устанавливается в еди ничное состояние, обеспечивая прохождение остальных импульсов на сче чик -5 импульсов. Таким образом, коррекция периода выходного сигнала осуществляется путем запрета прохождения одного импульса генератора 1 опорной часто через элемент И 14 на счетчик 5 импульсов, т.е. путем, увеличения соот ствующего периода выходного сигнала на один импульс опорной частоты. Пр этом коррекция ос1пцествляется в периодах выходного сигнала за период входного сигнала. Причем, если коэф фициент умножения Н 2 и погрешност измерения периода входного сигнала (остаточный код в делителе 2 частоты Иг Во В,)-2 4-...,- 2 +..., , где К - целое число, В г значение i-го разряда двоичного числа, то осуществляется коррекция каждого 4-го периода, начиная с -го/ где N N Ьуп i; тгО-.Дкн). Например, если в делителе 2 частоты сформировался код погрешности, равный половине дискрета его выходной частоты (),что соответствует установке старшего разряда делителя 2 частоты, например, в состояние логической единицы () то импульсы со схемы 11 сравнения будут поступат на Tpiierrep 13 каждый второй период вьа1ходного сигнала, начиная с 1-го. Таким образом, за период выходного сигнала будет скорректировано Nji Iпериодов выходного сигнала. i: При V)l () будет скорректиро.ван один период выходного сигнала с номером /г; при - два периода с номерами ЗК }при и-.з - три периода с номерами N|4 Nl,. 4-и т.д : Таким образом, в цифровом умножителе частоты следования импульсов осуществляется равномерная коррекция периодов выходного сигнала за первый и последующие периоды входного сигнала. При этом в любой точке периода входного сигнала обеспечивается отклонение реального выходного сигнала устройства от идеального преобразования.не более, чем на один дискрет-сигнала генератора опорной частоты. Синхронизация выходного и входного сигналов, обеспечивающая исключение фазового набега, осуществляется при помощи дешифратора 9 нуля, элемента И 8 и элемента ИЛИ 15. Дешифратор 9 нуля выделяет на счётчике 10 импульсов комбинацию (u-lj состояний, запрещает- прохождение.сигнала с дешиФратора б нуля через элементы И 8, ИЛИ 15 на выход умножителя. При этом умножитель устанавливается в режим ожидания очередного входного импульса. Очередной N-й импульс через элемент ИЛИ 15 поступает на выход умножителя и одновременно ла счетный вход счетчика 10 импульсов. Счетчик 10 изменяет свое состояние и дешифратор 9 снимает Запрет с элемента И 8, разрешая прохождение импульсов с первого формирователя импульсов через элемент ИЛИ 15 на выход умножителя. При отсутствии входного сигнала счетчик 10 импульсов сосчитывает (N-1) импульс и с дешифратора 9 на элемент И 8 Поступает сигнал запрета прохождения импульсов с первого формирователя 7 импульсов. Сигнал на выходе умножителя будет отсутствовать до поступления входного сигнала. Осуществление коррекции периодов выходного сигнала равномерно за весь цикл преобразования частоты при одновременном исключении фазового сдвига выходного сигнала относительно входного позволяет существенно повысить точность преобразования. При этом в любой тфчке периода входного сигнала обеспечивается отклонение реального вйходного сигнала умножителя от идеального преобразования не более, чем на один дискрет сигнала генератора 1 опорной частоты.

С Вц BK BK-I BK-I Вк-гВц-г - Вг В,

Фиъ.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты следования импульсов | 1984 |

|

SU1226604A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОВД СЛЕДОВАНИЯ. ИМПУЛЬСОВ., содержащий ренёратрр опорной частоты, делитель час- . тоты, первый, второй и третий счетчики, регистр, дешифратор нуля, схему сравнения, формирователь импульсов и. первый- и второй элементы И, причем выход генератора опорной частоты соединен с входом делителя частота, прямые разрядные выходы третьего счетчика соответственно соединеньа с входами дешифратора нуля, выхоЙ которого соединен с первым входом пер вого элемента И, а выход формирователя импульсов соединен со вторым вхо-. дом первого элемента И, отличают и и с я тем, что,-с целью поклшения точности умножения, в него . : Введены второй формирователь импульсов, второй регистр, второй дешифратор нуля , триггер и элемент ИЛИ, причем входом цифрового умножителя является вход второго формирователя импульсов,.выход которого соедиН1ен с входами начальной установки делителя частоты, г первого и третьего счетчиков, с входами разрешения записи первого и второго регистров и с первым входом элемента ИЛИ, выход целого числа делителя часточы соединен со счетным входом первого счетчика, разрядные выходы которого соответственно соединены с разрядными входгиии первого регистра, выходы остатка делителя частоты соответственно соединены с разрядными входами sTopioro регистра, разрядные выходы первого регистра соответственно соединешл с установочными входами счетчика, разрядные выходы которого соответственно соединены с входами второго дешифратора нуля, выход второго дешифратора нуля соединен с входр первого формирователя импульсов, выход первого элемента И соединен со вторьм входом элемента ИЛИ, выход которого соединен с входом раз:решения записи второго счетчика, хзо счетным входом третьего счетчика, с входом синхронизёщии схемл сравнения и является выходом цифрового умножителя, разрядные выхода второго регистра соответственно соединены Г с 1... К-ым разрядами первой группы входов сх

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 760420, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой умножитель частоты следования импульсов | 1978 |

|

SU790099A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-04-23—Публикация

1980-08-29—Подача