(54) АССОЦИАТИВНЫЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

| Элемент ассоциативной матрицы | 1973 |

|

SU478297A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Элемент памяти ассоциативной запоминающей матрицы | 1985 |

|

SU1265857A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1277211A1 |

Изобретение относится к запоминающим устройствам.

Известен ассоциативный запоминающий элемент, содержащий триггер, адресную шину, элементы управления записью, разрядные шины нуля и единицы, элементы управления считываниек, логический вход и выход ячейки, шину нулевого потенциала, инвертор, восстанавливающий вентиль, логический элемент ИЛИ-НЕ и параллельно соединенные передающие вентили til .

Недостатком известного ассоциативного запоминающего элемента является его сложность.

Наиболее близким техническим решением к данному изобретению является ассоциативный запоминающий элемент, содержащий триггер с двумя входными схемами И, две схемы И считывания информации, схему ИЛИ, схему НЕ, две выходные схемы. И, две выходные схемы ИЛИ, пять входных и пять выходньрс шин 2 .

Недостатком этмо асссадиатнвного запоминающего элемента являются невые сокое быстродействие и надежность вследствие его сложности.

Целью изобретения является повышенве быстродействия и надежности ассоциативного запоминающего элемента.

Поставленная цель достигается тем, что в ассоциативном аапоминаюсием эле менте, содержащем триггер, элементы

10 ИЛИ и элементы И, причем единичный и нулевой входы триггера соединены соот ветственно с выходами первого и второго элементов И, первые входы третьего и четвертого элементов И подключены

IS соответственно к единичному и нулевому выходам триггера, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ, первый вход первого элемента И соединен с первым входом

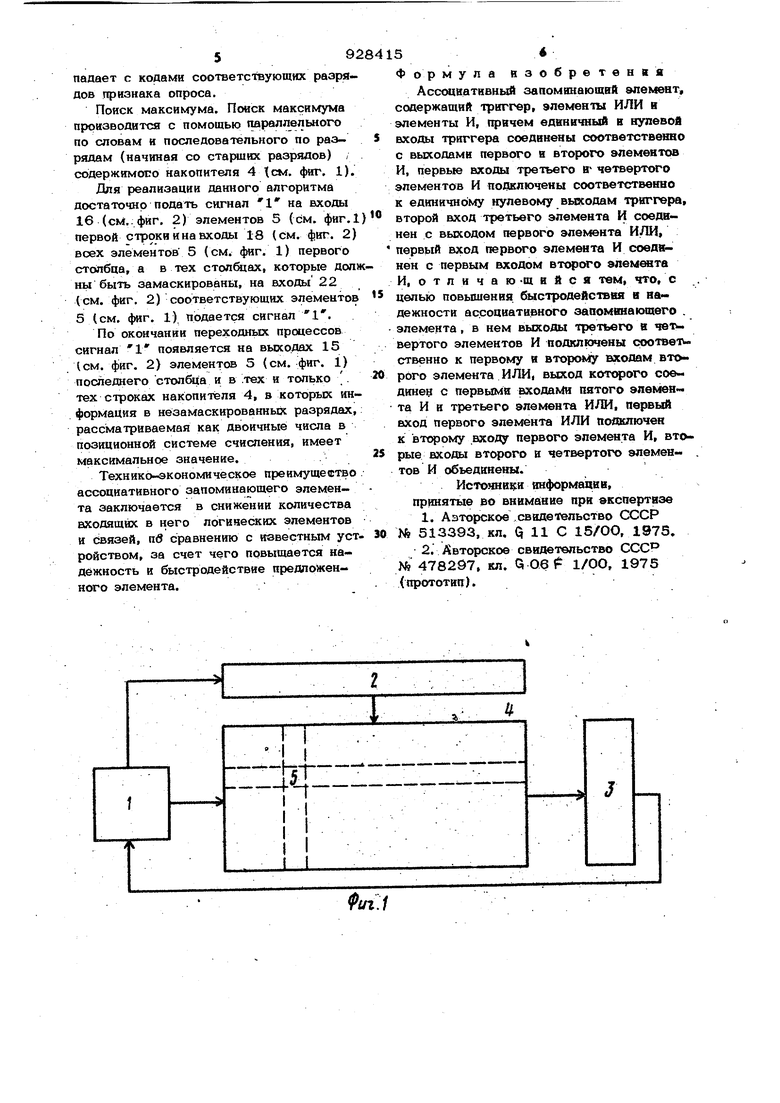

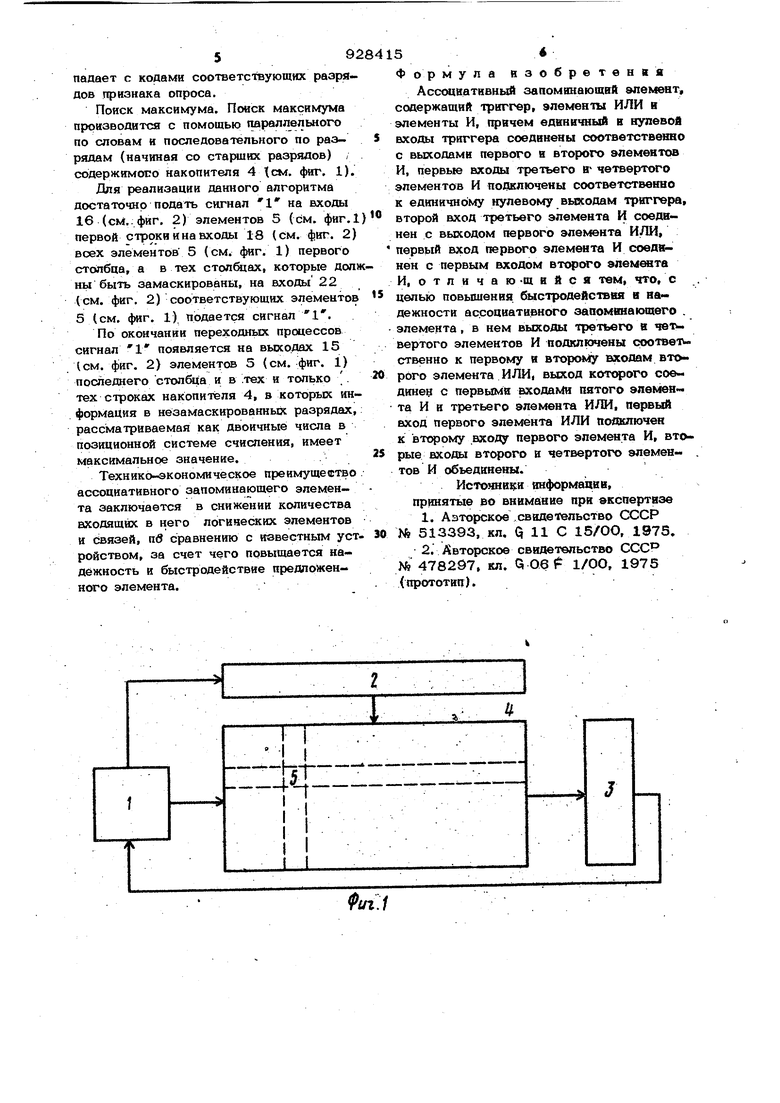

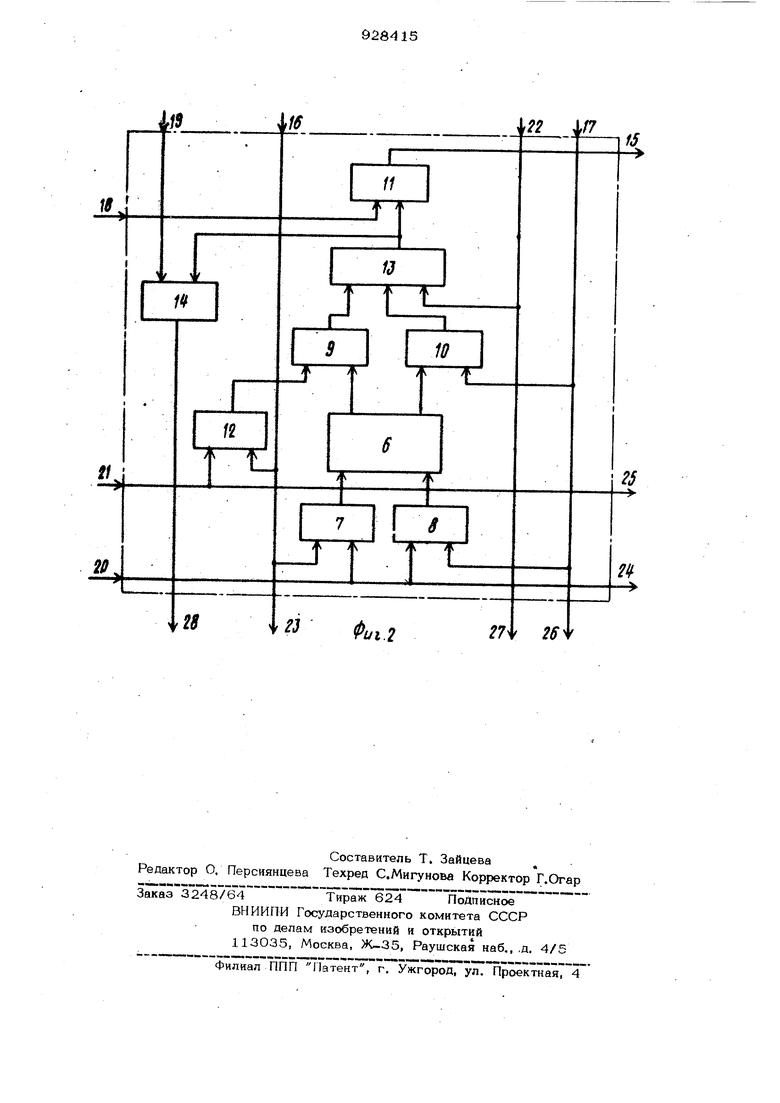

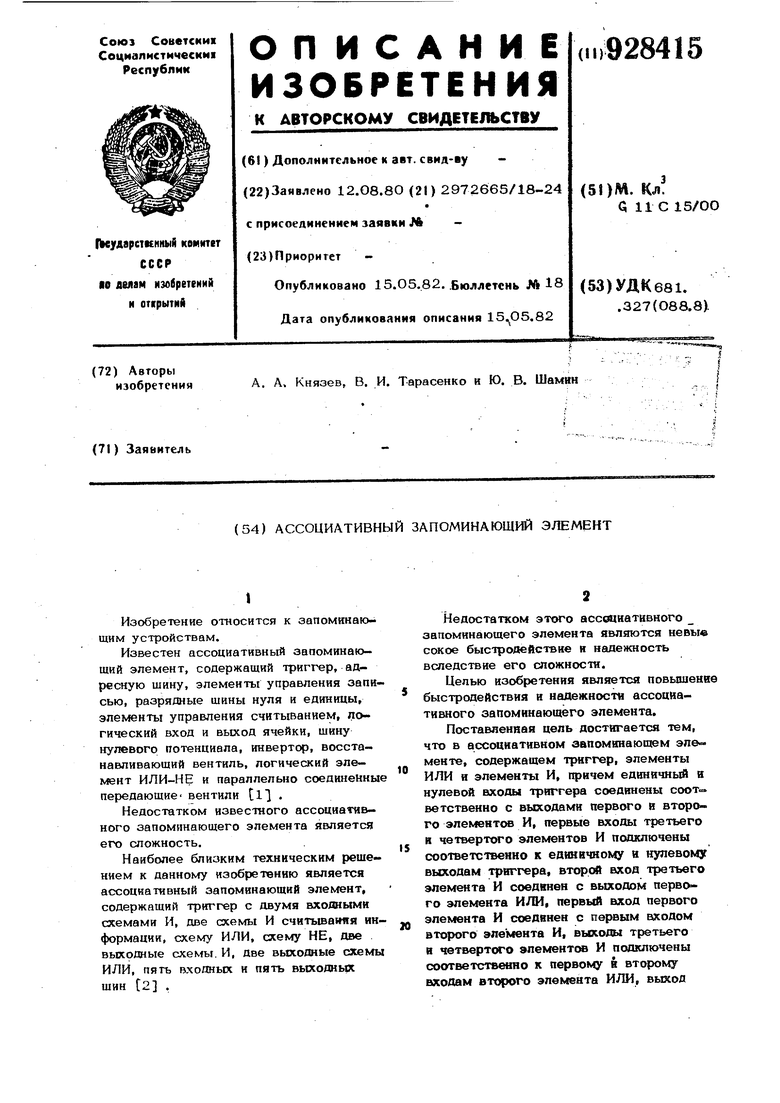

м второго элемента И, выходы третьего и четвертого элементе И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен с аервыми нссодами пятого элемента И и третьего элемента ИЛИ, первый вход первого элемента ИЛ подключен к второму входу первого элемента И, вторые входы второго н четвертого элементов И обьедннены. На фиг. 1 изображе( структурная схема арсоциатнвлого процессора, в котором применяется предложенный ассоциативный запоминающий элементу на , фкг. 2 - функциональная схема предложенного ассоциативного запоминающего элемента. На фиг. 1 обозначены местное уст.. ройство управления 1, входное устройств 2, выходное устройство 3 и накопитель 4 матричного тгипа, который состоит из одинаковых и одинаково между собой сое диненных ассоциативных запоминающих элементов 5. Ассоциативный запоминающий элемен (см, фиг, 2) содержит триггер 6, первый 7, второй 8, третий 9, четвертый Ю и пятый 11 элементы И, первый 12, второй 13 и третий 14 элементы ИЛИ.. На фиг. 2 обозначены первые выходы 15 и вход 16 второй 17, третий 18, четвертый 19, пятый 2О, шестой 21 И седьмой 22 входы, второй 23, третий 24, четвертый 25, пятый. 26, шестой 27 и седьмой 28 выходы ассоциативного запоминающего элемента. В каждом CTonate накопителя 4 (см. фиг. 1) седьмой 24, второй 23, шестой 27 и пятый 26 (см.-фиг. 2) Bbixotoi предыдущего ассоциативного запоминающего элемента 5 (см. фиг. 1) соединяются соответственно с четвертым 19 (см. фиг. 2), первым 16, седьмым 22 и вторым 17 входами следующего ассоц ативного запоминающего элемента 5 (см фиг. 1). В каждой строке накопителя 4 (см. фиг. 1) первый 15 (см. фиг. 2) четвертый 25 и третий 24 выходы продыдущего ассоциативного запоминающего элемента 5 (см. фиг. 1) соединяются соответственно с третьим 18 (см. фиг. шестым 21 и пятым 2О входами последующего ассоциативного запоминающего элемента 5 (см. фиг. 1). Предложенный -ассоциативный запоминающий элемент может быть реализован, например на интегральных микросхемах серии К 1О4 (элементы И, ИЛИ и К155 (триггеры). Ассоциативный запоминающий элемен работает следующим образом. Рассмотрим работу ассоциативного запоминающего, элемента на примере реализованного на его основе накопителя 4 (см. фиг. 1) матричного типа, входящего в ассоциативный процессор, который работает в четырех режимах, записи, чтения, ассоциативного поиска н поиска максимума. Запись. Слово, которое подлежит записи, подаётся с входного устройства 2 (см, фиг, 1) на вьосоды первой сверху строки матрицы накопителя 4 (см. фиг, 1/ таким образом, что прямой код каждого разряда подается на входы 16 (см. фиг. 2), а обратный код этого же разряда - на входы 17 элементов 5 (см, фиг, 1) соответствующего столбца накопителя 4. На входе 2О (см. фиг. 2) элементов 5 (см. фиг. 1) первого (слева) столбца в тех же строках накопителя 4 (см. фиг. 1), в которые необходимо произвести запись, подается сигнал 1, Маскирование записи производится путем одновременной подачи сигнала О на входы 16 и 17 (см. фиг.2) элементов 5 (см. фиг. -1). соответствующего столбца накопителя 4 (см, фиг. 1). Чтение. Для считывания содержимого некоторой строки накопителя 4 (см. фиг. 1) на вход 21 (см. фиг, 2) соот ветствующего элемента 5 (см. фиг. 1) первого (слева) столбца накопителя 4 подается сигнал . Содержимое вьйранной строки поступает на входы 24 (см. фиг, 2) элементов 5 (см. 1) поо- ледней (нижней) строки накопителя 4. Ассоциативный поиск. Разряды признака опроса подаются с входного устройства 2 (см, фиг. 1) на входы верхней строки матрицы накопителя 4 таким образом, что прямой код признака опроса каждого разряда подается на вход 16 (см. фиг, 2), а обратный код этого же разряда - на вход 17 элементов 5 (см, фиг, 1) соответствующего столба матрицы. На все входы 18 (см, фиг. 2) элементов 5 (см, фцг, 1) первого стобца накопителя 4 подается сигнал 1. . Маскирование опроса производится путем подачи сигнала 1 на входы 22 (см. фиг, 2) элементов 5 (см. фиг. 1) соответствующих столбцов накопителя 4. При этом сигнал I появляется на выходах 15 (см, фиг. 2) элементов 5 (см. фиг. 1) последнего столбца в тех и точьйо тех , строках накопителя 4 (tM. фйг, 1), в которых содержимое всех незамаскированных разрядов сов. падает с кодами соответствующих разрядов признака опроса. Поиск максимума. Поиск максимума производится с помощью параллельного по словам и последовательного по разpsuutM (начиная со старших разрядов) / содержимопо накопителя 4 ал. фиг. 1). Для реализации данного алгоритма достаточно подать сигнал на входы 16 (см.; фиг. 2) элементов 5 (см. фиг.1 первой строки и на входы 18 (см. фиг. 2) всех элементов 5 (см. фиг. 1) первого стсшбца, а в тех стол&хах, которые Долж ны быть замаскированы, на входы 22 (см. фиг, 2) соответствующих элементов 5 (см. фиг. 1) подается сигнал 1. По окончании переходных процессов сигнал 1 появляется на выходах 15 Чем. фиг. 2) элементов 5 (см. фиг. 1) последнего столбца и в .тех и только . тех строках накопителя 4, в которьк информация в незамаскированных разрядах, рассматриваемая как двоичные числа в позиционной системе счисления, имеет максимальное значение. Технико-экономическое преимущество ассоциативного запоминающего элемента заключается в снижении количества входящих в него логияеских элементов и связей, пв сравнению с известным устройством, за счет чего повышается надежность и быстродействие предложенного элемента.

.j-J.-....-.

-f 9

ui:i 54 Формула изобретения Асажиативный запоминающий элемент, содержащий триггер, элементы ИЛИ в элементы И, причем единичный н нулевой входы триггера соединены соответственно с выходами первого и второго элементов И, первые входы третьего и четвертого элементов И подключены соответственно к единичному нулевому выходам триггера, второй вход третьего элемента И соедв нен с выходом первого элемента ИЛИ, первый вход (юрвого элемента И соедянен с первым входом второго элемента И, отличаю-щийся тем, что, с целью повышения быстродействея и надежности ассоциативного зааоманающего элемента, в нем выходы третьего в чет вертого элементов И подключены сротве- ственно к первому и второму входам второго элемента ИЛИ, выход которого соединен с первыми входами пятого элемюн та И и третьего элемента ИЛИ, первый вход первого элемента ИЛИ пооключея к вт(ому входу первого элемента И, вторые входы второго и четвертого элементов И объединены. Истоянищ информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 513393, кл. Q 11 С 15/00, 1973. 2. Авторское свидетельство ССС №4782 7, кл. Ов 1/ОО, 1975 (прототип).

Авторы

Даты

1982-05-15—Публикация

1980-08-12—Подача