Изобретение относится к вычислительной технике и может быть использовано в качестве ассоциативного запоминающего устройства (АЗУ) ЭВМ в качестве элемента в ассоциативных процессорах при параллельной матричной обработке данных.

Известное ассоциативное ЗУ содержит матричный накопитель, мультиплексор-де- мультиплексор, приоритетный шифратор, специальную логику маскирования, регистры состояния и команд.

Более близким техническим решением является АЗУ, содержащее матричный накопитель, логические блоки, содержащие элементы И, И-НЕ, ИЛИ-НЕ, триггер.

К недостаткам этого АЗУ следует отнести задержку в получении сигнала есть информация, что происходит из-за иссле- довательной передачи сигнала блокировка от одного логического блока к другому,

так как при совпадении информации в первой строке на выход сигнал проходит через все логические блоки и каждый из них вносит задержку, при считывании найденных слов время между сигналами выборки должно быть таким, чтобы в случае совпадения информации в первой и последней строке сигнал снятия блокировки успел дойти до последнего логического блока, при увеличении емкости матричного накопителя эти задержки могут превысить время необходимое для реализации программного сравне- . ния.

Цель изобретения - повышение быстродействия. Цель достигается тем, что ассоциативное запоминающее устройство, содержащее матричный накопитель, входы- выходы запоминающих элементов каждого столбца которого подключены к соответствующим информационным шинам, и логичеVI ю ел ел

ю

ские блоки, дополнительно содержит усилители считывания, блоки записи, первый и второй инверторы, формирователь сигнала есть информация, формирователь сигнала готовность, блоки блокировки, логические блоки объединены в группы, причем выходы усилителей считывания соединены с входами соответствующих блоков записи и являются информационными входами-выходами устройства, входы усилителей счи- тывания и выходы блоков записи подключены к соответствующим информационным шинам, вход стррбирования блоков записи является первым управляющим входом устройства, вторым управляющим входом устройства является вход сброса маски блоков записи, вход управления предварительным зарядом которых является третьим управляющим входом устройства, входы опроса блоков записи и логических блоков объединены и является четвертым управляющим, входом устройства, пятым управляющим входом которого являются объединенные входы считывания усилителей считывания и вход первого инвертора, выход которого соединен с входами управле- ния записью блоков записи, вход формирования массива логических блоков является шестым управляющим входом устройства, седьмым управляющим входом которого является вход сброса логических блоков, вход выборки которых является восьмым управляющим входом устройства, девятым управляющим входом которого являются объединенные вход блокировки первого логического блока первой группы, первый вход первого блока блокировки и вход вторбто инвертора, выход которого соединен с первым входом формирователя сигнала готовность, выходы совпадения строк матричного накопителя соединены с входами совпадения соответствующих логических блоков, адресные выходы которых соединены с соответствующими адресными входами элементов памяти матричного накопителя, прямой выход блокировки логического 6лО(а соединен с входом блокировки последующего логического блока этой группы, инверсные выходы блокировки логических блоков, кроме последнего, соединены соответственное нечетными входами, начиная с третьего, формирователя сигнала готовность, выходы совпадения логических блоков соединены с соответствующими входами формирователя сигнала есть информация и четными входами формирователя сигнала готовность, выходы совпадения логических блоков каждой группы, кроме последней, соединены с соответствующими входами, начиная со второго, соответствующего блока блокировки, выход каждого блока блокировки, кроме последнего, подключен к первому входу последующего блока блокировки и, соответственно, ко входу блокировки первого логического блока каждой группы, начиная со второй, выход последнего блока блокировки подключен к входу бло- кировки первого логического блока последней группы, выход формирователя

сигнала есть информация является первым выходом устройства, вторым выходом которого является выход формирователя сигнала готовность.

Цель также достигается тем, что логиче5 ский блок содержит пороговый элемент, .первый и второй элементы ИЛИ-НЕ, первый и второй элементы И, первый и второй элементы ИЛИ, инвертор и триггер, причем первый вход первого элемента И является

0 входом опроса блока и соединен с входом порогового элемента, выход которого соединен со вторым входом элемента И и является входом совпадения блока, выход первого элемента И соединен с первым вхо5 дом первого элемента ИЛИ. второй вход которого является входом формирования массива блока, входом сброса которого является первый вход второго элемента ИЛИ, второй вход которого соединен с выходом

0 второго элемента И, первый вход которого подключен к первому входу первого элемента ИЛИ-НЕ и является входом выборки блока, второй вход второго элемента И и подключен к выходу первого элемента

5 ИЛИ-НЕ и является адресным выходом блока, выходом блокировки которого является выход инвертора, вход которого является инверсным выходом блокировки блока и соединен с выходом второго элемента ИЛИ0 НЕ, первый вход которого является входом совпадения блока и соединен с прямым выходом триггера/первый вход которого соединен с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен со

5 вторым входом триггера, инверсный выход которого соединен со вторым входом первого элемента ИЛИ-НЕ. третий вход которого соединен со вторым входом второго элемента ИЛИ-НЕ и является входом блокировки

0 блока.

Отличительными от прототипа признаками являются новая совокупность конструктивных элементов, выражающаяся в наличии новых блоков, а именно: усилите5 лей считывания, блоков записи, первого и второго инверторов, формирователя сигнала есть информация, формирователя сигнала готовность, блоков блокировки, логические блоки объединены в группы, новое исполнение логических блоков, каждый

из которых содержит пороговый элемент, первый и второй элементы ИЛИ-НЕ, первый и второй элементы И, первый и второй элементы И Л И, инвертор и триггер: наличие новых связей между элементами устройства.

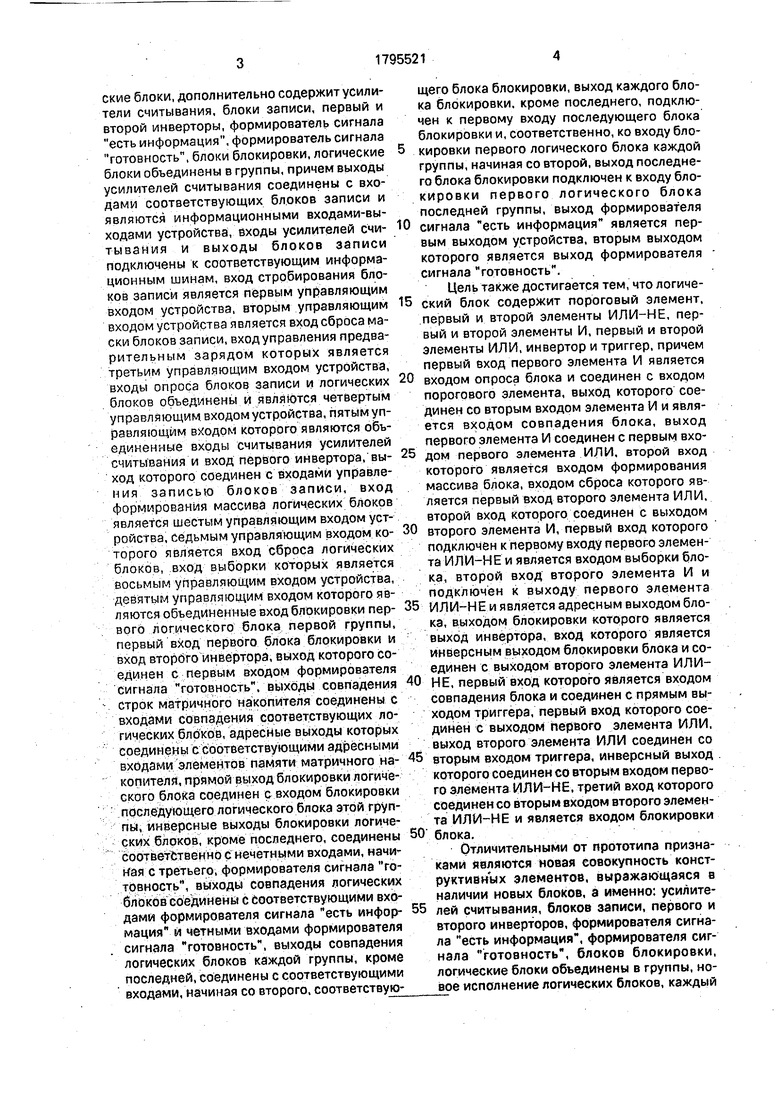

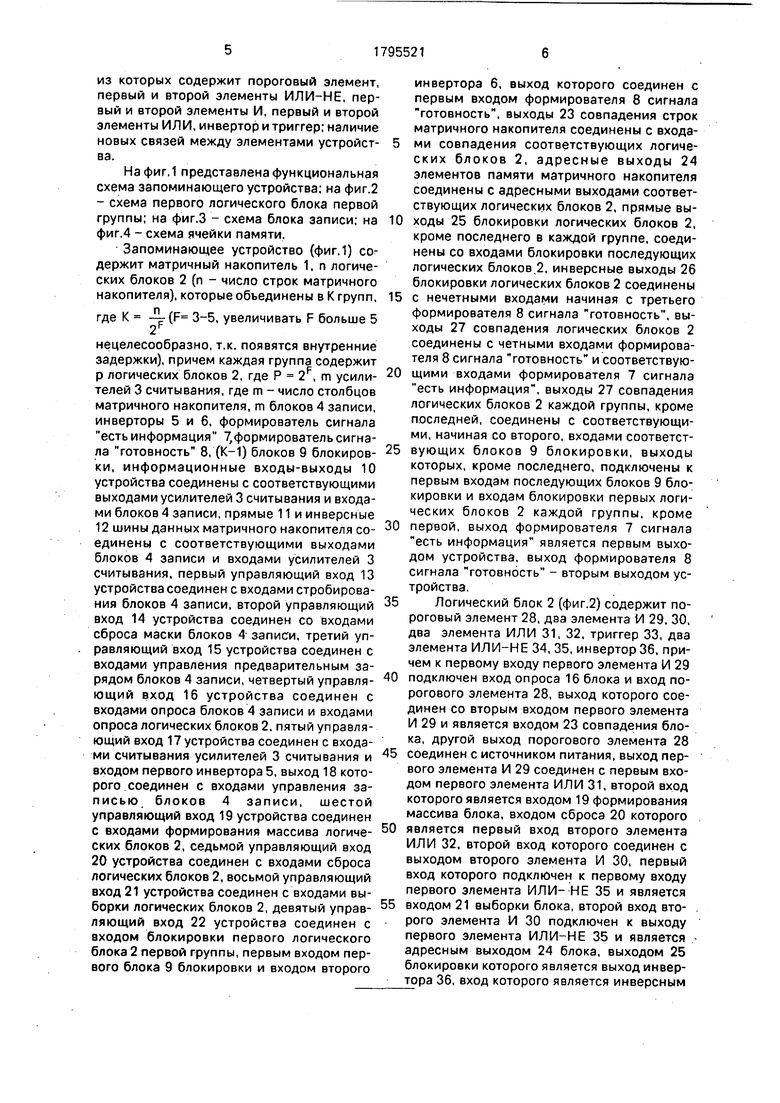

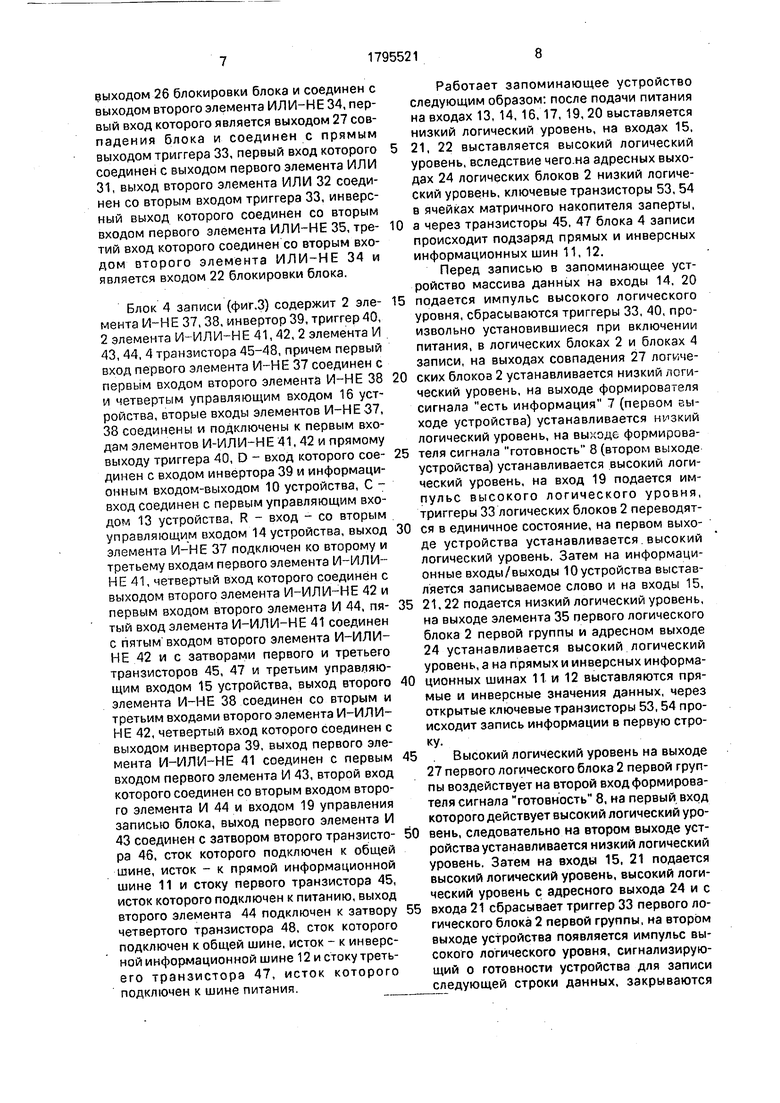

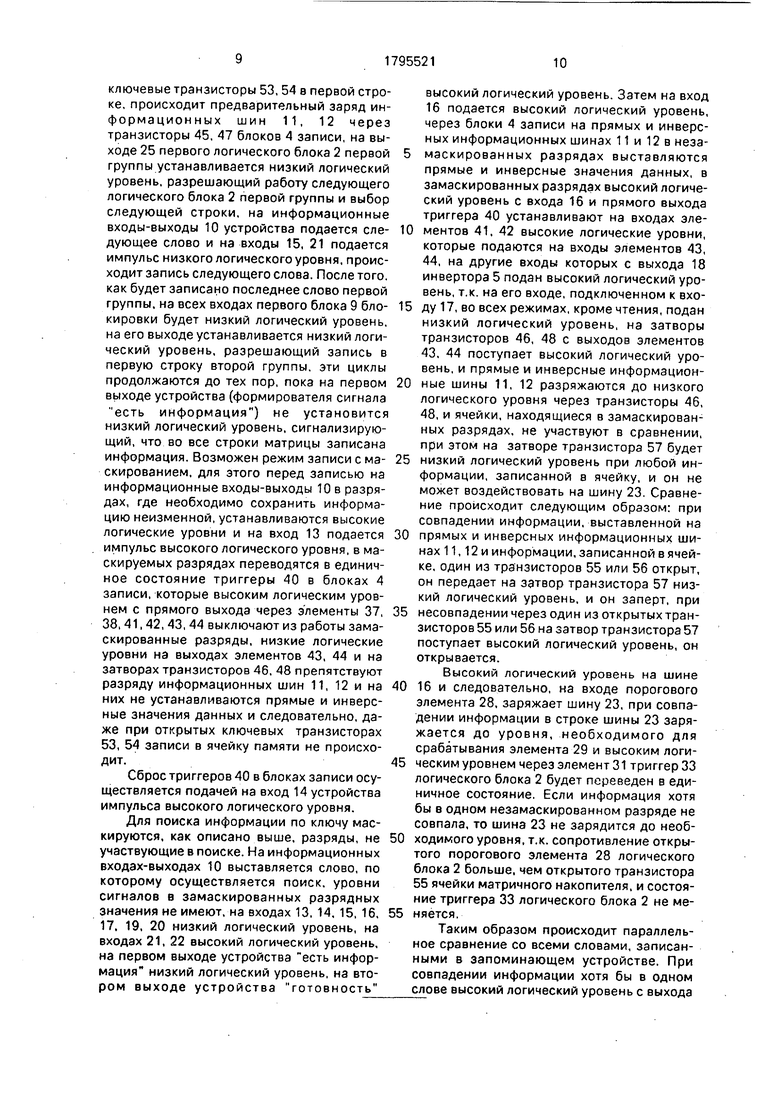

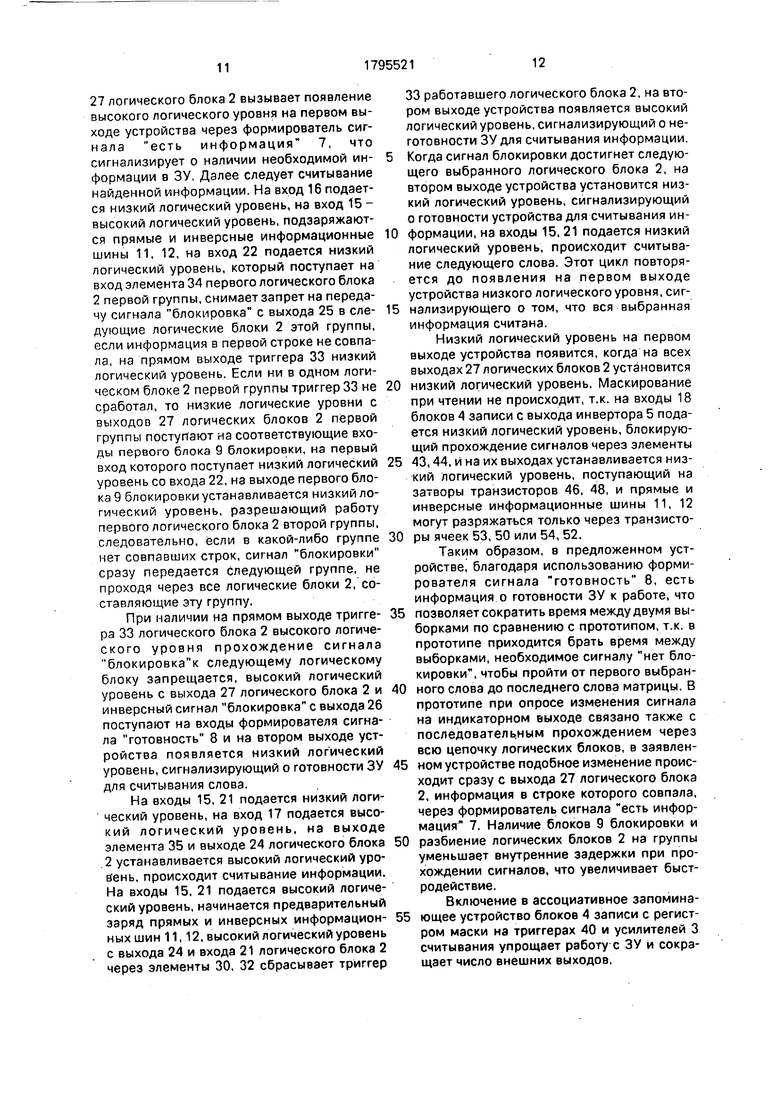

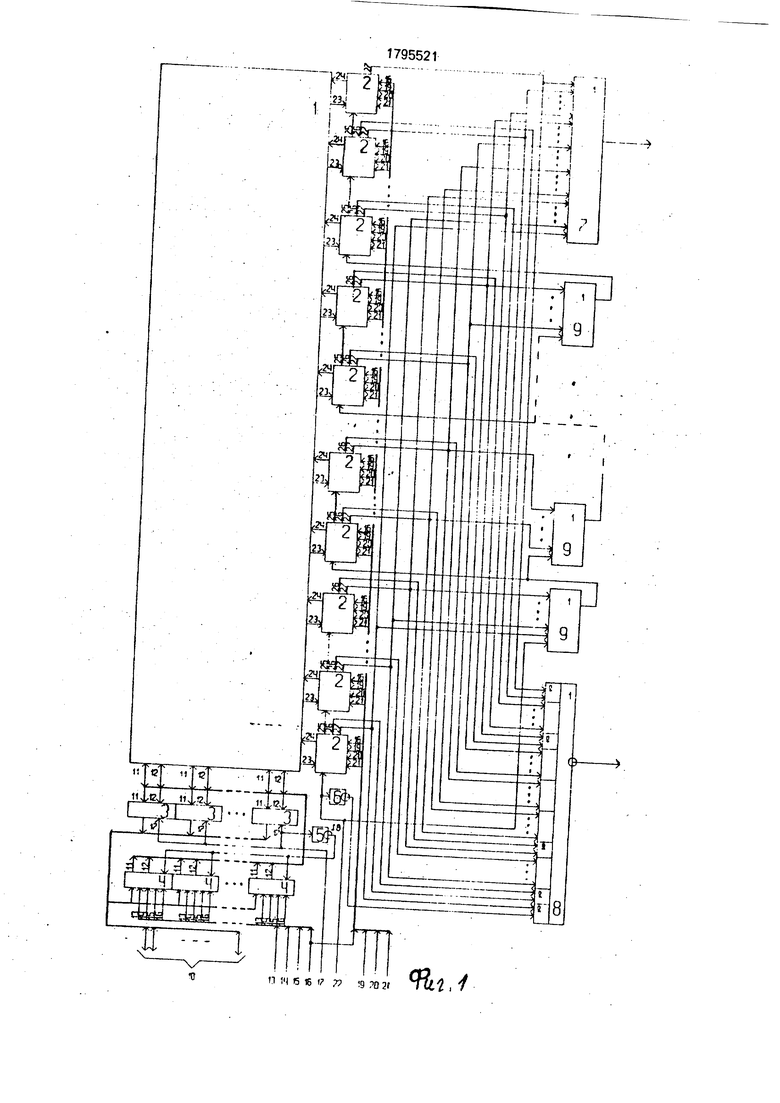

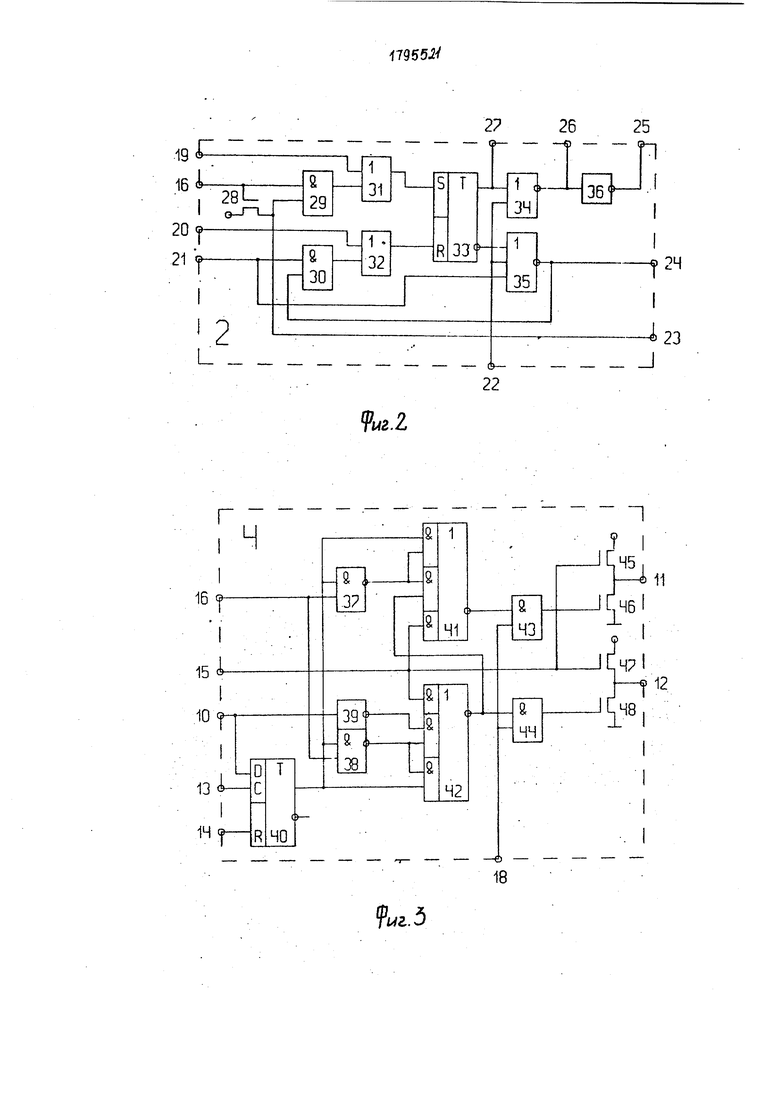

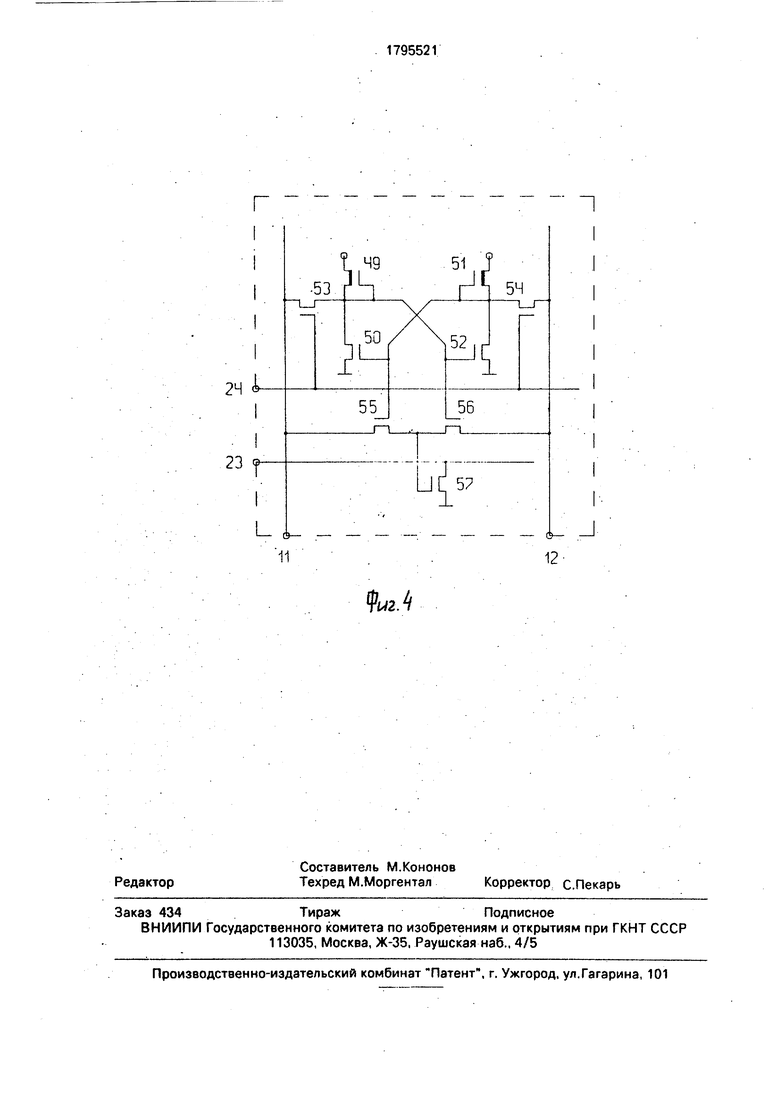

На фиг.1 представлена функциональная схема запоминающего устройства: на фиг.2 - схема первого логического блока первой группы; на фиг.З - схема блока записи; на фиг.4 - схема ячейки памяти.

Запоминающее устройство (фиг.1) содержит матричный накопитель 1. п логических блоков 2 (п - число строк матричного накопителя), которые объединены в К групп,

где К

(F 3-5, увеличивать F больше 5

нецелесообразно, т.к. появятся внутренние задержки), причем каждая группа содержит р логических блоков 2, где Р 2F, m усилителей 3 считывания, где m - число столбцов матричного накопителя, m блоков 4 записи, инверторы 5 и 6, формирователь сигнала есть информация 7,формирователь сигнала готовность 8, (К-1) блоков 9 блокировки, информационные входы-выходы 10 устройства соединены с соответствующими выходами усилителей 3 считывания и входами блоков 4 записи, прямые 11 и инверсные 12 шины данных матричного накопителя соединены с соответствующими выходами блоков 4 записи и входами усилителей 3 считывания, первый управляющий вход 13 устройства соединен с входами стробирова- ния блоков 4 записи, второй управляющий вход 14 устройства соединен со входами сброса маски блоков 4 записи, третий управляющий вход 15 устройства соединен с входами управления предварительным зарядом блоков 4 записи, четвертый управляющий вход 16 устройства соединен с входами опроса блоков 4 записи и входами опроса логических блоков 2, пятый управляющий вход 17 устройства соединен с входами считывания усилителей 3 считывания и входом первого инвертора 5, выход 18 которого соединен с входами управления записью блоков 4 записи, шестой управляющий вход 19 устройства соединен с входами формирования массива логических блоков 2, седьмой управляющий вход 20 устройства соединен с входами сброса логических блоков 2, восьмой управляющий вход 21 устройства соединен с входами выборки логических блоков 2, девятый управляющий вход 22 устройства соединен с входом блокировки первого логического блока 2 первой группы, первым входом первого блока 9 блокировки и входом второго

инвертора 6, выход которого соединен с первым входом формирователя 8 сигнала готовность, выходы 23 совпадения строк матричного накопителя соединены с входа- ми совпадения соответствующих логических блоков 2, адресные выходы 24 элементов памяти матричного накопителя соединены с адресными выходами соответствующих логических блоков 2, прямые вы0 ходы 25 блокировки логических блоков 2, кроме последнего в каждой группе, соединены со входами блокировки последующих логических блоков,2, инверсные выходы 26 блокировки логических блоков 2 соединены

5 с нечетными входами начиная с третьего формирователя 8 сигнала готовность, выходы 27 совпадения логических блоков 2 соединены с четными входами формирователя 8 сигнала готовность и соответствую0 щими входами формирователя 7 сигнала есть информация, выходы 27 совпадения логических блоков 2 каждой группы, кроме последней, соединены с соответствующими, начиная со второго, входами соответст5 вующих блоков 9 блокировки, выходы которых, кроме последнего, подключены к первым входам последующих блоков 9 блокировки и входам блокировки первых логических блоков 2 каждой группы, кроме

0 первой, выход формирователя 7 сигнала есть информация является первым выходом устройства, выход формирователя 8 сигнала готовность - вторым выходом устройства.

5 Логический блок 2 (фиг.2) содержит пороговый элемент 28, даа элемента И 29, 30, два элемента ИЛИ 31, 32, триггер 33, два элемента ИЛИ-НЕ 34, 35, инвертор 36, причем к первому входу первого элемента И 29

0 подключен вход опроса 16 блока и вход порогового элемента 28, выход которого соединен со вторым входом первого элемента И 29 и является входом 23 совпадения блока, другой выход порогового элемента 28

5 соединен с источником питания, выход первого элемента И 29 соединен с первым входом первого элемента ИЛИ 31, второй вход которого является входом 19 формирования массива блока, входом сброса 20 которого

0 является первый вход второго элемента ИЛИ 32, второй вход которого соединен с выходом второго элемента И 30, первый вход которого подключен к первому входу первого элемента ИЛИ-НЕ 35 и является

5 входом 21 выборки блока, второй вход второго элемента И 30 подключен к выходу первого элемента ИЛИ-НЕ 35 и является адресным выходом 24 блока, выходом 25 блокировки которого является выход инвертора 36, вход которого является инверсным

выходом 26 блокировки блока и соединен с выходом второго элемента ИЛИ-НЕ 34, первый вход которого является выходом 27 совпадения блока и соединен с прямым выходом триггера 33, первый вход которого соединен с выходом первого элемента ИЛИ 31, выход второго элемента ИЛИ 32 соединен со вторым входом триггера 33, инверсный выход которого соединен со вторым входом первого элемента ИЛИ-НЕ 35, третий вход которого соединен со вторым входом второго элемента ИЛИ-НЕ 34 и является входом 22 блокировки блока.

Блок 4 записи (фиг.З) содержит 2 элемента И-НЕ 37, 38, инвертор 39, триггер40, 2 элемента И-ИЛ И-НЕ 41, 42, 2 элемента И 43, 44, 4 транзистора 45-48, причем первый вход первого элемента И-НЕ 37 соединен с первым входом второго элемента И-НЕ 38 и четвертым управляющим входом 16 устройства, вторые входы элементов И-НЕ 37, 38 соединены и подключены к первым входам элементов И-ИЛИ-НЕ 41, 42 и прямому выходу триггера 40, D - вход которого соединен с входом инвертора 39 и информационным входом-выходом 10 устройства, С - вход соединен с первым управляющим входом 13 устройства, R - вход - со вторым управляющим входом 14 устройства, выход элемента И-НЕ 37 подключен ко второму и третьему входам первого элемента И-ИЛИ- НЕ 41, четвертый вход которого соединён с выходом второго элемента И-ИЛИ-НЕ 42 и первым входом второго элемента И 44, пятый вход элемента И-ИЛИ-НЕ 41 соединен с пятым входом второго элемента И-ИЛИ- НЕ 42 и с затворами первого и третьего транзисторов 45, 47 и третьим управляющим входом 15 устройства, выход второго элемента И-НЕ 38 соединен со вторым и третьим входами второго элемента И-ИЛИ- НЕ 42, четвертый вход которого соединен с выходом инвертора 39, выход первого элемента И-ИЛИ-НЕ 41 соединен с первым входом первого элемента И 43, второй вход которого соединен со вторым входом второго элемента И 44 и входом 19 управления записью блока, выход первого элемента И 43 соединен с затвором второго транзистора 4.6, сток которого подключен к общей шине, исток - к прямой информационной шине 11 и стоку первого транзистора 45, исток которого подключен к питанию, выход второго элемента 44 подключен к затвору четвертого транзистора 48, сток которого подключен к общей шине, исток - к инверсной информационной шине 12 и стоку треть- его транзистора 47, исток которого подключен к шине питания.

Работает запоминающее устройство следующим образом: после подачи питания на входах 13, 14, 16,17, 19, 20 выставляется низкий логический уровень, на входах 15,

21, 22 выставляется высокий логический уровень, вследствие чего.на адресных выходах 24 логических блоков 2 низкий логический уровень, ключевые транзисторы 53, 54 в ячейках матричного накопителя заперты,

0 а через транзисторы 45, 47 блока 4 записи происходит подзаряд прямых и инверсных информационных шин 11, 12.

Перед записью в запоминающее устройство массива данных на входы 14, 20

5 подается импульс высокого логического уровня, сбрасываются триггеры 33, 40, произвольно установившиеся при включении питания, в логических блоках 2 и блоках 4 записи, на выходах совпадения 27 логиче0 ских блоков 2 устанавливается низкий логический уровень, на выходе формирователя сигнала есть информация 7 (первом выходе устройства) устанавливается низкий логический уровень, на выходе формирова5 теля сигнала готовность 8 (втором выходе устройства) устанавливается высокий логический уровень, на вход 19 подается импульс высокого логического уровня, триггеры 33 логических блоков 2 переводят0 ся в единичное состояние, на первом выходе устройства устанавливается, высокий логический уровень. Затем на информационные входы/выходы 10устройства выставляется записываемое слово и на входы 15,

5 21,22 подается низкий логический уровень, на выходе элемента 35 первого логического блока 2 первой группы и адресном выходе 24 устанавливается высокий логический уровень, а на прямых и инверсных информа0 ционных шинах 11. и 12 выставляются прямые и инверсные значения данных, через открытые ключевые транзисторы 53,54 происходит запись информации в первую строку.

5 . Высокий логический уровень на выходе 27 первого логического блока 2 первой группы воздействует на второй вход формирователя сигнала готовность 8, на первый вход которого действует высокий логический уро0 вень, следовательно на втором выходе устройства устанавливается низкий логический уровень. Затем на входы 15, 21 подается высокий логический уровень, высокий логический уровень с адресного выхода 24 и с

5 входа 21 сбрасывает триггер 33 первого логического блока 2 первой группы, на втором выходе устройства появляется импульс высокого логического уровня, сигнализирующий о готовности устройства для записи следующей строки данных, закрываются

ключевые транзисторы 53, 54 в первой строке, происходит предварительный заряд ин- формационных шин 11, 12 через транзисторы 45, 47 блоков 4 записи, на выходе 25 первого логического блока 2 первой группы устанавливается низкий логический уровень, разрешающий работу следующего логического блока 2 первой группы и выбор следующей строки, на информационные входы-выходы 10 устройства подается еле- дующее слово и на входы 15, 21 подается импульс низкого логического уровня, происходит запись следующего слова. После того, как будет записано последнее слово первой группы, на всех входах первого блока 9 бло- кировки будет низкий логический уровень, на его выходе устанавливается низкий логический уровень, разрешающий запись в первую строку второй группы, эти циклы продолжаются до тех пор, пока на первом выходе устройства (формирователя сигнала есть информация) не установится низкий логический уровень, сигнализирующий, что во все строки матрицы записана информация. Возможен режим записи с ма- скированием, для этого перед записью на информационные входы-выходы 10 в разрядах, где необходимо сохранить информацию неизменной, устанавливаются высокие логические уровни и на вход 13 подается импульс высокого логического уровня, в маскируемых разрядах переводятся в единичное состояние триггеры 40 в блоках 4 записи, которые высоким логическим уровнем с прямого выхода через элементы 37, 38, 41, 42, 43, 44 выключают из работы замаскированные разряды, низкие логические уровни на выходах элементов 43, 44 и на затворах транзисторов 46, 48 препятствуют разряду информационных шин 11, 12 и на них не устанавливаются прямые и инверсные значения данных и следовательно, даже при открытых ключевых транзисторах 53, 54 записи в ячейку памяти не происходит.

Сброс триггеров 40 в блоках записи осуществляется подачей на вход 14 устройства импульса высокого логического уровня.

Для поиска информации по ключу маскируются, как описано выше, разряды, не участвующие в поиске. На информационных входах-выходах 10 выставляется слово, по которому осуществляется поиск, уровни сигналов в замаскированных разрядных значения не имеют, на входах 13, 14, 15, 16, 17, 19, 20 низкий логический уровень, на входах 21, 22 высокий логический уровень, на первом выходе устройства есть информация низкий логический уровень, на втором выходе устройства готовность

высокий логический уровень. Затем на вход 16 подается высокий логический уровень, через блоки 4 записи на прямых и инверсных информационных шинах 11 и 12 в незамаскированных разрядах выставляются прямые и инверсные значения данных, в замаскированных разрядах высокий логический уровень с входа 16 и прямого выхода триггера 40 устанавливают на входах элементов 41, 42 высокие логические уровни, которые подаются на входы элементов 43, 44, на другие входы которых с выхода 18 инвертора 5 подан высокий логический уровень, т.к. на его входе, подключенном к входу 17, во всех режимах, кроме чтения, подан низкий логический уровень, на затворы транзисторов 46, 48 с выходов элементов 43, 44 поступает высокий логический уровень, и прямые и инверсные информационные шины 11, 12 разряжаются до низкого логического уровня через транзисторы 46, 48, и ячейки, находящиеся в замаскированных разрядах, не участвуют в сравнении, при этом на затворе транзистора 57 будет низкий логический уровень при любой информации, записанной в ячейку, и он не может воздействовать на шину 23. Сравнение происходит следующим образом: при совпадении информации, выставленной на прямых и инверсных информационных шинах 11,12 и информации, записанной в ячейке, один из транзисторов 55 или 56 открыт, он передает на затвор транзистора 57 низкий логический уровень, и он заперт, при несовпадении через один из открытых транзисторов 55 или 56 на затвор транзистора 57 поступает высокий логический уровень, он открывается.

Высокий логический уровень на шине 16 и следовательно, на входе порогового элемента 28, заряжает шину 23, при совпадении информации в строке шины 23 заряжается до уровня, необходимого для срабатывания элемента 29 и высоким логическим уровнем через элемент 31 триггер 33 логического блока 2 будет переведен в единичное состояние. Если информация хотя бы в одном незамаскированном разряде не совпала, то шина 23 не зарядится до необходимого уровня, т.к. сопротивление открытого порогового элемента 28 логического блока 2 больше, чем открытого транзистора 55 ячейки матричного накопителя, и состояние триггера 33 логического блока 2 не меняется.

Таким образом происходит параллельное сравнение со всеми словами, записанными в запоминающем устройстве. При совпадении информации хотя бы в одном слове высокий логический уровень с выхода

27 логического блока 2 вызывает появление высокого логического уровня на первом выходе устройства через формирователь сигнала есть информация 7, что сигнализирует о наличии необходимой информации в ЗУ. Далее следует считывание найденной информации. На вход 16 подается низкий логический уровень, на вход 15 - высокий логический уровень, подзаряжаются прямые и инверсные информационные шины 11, 12, на вход 22 подается низкий логический уровень, который поступает на вход элемента 34 первого логического блока 2 первой группы, снимает запрет на передачу сигнала блокировка с выхода 25 в следующие логические блоки 2 этой группы, если информация в первой строке не совпала, на прямом выходе триггера 33 низкий логический уровень. Если ни в одном логическом блоке 2 первой группы триггер 33 не сработал, то низкие логические уровни с выходов 27 логических блоков 2 первой группы поступают на соответствующие входы первого блока 9 блокировки, на первый вход которого поступает низкий логический уровень со входа 22, на выходе первого блока 9 блокировки устанавливается низкий логический уровень, разрешающий работу первого логического блока 2 второй группы, следовательно, если в какой-либо группе нет совпавших строк, сигнал блокировки сразу передается следующей группе, не проходя через все логические блоки 2, составляющие эту группу.

При наличии на прямом выходе триггера 33 логического блока 2 высокого логиче- ского уровня прохождение сигнала блокировка к следующему логическому блоку запрещается, высокий логический уровень с выхода 27 логического блока 2 и инверсный сигнал блокировка с выхода 26 поступают на входы формирователя сигнала готовность 8 и на втором выходе устройства появляется низкий логический уровень, сигнализирующий о готовности ЗУ для считывания слова.

На входы 15, 21 подается низкий логический уровень, на вход 17 подается высокий логический уровень, на выходе элемента 35 и выходе 24 логического блока 2 устанавливается высокий логический уровень, происходит считывание информации. На входы 15, 21 подается высокий логический уровень, начинается предварительный заряд прямых и инверсных информационных шин 11,12. высокий логический уровень с выхода 24 и входа 21 логического блока 2 через элементы 30, 32 сбрасывает триггер

33 работавшего логического блока 2, на втором выходе устройства появляется высокий логический уровень, сигнализирующий о неготовности ЗУ для считывания информации.

Когда сигнал блокировки достигнет следующего выбранного логического блока 2, на втором выходе устройства установится низкий логический уровень, сигнализирующий о готовности устройства для считывания информации, на входы 15. 21 подается низкий логический уровень, происходит считывание следующего слова. Этот цикл повторяется до появления на первом выходе устройства низкого логического уровня, сигнализирующего о том, что вся выбранная информация считана.

Низкий логический уровень на первом выходе устройства появится, когда на всех выходах 27 логических блоков 2 установится

низкий логический уровень. Маскирование при чтении не происходит, т.к. на входы 18 блоков 4 записи с выхода инвертора 5 подается низкий логический уровень, блокирующий прохождение сигналов через элементы

43,44, и на их выходах устанавливается низкий логический уровень, поступающий на затворы транзисторов 46, 48, и прямые и инверсные информационные шины 11, 12 могут разряжаться только через транзисторы ячеек 53, 50 или 54, 52.

Таким образом, в предложенном устройстве, благодаря использованию формирователя сигнала готовность 8, есть информация о готовности ЗУ к работе, что

позволяет сократить время между двумя выборками по сравнению с прототипом, т.к. в прототипе приходится брать время между выборками, необходимое сигналу нет блокировки, чтобы пройти от первого выбранного слова до последнего слова матрицы, В прототипе при опросе изменения сигнала на индикаторном выходе связано также с последователь.ным прохождением через всю цепочку логических блоков, в заявленном устройстве подобное изменение происходит сразу с выхода 27 логического блока 2, информация в строке которого совпала, через формирователь сигнала есть информация 7. Наличие блоков 9 блокировки и

разбиение логических блоков 2 на группы уменьшает внутренние задержки при прохождении сигналов, что увеличивает быстродействие.

Включение в ассоциативное запоминающее устройство блоков 4 записи с регистром маски на триггерах 40 и усилителей 3 считывания упрощает работу с ЗУ и сокращает число внешних выходов.

Формула изобретения 1. Ассоциативное запоминающее устройство, содержащее матричный накопитель, входы-выходы запоминающих элементов каждого столбца которого подключены к соответствующим информационным шинам, и логические блоки, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит усилители считывания, блоки записи, первый и второй инверторы, формирователь сигнала Есть информация, формирователь сигнала Готовность, блоки блокировки, логические блоки объединены в группы, причем выходы усилителей считывания соединены с входами соответствующих блоков записи и являются информационными входами-выходами устройства, входы усилителей считывания и выходы блоков записи подключены к соответствующим информационным шинам, вход стробирования блоков записи является первым управляющим входом устройства, вторым управляющим входом устройства является вход сброса маски блоков записи, вход управления предварительным зарядом которых является третьим управляющим входом устройства, входы опроса блоков записи и логических блоков объединены и являются четвертым управляющим входом устройства, пятым управляющим входом которого являются объединенные входы считывания усилителей считывания и вход первого инвертора, выход которого соединен с входами управле- ния записью блоков записи, вход формирования массива логических блоков является шестым управляющим входом устройства, седьмым управляющим входом которого является вход сброса логических блоков, вход выборки которых является восьмым управляющим входом устройства, девятым управляющим входом которого являются объединенные вход блокировки первого логического блока первой группы, первый вход первого блока блокировки и вход второго инвертора, выход которого соединен с первым входом формирователя сигнала Готовность, выходы совпадения строк матричного накопителя соединены с входами совпадения соответствующих логических блоков, адресные выходы которых соединены с соответствующими адресными входами элементов памяти матричного накопителя, прямой выход блокировки логического блока соединен с входом блокировки последующего логического блока этой группы, инверсные выходы блокировки логических блоков, кроме последнего, соединены соответственно с нечетными входами, начиная с третьего формирователя сигнала Готовность, выходы совпадения логических блоков соединены с соответствующими входами формирователя сигнала Есть информация и четными входами формирователя сигнала Готовность, выходы совпадения логических блоков каждой группы, кроме последней, соединены с соответствующими входами, начиная с второго, соответствующего блока блокировки, выход каждого блока блокировки, кроме последнего, подключен к первому входу последующего блока блокировки и, соответственно, к входу блокировки первого логического блока каждой группы, начиная с второй, выход последнего блока блокировки подключен к входу блокировки первого логического бло- . ка последней группы, выход формирователя сигнала Есть информация является первым выходом устройства, вторым выходом которого является выход формирователя сигнала Готовность.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что логический блок содержит пороговый элемент, первый и второй элементы ИЛИ-НЕ. первый и второй элементы И, первый и второй элементы ИЛИ, инвертор и триггер, причем первый вход первого элемента И является входом опроса блока и соединен с входом порогового элемента, выход которого соединен с вторым входом элемента И и является входом совпадения блока, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого является входом формирования массива блока, входом сброса которого является первый вход второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого подключен к первому входу первого элемента ИЛИ-НЕ и является входом выборки блока, второй вход второго элемента И подключен к выходу первого элемента ИЛИ-НЕ и является адресным выходом блока, выходом блокировки которого является выход инвертора, вход которого является инверсным выходом блокировки блока и соединен с выходом второго элемента ИЛИ- НЕ, первый вход которого является выходом совпадения блока и соединен с прямым выходом триггера, первый вход которого соединен с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом триггера, инверсный выход которого соединен с вторым входом первого . элемента ИЛИ-НЕ, третий вход которого соединен с вторым входом второго элемента ИЛИ-НЕ и является входом блокировки блока.

2726

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1654852A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве ассоциативного запоминающего устройства ЭВМ и в качестве элемента в ассоциативных процессорах при параллельной и матричной обработке данных. Изобретение позволяет повысить быстродействие устройства. Поставленная цель достигается тем, что ассоциативное запоминающее устройство, содержащее матричный накопитель, группы логических блоков, усилители считывания, блоки записи, первый и второй инверторы, формирователь сигнала есть информация, формирователь сигнала готовность, блоки блокировки, каждый логический блок содержит триггер, первый и второй элементы ИЛИ-НЕ, первый и второй элементы И, первый и второй элементы ИЛИ, инвертор и пороговый элемент. 1 з.п. ф-лы, 4 ил. (/) С

19

16

20

21

24

%г2

Риг.3

Г

11

12

4U4

| Коул Бернард К | |||

| Ассоциативные ЗУ компании АМД | |||

| Электроника, № 24, 1988, стр.36 | |||

| Ассоциативное запоминающее устройство | 1984 |

|

SU1277210A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-02-15—Публикация

1990-10-01—Подача