(5) ЦИФРОВОЙ КОМПАРАТОР

1

Изобретение относится к цифровому регулированию параметров технологических процессов и может быть использовано для высокоточной стабилизации параметров, например, скорости электродвигателей.

Известны цифровые компараторы, содержащие реверсивный счетчик, выходы которого соединены с входами схем блокировки, а входы через схему управления - с входами устройства 1 и 2,

Известные устройства реагируют на.разность частот задания и обратной связи.

Цель изобретения - расширение функциональных возможностей устройства. .

Эта цель достигается тем, что в устройство введены последовательно соединенные третий RS-триггер, третий элемент И, а также последовательно соединенные .блок кодовых вентилей и вычитающий счетчик, выХОД которого подключен к входу дешифратора, соединенного выходом с первым входом третьего RS-триггера, второй вход которого соединен с шиной опорной частоты, второй вход вы, читающего счетчика соединен с выходом третьего элемента И, второй вход KOTOpqro подключен к выходу генератора импульсов, первый вход блока кодовых вентилей соединен с

10 прямым выходом реверсивного счетчика и является выходом компаратора, а второй вход - с шиной опорной частоты.

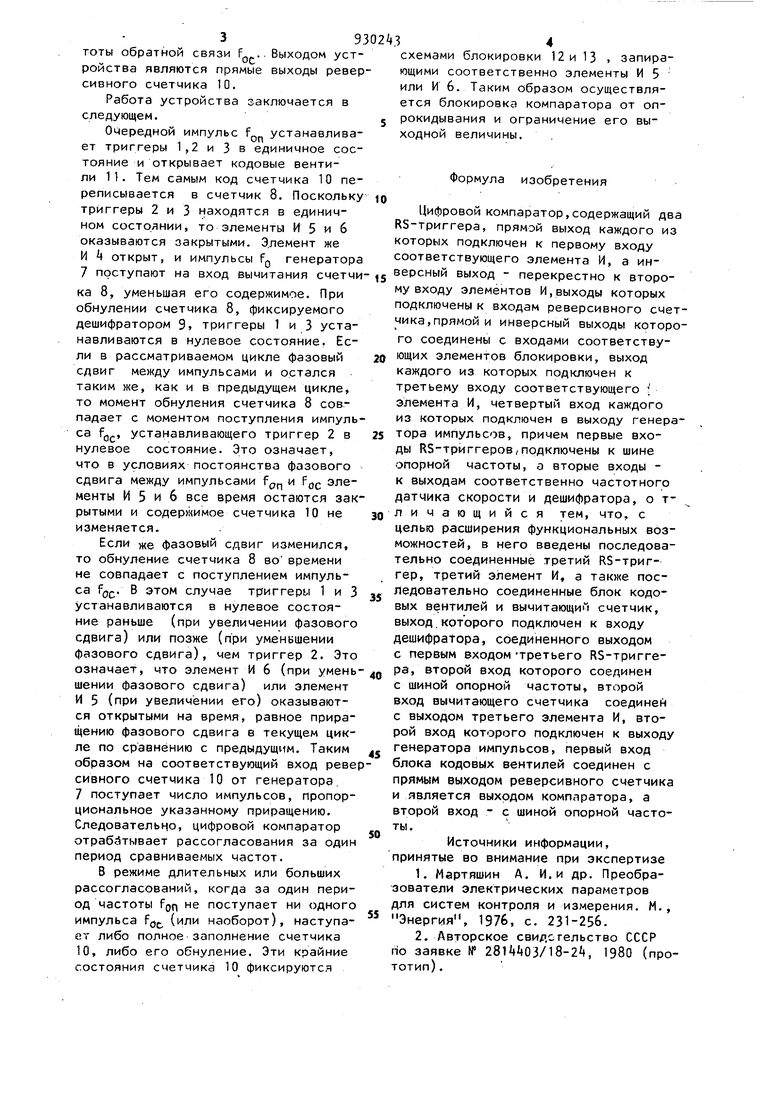

На чертеже приведена функцио15нальная схема цифрового компаратора.

Устройство содержит RS-триггеры 1,2 и 3, элементы И ,5 и.6, генератор 7 стабильной частоты f-j , вычитающий счетчик 8, дешифратор нуля

20 9, реверсивный счетчик 10, блок 11 кодовых вентилей., схемы блокировки 12 и 13. Входами устройства являются шины опорной частоты f и час

тоты обратной связи FQ...- Выходом устройства являются прямые выходы реверсивного счетчика 10.

Работа устройства заключается в следующем.

Очередной импульс f устанавливает триггеры 1,2 и 3 в единичное состояние и открывает кодовые вентили 11. Тем самым код счетчика 10 переписывается в счетчик 8. Поскольку триггеры 2 и 3 находятся в единичном состоянии, то элементы И 5 и 6 оказываются закрытыми. Элемент же И k открыт, и импульсы ff, генератора 7 поступают на вход вычитания счетчи ка 8, уменьшая его содержимое. При обнулении счетчика 8, фиксируемого дешифратором 9 триггеры 1 и 3 устанавливаются в нулевое состояние. Если в рассматриваемом цикле фазовый сдвиг между импульсами и остался таким же, как и в предыдущем цикле, то момент обнуления счетчика 8 совпадает с моментом поступления импуль са fgj., устанавливающего триггер 2 в нулевое состояние. Это означает, что в условиях постоянства фазового сдвига между импульсами f, и элементы И 5 и 6 все время остаются зак рытыми и содержимое счетчика 10 не изменяется. Если же фазовый сдвиг изменился, то обнуление счетчика 8 во времени не совпадает с поступлением импульса fjj. В этом случае триггеры 1 и 3 устанавливаются в нулевое состояние раньше (при увеличении фазового сдвига) или позже (при уменьшении фазового сдвига), чем триггер 2. Это означает, что элемент И 6 (при умень шении фазового сдвига) или элемент И 5 (при увеличении его) оказываются открытыми на время, равное приращению фазового сдвига в текущем цикле по сравнению с предыдущим. Таким образом на соответствующий вход реве сивного счетчика 10 от генератора. 7 поступает число импульсов, пропорциональное указанному приращению. Следовательно, цифровой компаратор отрабатывает рассогласования за один период сравниваемых частот. В режиме длительных или больших рассогласований, когда за один период частоты fgq не поступает ни одного импульса fjjj. (или наоборот), наступает либо полное заполнение счетчика 10, либо его обнуление. Эти крайние состояния счетчика 10 фиксируются

схемами блокировки 12 и 13 , запирающими соответственно элементы И 5 или И 6. Таким образом осуществляется блокировка компаратора от опрокидывания и ограничение его выходной величины.

Формула изобретения

Цифровой компаратор,содержащий два RS-триггера, прямой выход каждого из которых подключен к первому входу соответствующего элемента И, а выход - перекрестно к второму входу элементов И,выходы которых подключены к входам реверсивного счетчика,прямой и инверсный выходы которого соединены с входами соответствующих элементов блокировки, выход каждого из которых подключен к третьему входу соответствующего ; элемента И, четвертый вход каждого из которых подключен в выходу генератора импульсов, причем первые входы RS-триггеров,подключены к шине опорной частоты, о вторые входы к выходам соответственно частотного датчика скорости и дешифратора, о тличающийся тем, что, с целью расширения функциональных возможностей, в него введены последовательно соединенные третий RS-триггер, третий элемент И, а также последовательно соединенные блок кодовых вентилей и вычитающим счетчик, выход которого подключен к входу flemM0patopa, соединенного выходом с первым входом -третьего RS-триггера, второй вход которого соединен С шиной опорной частоты, второй вход вычитающего счетчика соединен с выходом третьего элемента И, второй вход которого подключен к выходу генератора импульсов, первый вход блока кодовых вентилей соединен с прямым выходом реверсивного счетчика и является выходом комплратора, а второй вход - с шиной опорной частоты. Источники информации, принятые во внимание при экспертизе 1.Мартяшин А. И.и др. Преобразователи электрических параметров для систем контроля и измерения. М., Энергия , 1976, с. 231-256. 2.Авторское свидсгельство СССР по заявке № 281 03/18-2, 1980 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU963034A1 |

| Следящий электропривод для разметки шкал | 1984 |

|

SU1228071A1 |

| Устройство для управления электрическим преобразователем с защитой от перенапряжений | 1990 |

|

SU1817217A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Генератор последовательности импульсов | 1983 |

|

SU1192120A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Авторы

Даты

1982-05-23—Публикация

1980-02-18—Подача