Изобретение относится к электросвязи, может использоваться для асинхронного ввода-вывода синхронных двоичных сигналов в цифровые тракты систем с импульсно-кодовой модуляцией, дельта-модуляцией и другими цифровыми методами модуляции и является усовершенствованием устройства по авт. св. № 1285608.

Цель изобретения - повышение точности сопряжения цифровых последовательностей .

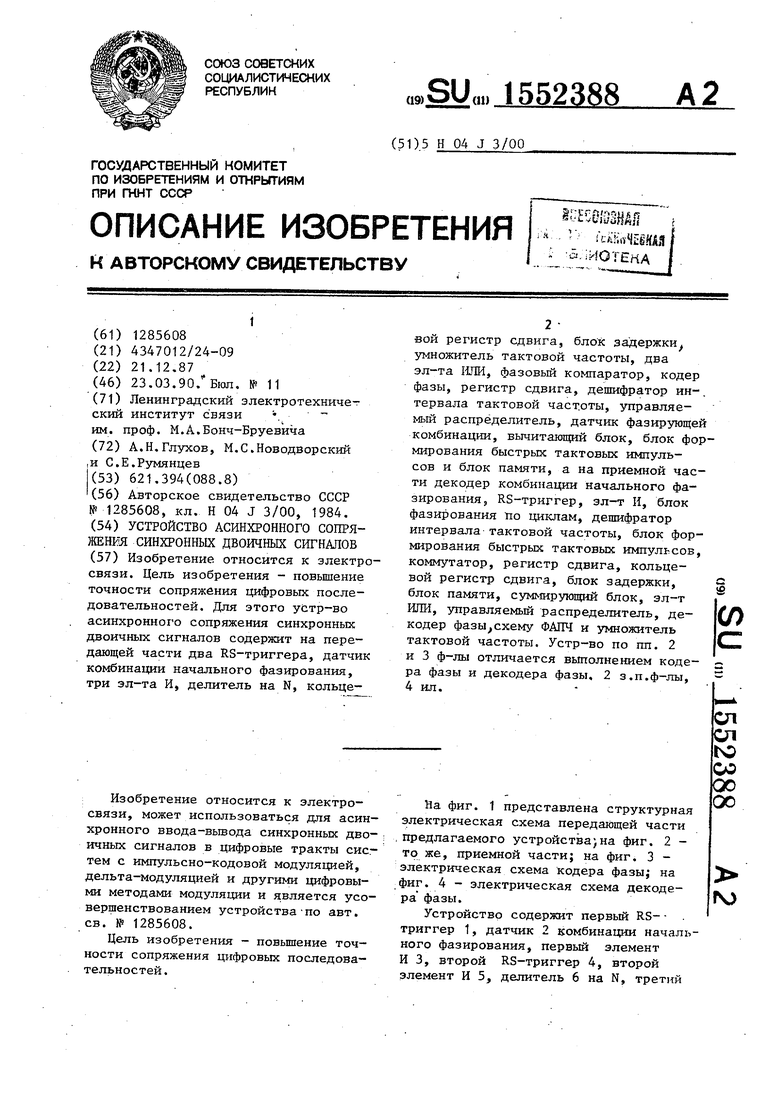

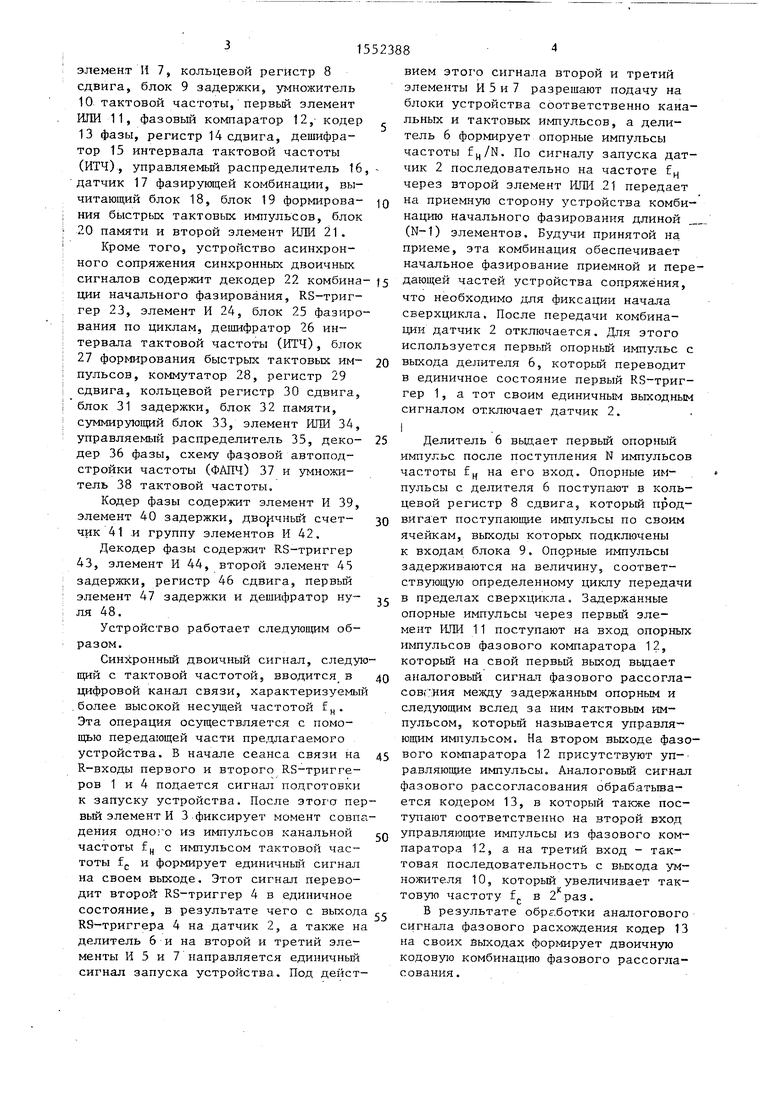

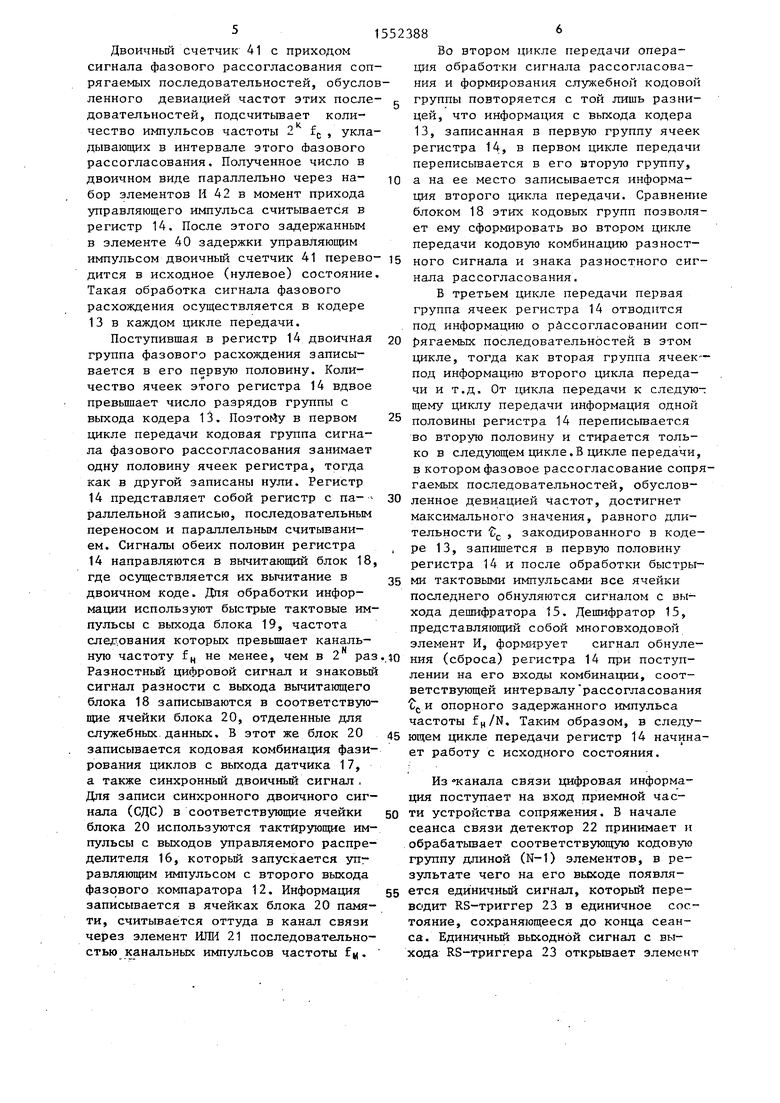

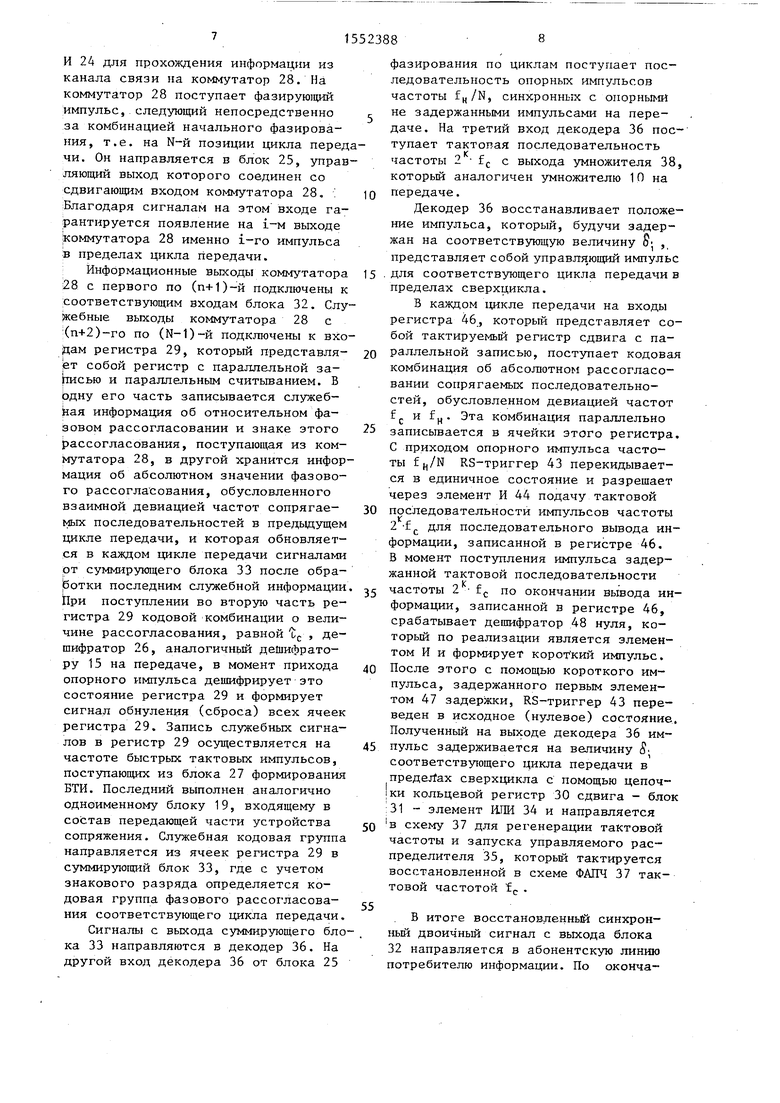

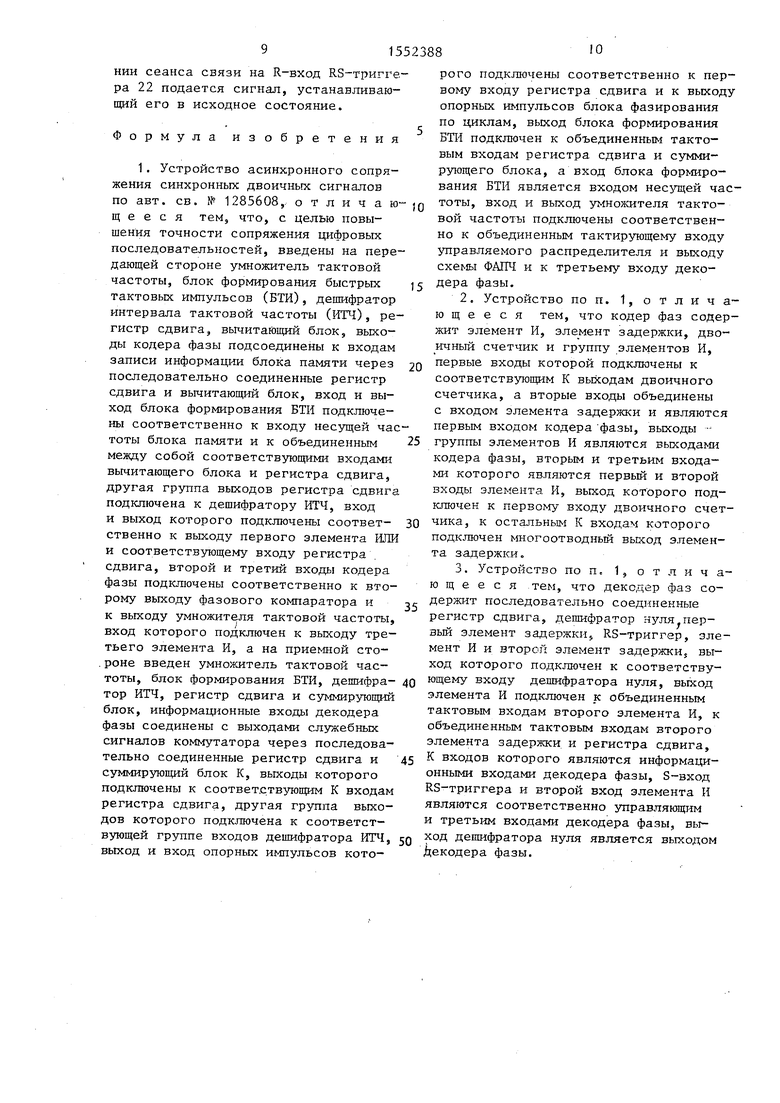

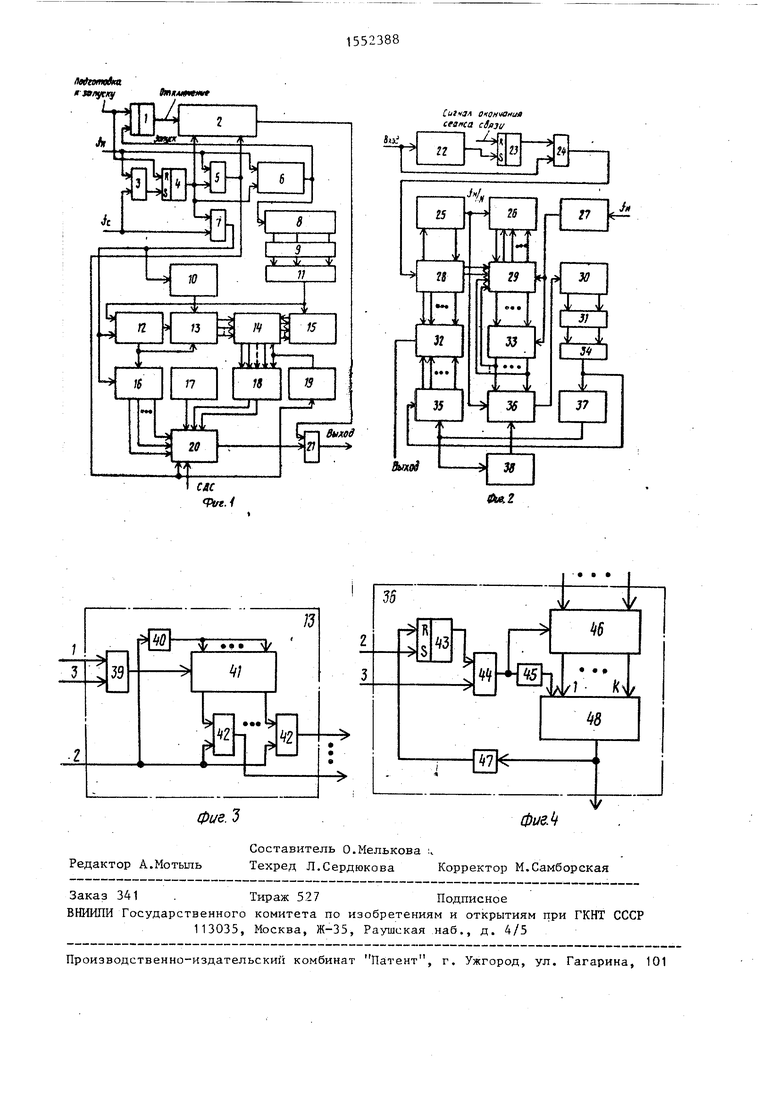

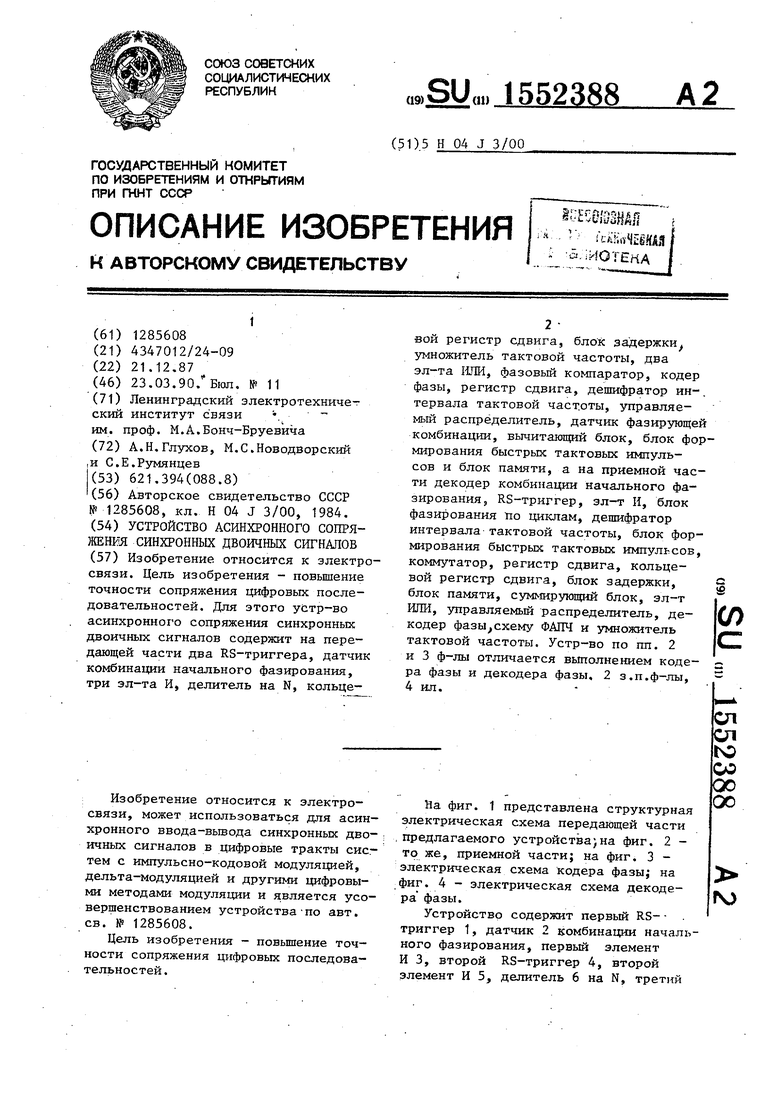

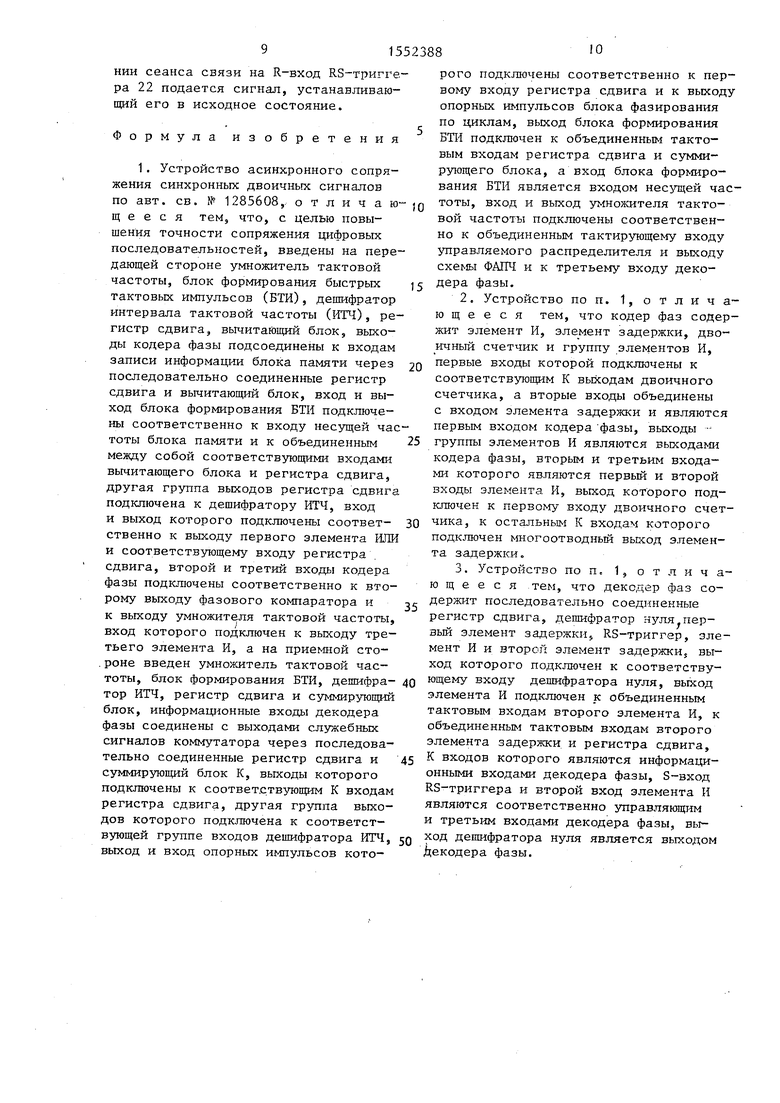

На фиг. 1 представлена структурная электрическая схема передающей части предлагаемого устройства;на фиг. 2 - то же, приемной части; на фиг. 3 - электрическая схема кодера фазы; на фиг. 4 - электрическая схема декодера фазы.

Устройство содержит первый RS- триггер 1, датчик 2 комбинации начального фазирования, первый элемент ИЗ, второй RS-триггер 4, второй элемент И 5, делитель 6 на N, третий

СЛ СП N5

GO ОО 00

N)

элемент И 7, кольцевой регистр 8 сдвига, блок 9 задержки, умножитель 10 тактовой частоты, первый элемент ИЛИ 11, фазовый компаратор 12, кодер 13 фазы, регистр 14 сдвига, дешифратор 15 интервала тактовой частоты (ИТЧ), управляемый распределитель 16 датчик 17 фазирующей комбинации, вычитающий блок 18, блок 19 формирования быстрых тактовых импульсов, блок 20 памяти и второй элемент ИЛИ 21.

Кроме того, устройство асинхронного сопряжения синхронных двоичных

вием этого сигнала второй и третий элементы И 5 и 7 разрешают подачу на блоки устройства соответственно канальных и тактовых импульсов, а делитель 6 формирует опорные импульсы частоты Гц/N. По сигналу запуска датчик 2 последовательно на частоте fH через второй элемент ИЛИ 21 передает на приемную сторону устройства комбинацию начального фазирования длиной (N-1) элементов. Будучи принятой на приеме, эта комбинация обеспечивает начальное фазирование приемной и пере

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности сопряжения цифровых последовательностей. Для этого устройство асинхронного сопряжения синхронных двоичных сигналов содержит на передающей части два RS-триггера, датчик комбинации начального фазирования, три эл-та И, делитель на N, кольцевой регистр сдвига, блок задержки, умножитель тактовой частоты, два эл-та ИЛИ, фазовый компаратор, кодер фазы, регистр сдвига, дешифратор интервала тактовой частоты, управляемый распределитель, датчик фазирующей комбинации, вычитающий блок, блок формирования быстрых тактовых импульсов и блок памяти, а на приемной части декодер комбинации начального фазирования, RS-триггер, эл-т И, блок фазирования по циклам, дешифратор интервала тактовой частоты, блок формирования быстрых тактовых импульсов, коммутатор, регистр сдвига, кольцевой регистр сдвига, блок задержки, блок памяти, суммирующий блок, эл-т ИЛИ, управляемый распределитель, декодер фазы, схему ФАПЧ и умножитель тактовой частоты. Устройство по п.п. 2 и 3 ф-лы отличается выполнением кодера фазы и декодера фазы. 2 з.п. ф-лы, 4 ил.

20

25

30

сигналов содержит декодер 22 комбиня- 15 дающей частей устройства сопряжения, ции начального фазирования, RS-триг- гер 23, элемент И 24, блок 25 фазирования по циклам, дешифратор 26 интервала тактовой частоты (ИТЧ), блок 27 формирования быстрых тактовых импульсов, коммутатор 28, регистр 29 сдвига, кольцевой регистр 30 сдвига, блок 31 задержки, блок 32 памяти, суммирующий блок 33, элемент ИЛИ 34, управляемый распределитель 35, декодер 36 фазы, схему фадовой автоподстройки частоты (ФАПЧ) 37 и умножитель 38 тактовой частоты.

Кодер фазы содержит элемент И 39, элемент 40 задержки, двоичный счетчик 41 и группу элементов И 42.

Декодер фазы содержит RS-триггер 43, элемент И 44, второй элемент 45 задержки, регистр 46 сдвига, первьм элемент 47 задержки и дешифратор нуля 48.

Устройство работает следующим образом.

Синхронный двоичный сигнал, следующий с тактовой частотой, вводится в до цифровой канал связи, характеризуемый более высокой несущей частотой fH. Эта операция осуществляется с помощью передающей части предлагаемого устройства. В начале сеанса связи на R-входы первого и второго RS-тригге- ров 1 и 4 подается сигнал подготовки к запуску устройства. После этого первый элемент И 3 фиксирует момент совпадения одного из импульсов канальной

35

45

50

что необходимо для фиксации начала сверхцикла. После передачи комбинации датчик 2 отключается. Для этого используется первый опорный импульс с выхода делителя 6, который переводит в единичное состояние первый RS-триггер 1, а тот своим единичным выходным сигналом отключает датчик 2.

Делитель 6 выдает первый опорный импульс после поступления N импульсов частоты на его вход. Опорные импульсы с делителя 6 поступают в кольцевой регистр 8 сдвига, который продвигает поступающие импульсы по своим ячейкам, выходы которых подключены к входам блока 9. Опорные импульсы задерживаются на величину, соответствующую определенному циклу передачи в пределах сверхцикла. Задержанные опорные импульсы через первый элемент ИЛИ 11 поступают на вход опорных импульсов фазового компаратора 12, который на свой первый выход выдает аналоговый сигнал фазового рассогла- совгння между задержанным опорным и следующим вслед за ним тактовым импульсом, который называется управляющим импульсом. На втором выходе фазо вого компаратора 12 присутствуют управляющие импульсы. Аналоговый сигнал фазового рассогласования обраб ггыва- ется кодером 13, в который также поступают соответственно на второй вход управляющие импульсы из фазового компаратора 12, а на третий вход - тактовая последовательность с выхода умножителя 10, который увеличивает тактовую частоту ff в 2 раз.

частоты fH с импульсом тактовой частоты fc и формирует единичный сигнал на своем выходе. Этот сигнал переводит второй RS-триггер 4 в единичное состояние, в результате чего с выхода RS-триггера 4 на датчик 2, а также на делитель 6 и на второй и третий элементы И 5 и 7 направляется единичный сигнал запуска устройства. Под дейст0

5

0

5 дающей частей устройства сопряжения,

о 35

45

50

5

что необходимо для фиксации начала сверхцикла. После передачи комбинации датчик 2 отключается. Для этого используется первый опорный импульс с выхода делителя 6, который переводит в единичное состояние первый RS-триггер 1, а тот своим единичным выходным сигналом отключает датчик 2.

Делитель 6 выдает первый опорный импульс после поступления N импульсов частоты на его вход. Опорные импульсы с делителя 6 поступают в кольцевой регистр 8 сдвига, который продвигает поступающие импульсы по своим ячейкам, выходы которых подключены к входам блока 9. Опорные импульсы задерживаются на величину, соответствующую определенному циклу передачи в пределах сверхцикла. Задержанные опорные импульсы через первый элемент ИЛИ 11 поступают на вход опорных импульсов фазового компаратора 12, который на свой первый выход выдает аналоговый сигнал фазового рассогла- совгння между задержанным опорным и следующим вслед за ним тактовым импульсом, который называется управляющим импульсом. На втором выходе фазового компаратора 12 присутствуют управляющие импульсы. Аналоговый сигнал фазового рассогласования обраб ггыва- ется кодером 13, в который также поступают соответственно на второй вход управляющие импульсы из фазового компаратора 12, а на третий вход - тактовая последовательность с выхода умножителя 10, который увеличивает тактовую частоту ff в 2 раз.

В результате обработки аналогового сигнала фазового расхождения кодер 13 на своих выходах формирует двоичную кодовую комбинацию фазового рассогласования .

ную частоту fH не менее, чем в 2N раз Разностный цифровой сигнал и знаковый сигнал разности с выхода вычитающего блока 18 записываются в соответствующие ячейки блока 20, отделенные для служебных данных. В этот же блок 20 записывается кодовая комбинация фазирования циклов с выхода датчика 17, а также синхронный двоичный сигнал , Для записи синхронного двоичного сигнала (СДС) в соответствующие ячейки блока 20 используются тактирующие импульсы с выходов управляемого распределителя 16, который запускается управляющим импульсом с второго выхода фазового компаратора 12. Информация записывается в ячейках блока 20 памяти, считывается оттуда в канал связи через элемент ИЛИ 21 последовательностью канальных импульсов частоты fц,

Двоичный счетчик 41 с приходом сигнала фазового рассогласования сопрягаемых последовательностей, обусловленного девиацией частот этих после- довательностей, подсчитывает количество импульсов частоты 2 fc , укладывающих в интервале этого Фазового рассогласования. Полученное число в двоичном виде параллельно через набор элементов И 42 в момент прихода управляющего импульса считывается в регистр 14. После этого задержанным в элементе 40 задержки управляющим импульсом двоичный счетчик 41 переводится в исходное (нулевое) состояние. Такая обработка сигнала фазового расхождения осуществляется в кодере

13в каждом цикле передачи. Поступившая в регистр 14 двоичная

группа фазового расхождения записывается в его первую половину. Количество ячеек этого регистра 14 вдвое превышает число разрядов группы с выхода кодера 13. Поэтому в первом цикле передачи кодовая группа сигнала фазового рассогласования занимает одну половину ячеек регистра, тогда как в другой записаны нули. Регистр

14представляет собой регистр с параллельной записью, последовательным переносом и параллельным считыванием. Сигналы обеих половин регистра

14 направляются в вычитающий блок 18, где осуществляется их вычитание в двоичном коде. Для обработки информации используют быстрые тактовые импульсы с выхода блока 19, частота следования которых превышает каналь

0

,

5

0

5

0

5

0

5

0

5

Во втором цикле передачи операция обработки сигнала рассогласования и формирования служебной кодовой группы повторяется с той лишь разницей, что информация с выхода кодера 13, записанная в первую группу ячеек регистра 14, в первом цикле передачи переписывается в его вторую группу, а на ее место записывается информация второго цикла передачи. Сравнение блоком 18 этих кодовых групп позволяет ему сформировать во втором цикле передачи кодовую комбинацию разностного сигнала и знака разностного сигнала рассогласования.

В третьем цикле передачи первая группа ячеек регистра 14 отводится под информацию о рассогласовании сопрягаемых последовательностей в этом цикле, тогда как вторая группа ячеек- под информацию второго цикла передачи и т.д. От цикла передачи к следующему циклу передачи информация одной половины регистра 14 переписывается во вторую половину и стирается только в следующем цикле.В цикле передачи, в котором фазовое рассогласование сопрягаемых последовательностей, обусловленное девиацией частот, достигнет максимального значения, равного длительности Јс , закодированного в кодере 13, запишется в первую половину регистра 14 и после обработки быстрыми тактовыми импульсами все ячейки последнего обнуляются сигналом с выхода дешифратора 15. Дешифратор 15, представляющий собой многовходовой элемент И, формирует сигнал обнуления (сброса) регистра 14 при поступлении на его входы комбинации, соответствующей интервалу рассогласования Ср и опорного задержанного импульса частоты fH/N. Таким образом, в следующем цикле передачи регистр 14 начинает работу с исходного состояния.

Из «канала связи цифровая информация поступает на вход приемной части устройства сопряжения. В начале сеанса связи детектор 22 принимает и обрабатывает соответствующую кодовую группу длиной (N-1) элементов, в результате чего на его выходе появляется единичный сигнал, который переводит RS-триггер 23 в единичное состояние, сохраняющееся до конца сеанса. Единичный выходной сигнал с выхода RS-триггера 23 открывает элемент

И 24 для прохождения информации из канала связи на коммутатор 28. На коммутатор 28 поступает фазирукнций импульс, следующий непосредственно за комбинацией начального фазирования, т.е. на N-й позиции цикла передчи. Он направляется в блок 25, управляющий выход которого соединен со сдвигающим входом коммутатора 28. Благодаря сигналам на этом входе гарантируется появление на i-м выходе коммутатора 28 именно 1-го импульса в пределах цикла передачи.

Информационные выходы коммутатора 28 с первого по (п+1)-й подключены к соответствующим входам блока 32. Служебные выходы коммутатора 28 с (п+2)-го по (N-l)-ft подключены к входам регистра 29, который представля- ет собой регистр с параллельной записью и параллельным считыванием. В одну его часть записывается служебная информация об относительном фазовом рассогласовании и знаке этого рассогласования, поступающая из коммутатора 28, в другой хранится информация об абсолютном значении фазового рассогласования, обусловленного взаимной девиацией частот сопрягае- мых последовательностей в предыдущем цикле передачи, и которая обновляется в каждом цикле передачи сигналами от суммирующего блока 33 после обработки последним служебной информации При поступлении во вторую часть регистра 29 кодовой комбинации о величине рассогласования, равной 1С , дешифратор 26, аналогичный дешифратору 15 на передаче, в момент прихода опорного импульса дешифрирует это состояние регистра 29 и формирует сигнал обнуления (сброса) всех ячеек регистра 29. Запись служебных сигналов в регистр 29 осуществляется на частоте быстрых тактовых импульсов, поступающих из блока 27 формирования БТИ. Последний выполнен аналогично одноименному блоку 19, входящему в состав передающей части устройства сопряжения. Служебная кодовая группа направляется из ячеек регистра 29 в суммирующий блок 33, где с учетом знакового разряда определяется кодовая группа фазового рассогласова- ния соответствующего цикла передачи.

Сигналы с выхода суммирующего блока 33 направляются в декодер 36. На другой вход декодера 36 от блока 25

фазирования по циклам поступает последовательность опорных импульсов частоты fH/N, синхронных с опорными не задержанными импульсами на передаче. На третий вход декодера 36 поступает тактогая последовательность

tf

частоты 2 fc с выхода умножителя 38, который аналогичен умножителю 10 на передаче.

Декодер 36 восстанавливает положение импульса, который, будучи задержан на соответствующую величину О; , представляет собой управляющий импульс для соответствующего цикла передачи в пределах сверхцикла.

В каждом цикле передачи на входы регистра 46, который представляет собой тактируемый регистр сдвига с параллельной записью, поступает кодовая комбинация об абсолютном рассогласовании сопрягаемых последовательностей, обусловленном девиацией частот fc и fн. Эта комбинация параллельно записывается в ячейки этого регистра. С приходом опорного импульса частоты fH/N RS-триггер 43 перекидывается в единичное состояние и разрешает через элемент И 44 подачу тактовой последовательности импульсов частоты 2 -fc для последовательного вывода информации, записанной в регистре 46. В момент поступления импульса задержанной тактовой последовательности

о ь с

частоты / tc по окончании вывода информации, записанной в регистре 46, срабатывает дешифратор 48 нуля, который по реализации является элементом И и формирует корот кий импульс. После этого с помощью короткого импульса, задержанного первым элементом 47 задержки, RS-триггер 43 переведен в исходное (нулевое) состояние. Полученный на выходе декодера 36 импульс задерживается на величину .( соответствующего цикла передачи в предел ах сверхцикла с помощью цепоч- ки кольцевой регистр 30 сдвига - блок

31- элемент ИЛИ 34 и направляется в схему 37 для регенерации тактовой частоты и запуска управляемого распределителя 35, который тактируется восстановленной в схеме ФАГГЧ 37 тактовой частотой fc .

В итоге восстановленный синхронный двоичный сигнал с выхода блока

32направляется в абонентскую линию потребителю информации. По окончании сеанса связи на R-вход RS-тригге- ра 22 подается сигнал, устанавливающий его в исходное состояние.

Формула изобретения

тоты, блок формирования БТИ, дешифра- 40 юЩемУ входу дешифратора нуля, выход

элемента И подключен к объединенным тактовым входам второго элемента И, к объединенным тактовым входам второго элемента задержки и регистра сдвига, К входов которого являются информационными входами декодера фазы, S-вход RS-триггера и второй вход элемента И являются соответственно управляющим и третьим входами декодера фазы, выход дешифратора нуля является выходом декодера фазы.

тор ИТЧ, регистр сдвига и суммирующий блок, информационные входы декодера фазы соединены с выходами служебных сигналов коммутатора через последовательно соединенные регистр сдвига и суммирующий блок К, выходы которого подключены к соответствующим К входам регистра сдвига, другая группа выходов которого подключена к соответствующей группе входов дешифратора ИТЧ, выход и вход опорных импульсов кото45

50

5

Q 5 0

5

0

5

рого подключены соответственно к первому входу регистра сдвига и к выходу опорных импульсов блока фазирования по циклам, выход блока формирования БТИ подключен к объединенным тактовым входам регистра сдвига и суммирующего блока, а вход блока формирования БТИ является входом несущей частоты, вход и выход умножителя тактовой частоты подключены соответственно к объединенным тактирующему входу управляемого распределителя и выходу схемы ФАПЧ и к третьему входу декодера фазы.

с входом элемента задержки и являются первым входом кодера фазы, выходы группы элементов И являются выходами кодера фазы, вторым и третьим входа- Mi которого явпяются первый и второй входы элемента И, выход которого под- кппочен к первому входу двоичного счетчика, к остальным К входам которого подключен многоотводный выход эпемон- та задержки.

50

фие. 3

Составитель О.Мелькова . Редактор А.Мотыль Техред Л.Сердюкова Корректор М.Самборская

Заказ 341Тираж 577Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

фиг.1

| Авторское свидетельство СССР № 1285608, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-03-23—Публикация

1987-12-21—Подача