(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования аналогового сигнала в кодовые слова | 1981 |

|

SU1005303A2 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для измерения фазового сдвига отраженного сигнала | 1983 |

|

SU1167554A1 |

| Устройство для определения концентрации газа в жидкости | 1989 |

|

SU1658074A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1121691A1 |

| ПАРАМЕТРИЧЕСКИЙ ЭХОЛОКАТОР | 1989 |

|

RU1641102C |

| РАДИОЛОКАТОР-ИНТРОСКОП | 1994 |

|

RU2096767C1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ДАННЫХ ИЗМЕРЕНИЙ | 1993 |

|

RU2079892C1 |

1

Изобретение относится к импульсной технике.

Известен аналого-ии({|ровой преобразователь, содержащий последовательно соединенные операционный усилитель, блок сравнения, выполненный на транзисторах, генератор переменной частоты, однод&кадный счетчик, Шзшолненный на триггерах, цепочечный делитель, блок задержки, состоящий из двух параллельных цепей, каждая из которых содержит конденсатор и два переключаетлых полевых транзистора, выход схемы задержки соединен с неинвертируюшим входом операционного усилителя, входы операционного усилителя подключены к входным шинам, на которые подается аналоговый сигнал nont жительной и отрицательной полярности, однодекадный счетчик на триггерах ио« пользуется в цепи рециркуляции для преобразования аналогового сигнала в десятичный код l.

Недостатком известного устройства является низкое быстродействие.

Известен аналого-цифровой преобразователь, содержащий синхронизатор, ход которого соединен с управляющим : входом первого переключателя, инфс маиноиный вход которого пошиоо чен к входной шине, а втсфой нвформадиоиный вход и выход переклх чателя соединены с целью редиркулягага, содержащий блок сравнения и линюо задержки, 6х0д делителя мощности соешгtoнен с выходом переключателя, первый выход делителя мощности подключав к первому входу дополнительного блока сравневпя, выход допопнетепьного одноразрядисяо блока сравнения соединен с

IS регистрирующим блоком и входом атте-. HfoaTopa, выход аттенюатора и второй, выход делителя мощности подключены к входам основного блсжа сравнения, выход основного блока сравнения соединен с

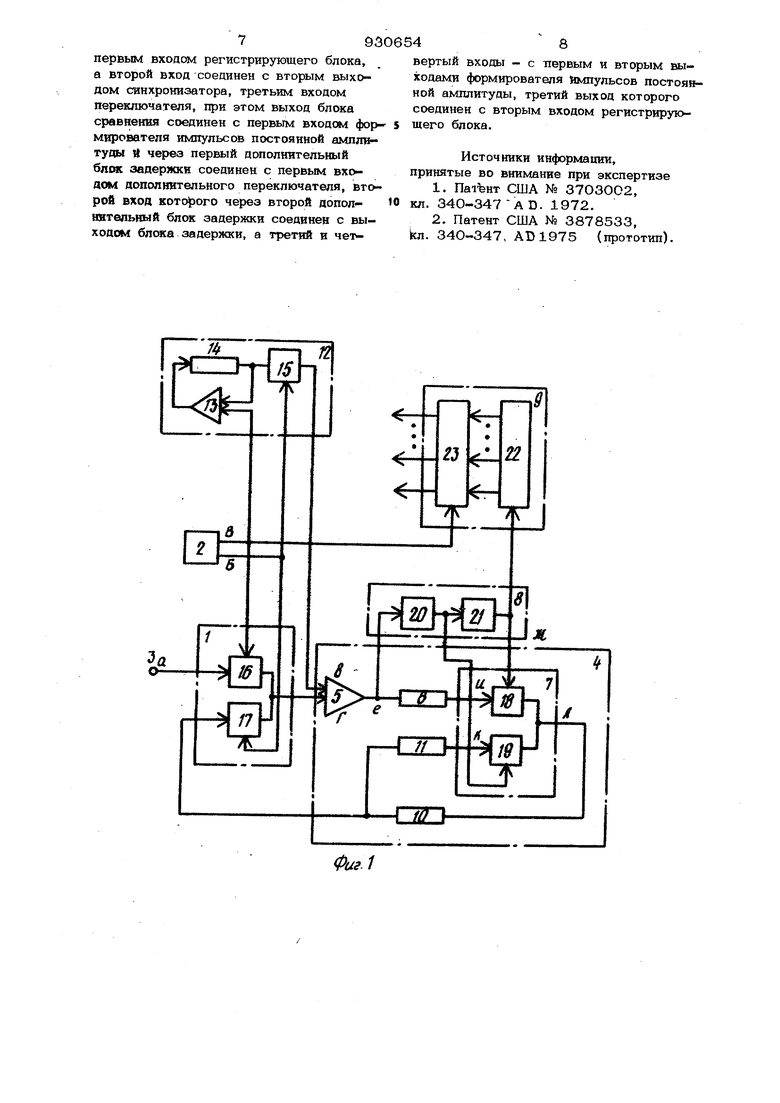

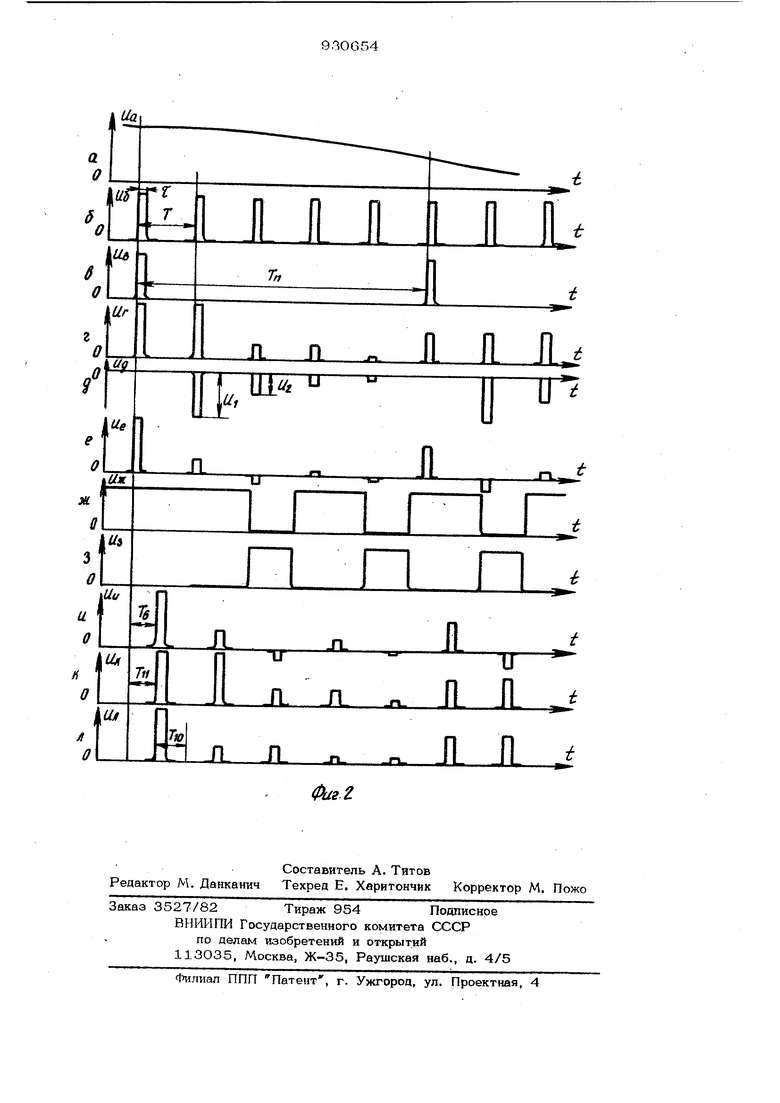

20 входом канала модулятора с жестким ограничителем, содержащим модулятор, линию задержки, ограничитель и демодулятор, выход канала одулятора подключей к входу усшштепя, выход усили теля соединен с входом переключателя, источник постоянного опорного напряжения подключен к второму входу дополнительного блока сравнения Г2 . Недостатками данного- устройства яв ляются низкие стабильность и быстродействие. Цель изобретения - повышение стаби ности работы, быстродействия и надежности. Указанная цель достигается тем, чч-о аналого-цифровой преобразователь, содер жаший фогыирователь опорных сигналов, регистрирующий блок, синхронизатор, первый выход которого соединен с первым входсфл переключателя, выход котор го соединен с входом блока срав нения, а второй вход с выходе блока задержки, введены два дополнительных блока задержки, формирователь импульсов постоянной амплитуды, дополнительный переключатель, выход которого соединен с входом блока задержки, причем второй вход блока сравнения соединен с а 1ходом формирователя опорных сигналов, первый вход которого соедине с первым входом переключателя и первым входе регистрирующего блока, вто рой вход - с вторым выходом синхронизатора и третьим входом переключателя, при этом выход блока сравнения соединен с первым входом формирователя импульсор постоянной амплитуды и через первый дополнительный блок задержки соединен с первым входом дополнительного переключателя, второй Вход которого через второй дополнйтель ный блок задержки соединен с вьгкоаом блока задержки, а третий и четвертый входы - с первым и вторым формирователя импульсов постоянной ам литуды, третий выход которого соединен с вторым входом регистрирующего блока На фиг. 1 приведена структурная электрическая схема устройства на фиг. 2 - временные диаграммы его работы. Устройство содержит егЬ переключатель 1, управляющий вход которого соединен с синхронизатором. 2, первый информационный вход переключателя 1 под ключен к входной шине 3, а второй информационный вход и выход соединены с рециркулятором 4, который содержит блок 5 сравнения, первый вход которого соединен с выходом переключателя 1, а выход - через блок 6 задержки с первым информационным входом переключателя 7, выход блока 5 через формирователь 8 импульсов постоянной амплитуды подключен к регистрирующему блоку 9 и управляющему входу переключателя 7, второй информационный вход и выход переключателя 7 соединены соответственно через блоки 10 и 11 задержки с вторым информационным входом переключателя 1, формирователь 12 опорных сигналов содержит эмиттерный повторитель 13, охваченный петлей задержанной обратной связи с блоком 14 задержки и переключатель 15, управляющий вход которого подключен к синхронизатору 2, выход формирователя 12 соединен с вторым входом блока 5, блоки 6, 1О и 11 могут иметь полосковое исполнение, переключатель 1 состоит из аналоговых ключей 16 и 17, выходы которых подключены к выходу переключателя 1, переклк чатель 7 состоит из аналогично соединенных аналоговых ключей 18 к 19, аналоговые ключи 16 - 19 и переключатель 15выполнены на диодах Шоттки и отпи раются положительным потенциалом, поступающим на соответствующие управлякнщие входы переключателей 17 и 15, формирователь 8 состоит из последовательно соединенных кипп-реле 20, которые запускаются импульсами отрицательной полярности, и инвертора 21, регистрирующий блок 9 состоит из блока 22 задержки с отводами, соединенными с буферным запоминающим устройством 23, выполненным в виде набора триггеров. Аналогс -ци(}5)овой преобразователь работает следующим образом. Сигнал X (фиг. 2, ), подвергаемый преобразованию поступает на входную шину 3. Синхронизатор 2 вырабатывает две последовательности импульсов дли тельностью Т с периодом такта Т (фиг. 2, б) и с кратным ему периодом преобраз( (п+1) (фиг. 2, &), где п - разрядность устройства. Импульс второй последовательности юступает на управляющий вход аналогового ключа 16переключателя 1 и осуществляет стробирование входного аналогового сигнала (фиг. 2 г). Одновременно этим же импульсом осуществляется запуск источника, который с периодом Т, равным времени задержки блока 14, вырабатывает импульсы отрицательной полярности с амшгатудой, убывающей по логарифмическому закону е основанием 2 (фиг. 2,3). Входной сигнал х циркулирует по цепи: первый информационный вход переключателя 1, блок 5, блок 6,

59306546

переключатель 7, блок 10, второй инфор- положительный импульс длительностью мационный вход переключателя 1. Задери- более Т/2 (фиг. 2,3 ), который отпирает жавшись в этой цепи на время где T и Tjo время задержки блоков задержки 6 и 1О, информационный сирнал X одновременно с опорным сигналом высшего разряда 0 поступает в блок 5. В блоке 5 сравнения происходит вычитание амплитуды опорного напряжения U из амплитуды аналогового сигнала X . Одновременность поступления сравниваемых сигналов на входы блока 5 обеопечивается подачей синхроимпульсов с периодом Т с синхронизатора 2 на а дало говый ключ 17 переключателя 1 и на переключатель 15. В зависимости от полярности разностного сигнала Д U X - U., дальнейшая работа преобразователя происходит по разному. 1. Д U О . Это означает, что в высшем разряде устройства запишется 1 и соответствующая информация через формирователь 8 поступает на регистрирующий блок 9. В этом момент. т. е. через время Т после подачи Bxofie ного сигнала, заканчивается первый такт преобразования. Разностный сигнал (фиг. 2,е), пройдя блок задержки, поотупает на первый информационный вход переключателя 7 и на формирователь 8, при этом на выходе кишь-реле 20 потевциал будет равным нулю (фиг. 2,д), вследствие чего остается закрытым аналоговый ключ 19 переключателя 7, а на выходе инвертора 21 потенциал остается положительным (4мг. 2, ) и анало говый ключ 18 будет открыт. Этот же положительный потенциал поступает на регистрирующий блок 9. Разностный сигнал, пройдя блок 6 (фиг. 2, и ), переключатель 7 (фиг. 2,п), блок 10 и пореключатель 1 через время Т ,.2Т после начала преобразования поступает На первый вход блока 5 (фиг. 2, t). В это же время на второй вход блока 5 от формирователя 12 поступит опорный

сигнал второго разряда с амплитудой Uo (фиг. 2, д). При этом ча выходе блока 5 получается сигнал остатка второго разряда (фиг. 2, е). Так заканчивается второй такт преобразования.

сравнения, а второй вход соединен с вь коаам блока задержки, отличающийся т&л, что, с .целью повышо ния стабильности работы, быстродействия в надежности, введены два дополнительных блока задержки, формирователь вм- пульсов постоянной амплитуды и дополнительный переключатель, выход которого соединен с входом блока задержки, прин:чем второй вход блока сравнения соединен с выход(мл формирователя (торных сигналов, первый вход которого соединен с первым входом переключателя, аналоговый ключ 19 переключателя 7 и одновременно, пройдя через инвертор 21 {фиг. 2,:), запирает аналоговый ключ 18. На второй информационный вход переключателя 7 поступает сигнал X (фиг. 2, К ) циркулировавший дй этого момента по цепи: выход переключателя 7, блок 10, блок 11, второй информацирн- ный вход переключателя 7. Пройдя пер&ключатель 7 (фиг. 2,А), блок 10, пер ключатель 1 (фиг. 2,1,}, информационный сигнал х поступает на первый вход блока 5 через время noc-,u ле начала преобразования, где вре мя задержки блока 11. В это же время на второй вход блока 5 от формирователя 12 поступает оперный сигнал второго разряда с амплитудой и(5(фиг. 2, а). При этом на выходе блока 5 появляется сигнал остатка второго разряда (фиг. 2,е ). Далре на третье такте происходит |повторенне одной из описанных выше npoiцедур, в зависимости от полярности ра костного сигнала. Основным преимуществом предлагаемого устройства по сравнению с известным является увеличение быстродействия за счет уменьшения в цепи рециркуляции активных элетлентов. Быстродействие увеличивается также благодаря тому, что активные элементы блока сравнения работают в линейном режиме, Формула изобретения Аналснго- ц«||ровой преобразователь, с держашнй фо1 1ирователь опорных сигналов, регистрирующий блок, синхронизатор, первый выход которого соединен с входом переключателя, выход которого соедш ев с первым входом блока

первым входом регистрирующего блока, а второй вход соединен с вторым выходом синхронизатора, третьим входом переключателя, при этом выход блока сравнения соединен с первым входом формироватедя импульсов постоянной амплв туды и через первый дополнительный блок задержки соединен с первым входом дополнительного переключателя, второй вход через второй дополивтвльный блок задержки соединен с выходом блока задержки, а третий и четвертый входы - с тгервым и вторым выходами формирователя импульсов пocтoя ной амплитуды, третий выход которого соединен с вторым входом регистрирук щего блока.

Источники информации, принятые во внимание при экспертизе

kn. 34О-347, AD 1975 (прототип).

Авторы

Даты

1982-05-23—Публикация

1980-02-15—Подача