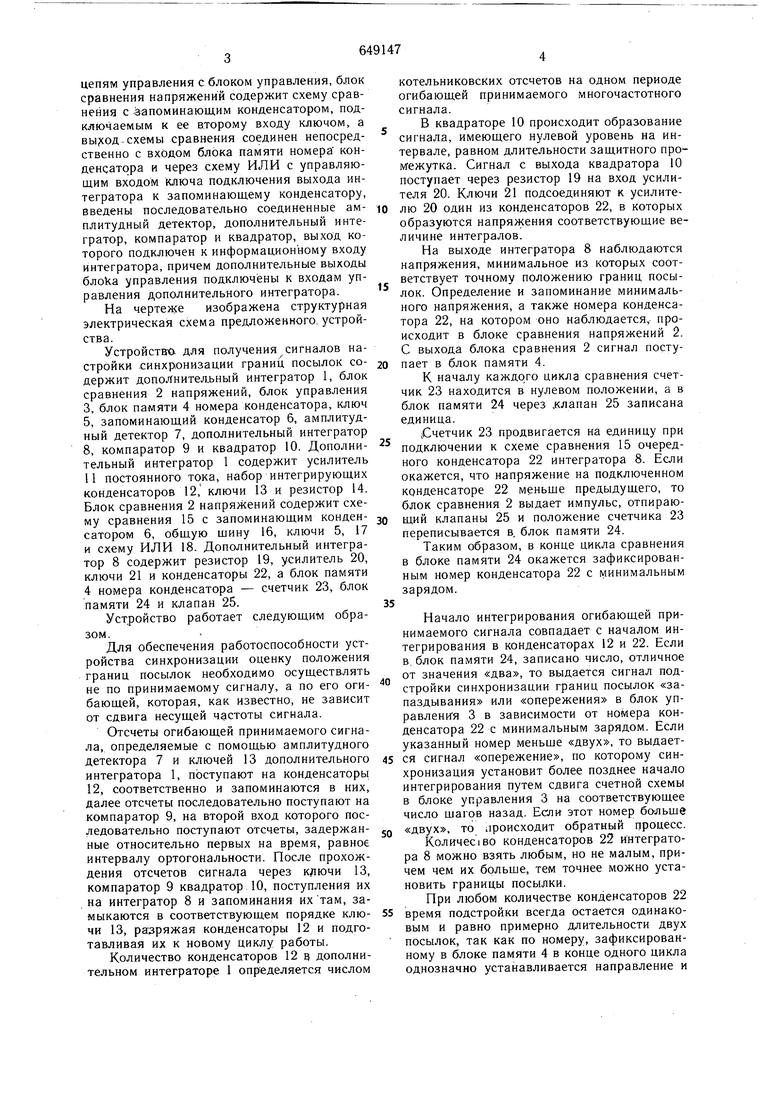

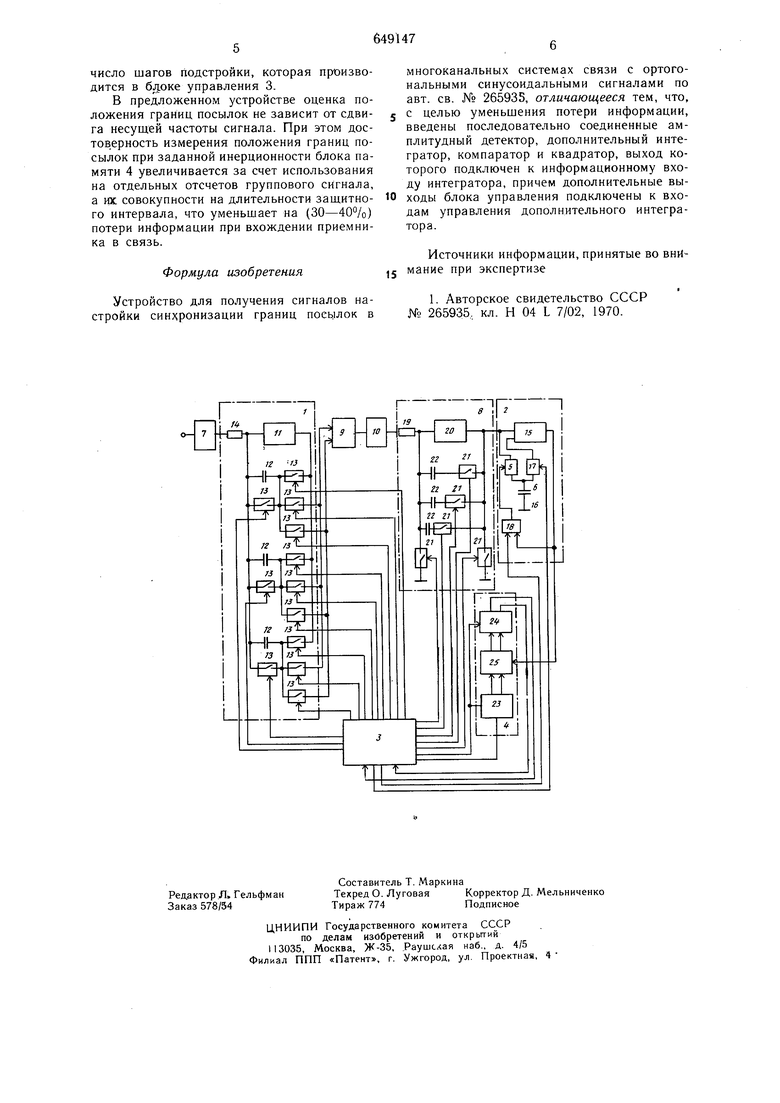

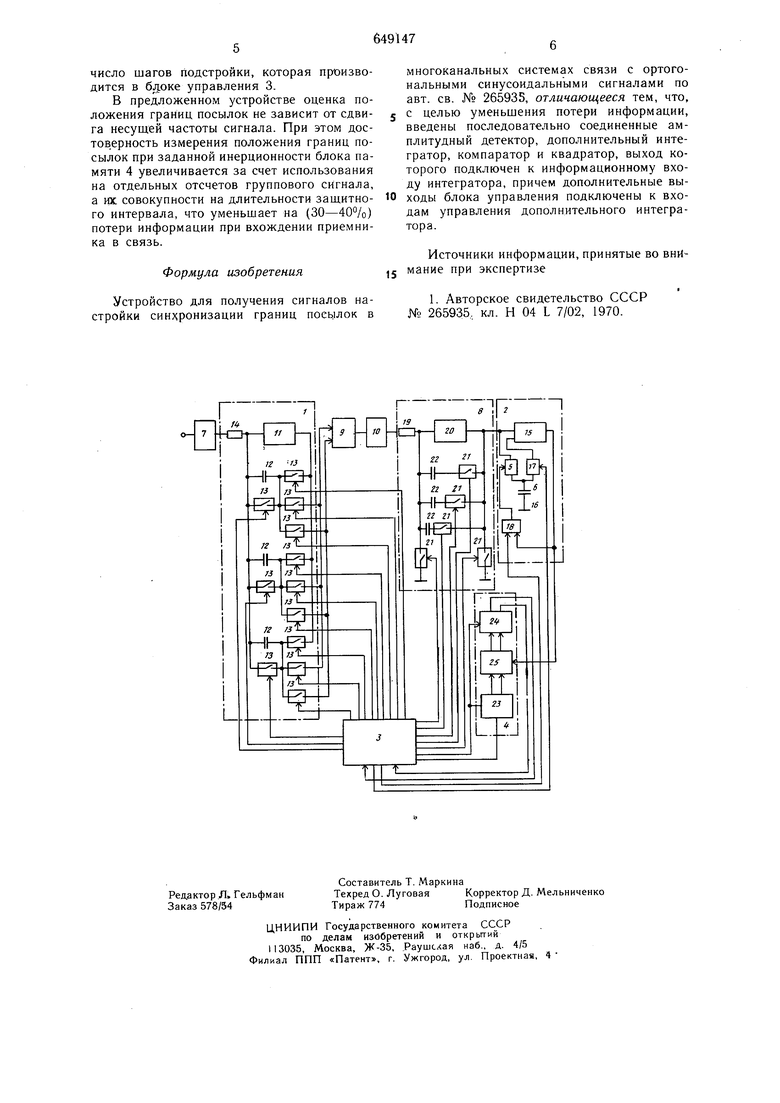

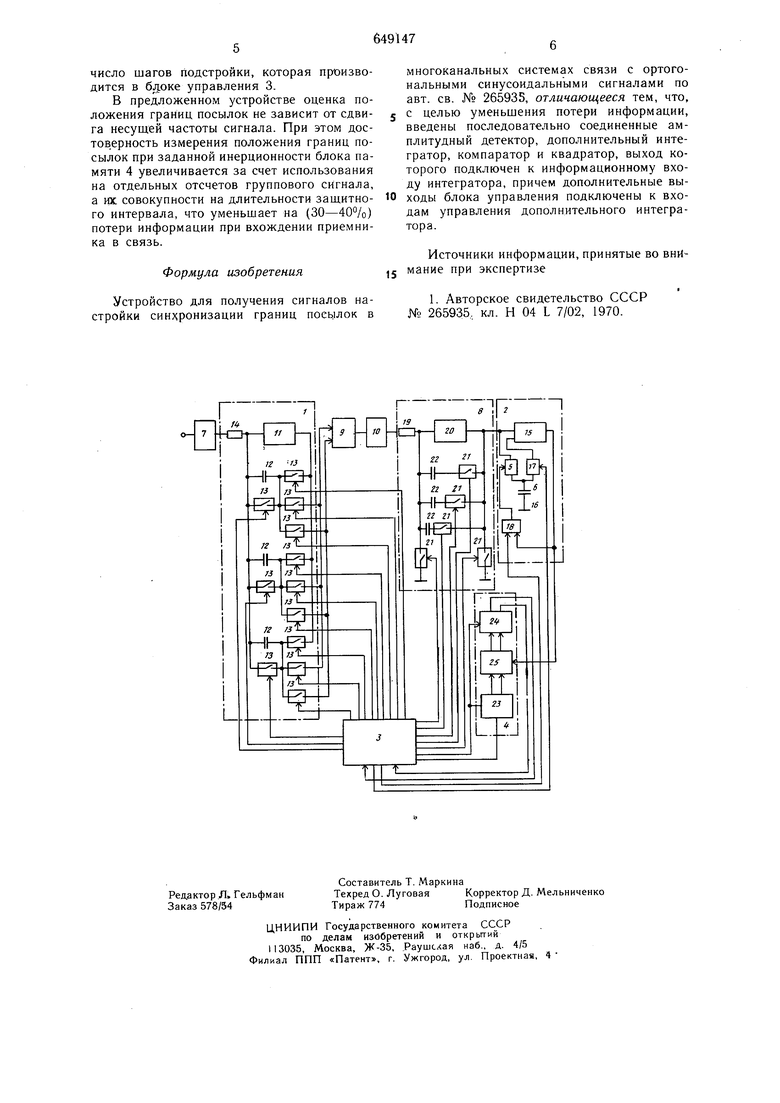

цепям управления с блоком управления, блок сравнения напряжений содержит схему сравнения с -запоминающим конденсатором, подключаемым к ее второму входу ключом, а вы од-схемы сравнения соединен непосредственно с входом блока памяти номера конденсатора и через схему ИЛИ с управляющим входом ключа подключения выхода интегратора к запоминающему конденсатору, введены последовательно соединенные амплитудный детектор, дополнительный интегратор, компаратор и квадратор, выход которого подключен к информационному входу интегратора, причем дополнительные выходы блоКа управления подключены к входам управления дополнительного интегратора. На чертеже изображена структурная электрическая схема предложенного устройства. Устройствах для получения сигналов настройки .синхронизации границ посылок содержит дополнител.ьный интегратор 1, блок сравнения 2 напряжений, блок управления 3, блок памяти 4 номера конденсатора, ключ 5, запоминающий конденсатор 6, амплитудный детектор 7, дополнительный интегратор 8, компаратор 9 и квадратор 10. Дополнительный интегратор 1 содержит усилитель 11 постоянного тока, набор интегрирующих конденсаторов 12, ключи 13 и резистор 14. Блок сравнения 2 напряжений содержит схему сравнения 15 с запоминающим конденсатором 6, общую щину 16, ключи 5, 17 и схему ИЛИ 18. Дополнительный интегратор 8 содержит резистор 19, усилитель 20, ключи 21 и конденсаторы 22, а блок памяти 4 номера конденсатора - счетчик 23, блок памяти 24 и клапан 25. Устройство работает следующим образом. Для обеспечения работоспособности устройства синхронизации оценку положения границ посылок необходимо осуществлять не по принимаемому сигналу, а по его огибающей, которая, как известно, не зависит от сдвига несущей частоты сигнала. Отсчеты огибающей принимаемого сигнала, определяемые с помощью амплитудного детектора 7 и ключей 13 дополнительного интегратора 1, поступают на конденсаторы 12, соответственно и запоминаются в них, далее отсчеты последовательно поступают на компаратор 9, на второй вход которого последовательно поступают отсчеты, задержанные относительно первых на время, равное интервалу ортогональности. После прохождения отсчетов сигнала через к/1ючи 13, компаратор 9 квадратор 10, поступления их на интегратор 8 и запоминания ихтам, замыкаются в соответствующем порядке ключи 13, разряжая конденсаторы 12 и подготавливая их к новому циклу работы. Количество конденсаторов 12 в дополнительном интеграторе 1 определяется числом котельниковских отсчетов на одном периоде огибающей принимаемого многочастотного сигнала. В квадраторе 10 происходит образование сигнала, имеющего нулевой уровень на интервале, равном длительности защитного промежутка. Сигнал с выхода квадратора 10 поступает через резистор 19 на вход усилителя 20. Ключи 21 подсоединяют к усилителю 20 один из конденсаторов 22, в которых образуются напряжения соответствующие величине интегралов. На выходе интегратора 8 наблюдаются напряжения, минимальное из которых соответствует точному положению границ посылок. Определение и запоминание минимального напряжения, а также номера конденсатора 22, на котором оно наблюдается, происходит в блоке сравнения напряжений 2. С выхода блока сравнения 2 сигнал поступает в блок памяти 4. К началу каждого цикла сравнения счетчик 23 находится в нулевом положении, а в блок памяти 24 через .клапан 25 записана единица. ;Счетчик 23 продвигается на единицу при подключении к схеме сравнения 15 очередного конденсатора 22 интегратора 8. Если окажется, что напряжение на подключенном конденсаторе 22 меньще предыдущего, то блок сравнения 2 выдает импульс, отпирающий клапаны 25 и положение счетчика 23 переписывается в. блок памяти 24. Таким образом, в конце цикла сравнения в блоке памяти 24 окажется зафиксированным номер конденсатора 22 с минимальным зарядом. Начало интегрирования огибающей принимаемого сигнала совпадает с началом интегрирования в конденсаторах 12 и 22. Если в. блок памяти 24, записано число, отличное от значения «два, то выдается сигнал подстройки синхронизации границ посылок «запаздывания или «опережения в блок управления 3 в зависимости от номера конденсатора 22 с минимальным зарядом. Если указанный номер меньще «двух, то выдается сигнал «опережение, по которому синхронизация установит более позднее начало интегрирования путем сдвига счетной схемы в блоке управления 3 на соответствующее число шагов назад. Если этот номер больше «двух, то происходит обратный процесс. Количес1во конденсаторов 22 интегратора 8 можно взять любым, но не малым, причем чем их больше, тем точнее можно установить границы посылки. При любом количестве конденсаторов 22 время подстройки всегда остается одинаковым и равно примерно длительности двух посылок, так как по номеру, зафиксированному в блоке памяти 4 в конце одного цикла однозначно устанавливается направление и

число шагов подстройки, которая производится в бяоке управления 3.

В предложенном устройстве оценка положения границ посылок не зависит от сдвига несущей частоты сигнала. При этом достов.ерность измерения положения границ посылок при заданной инерционности блока памяти 4 увеличивается за счет использования на отдельных отсчетов группового сигнала, а их совокупности на длительности защитного интервала, что уменьшает на (30-40%) потери информации при вхождении приемника в связь.

Формула изобретения

Устройство для получения сигналов настройки синхронизации границ посылок в

многоканальных системах связи с ортогональными синусоидальными сигналами по авт. св. № 265935, отличающееся тем, что,

с целью уменьщения потери информации, введены последовательно соединенные амплитудный детектор, дополнительный интегратор, компаратор и квадратор, выход которого подключен к информационному входу интегратора, причем дополнительные выходы блока управления подключены к входам управления дополнительного интегратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 265935, кл. Н 04 L 7/02, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Когерентный демодулятор сигналов | 1984 |

|

SU1243152A1 |

| Корреляционный демодулятор сигналов с угловой модуляцией | 1983 |

|

SU1166338A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| Регенератор цифрового сигнала | 1982 |

|

SU1083351A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ по РАБОЧЕМУ СИГНАЛУ | 1967 |

|

SU195495A1 |

| Устройство для некогерентного приема сигналов с относительной фазовой манипуляцией | 1985 |

|

SU1396291A1 |

| Дельта-модулятор для передачи речевых сигналов | 1990 |

|

SU1795554A1 |

Авторы

Даты

1979-02-25—Публикация

1977-01-06—Подача