Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания радиоэлектронной аппаратуры повышенной надежности для стабилизации постоянного напряжения.

Целью изобретения является повы- шение функциональной надежности при сохранении качества выходного напряжения и обеспечение модульного построения из унифицированных модулей одного типао

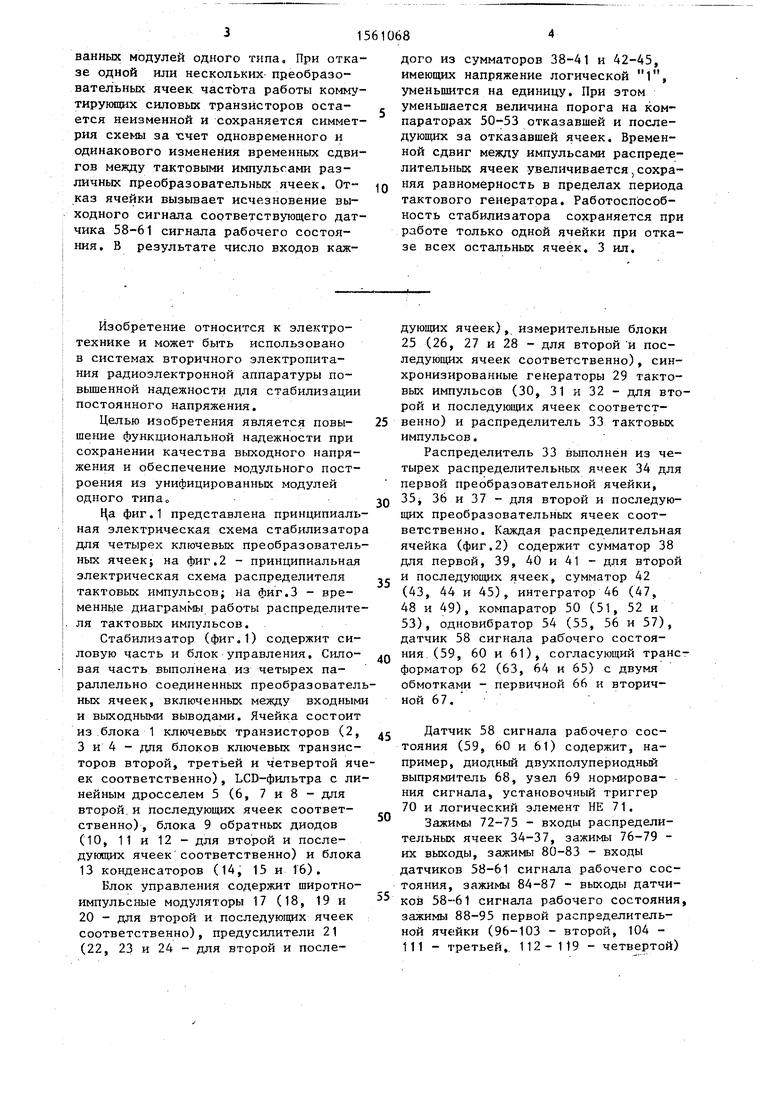

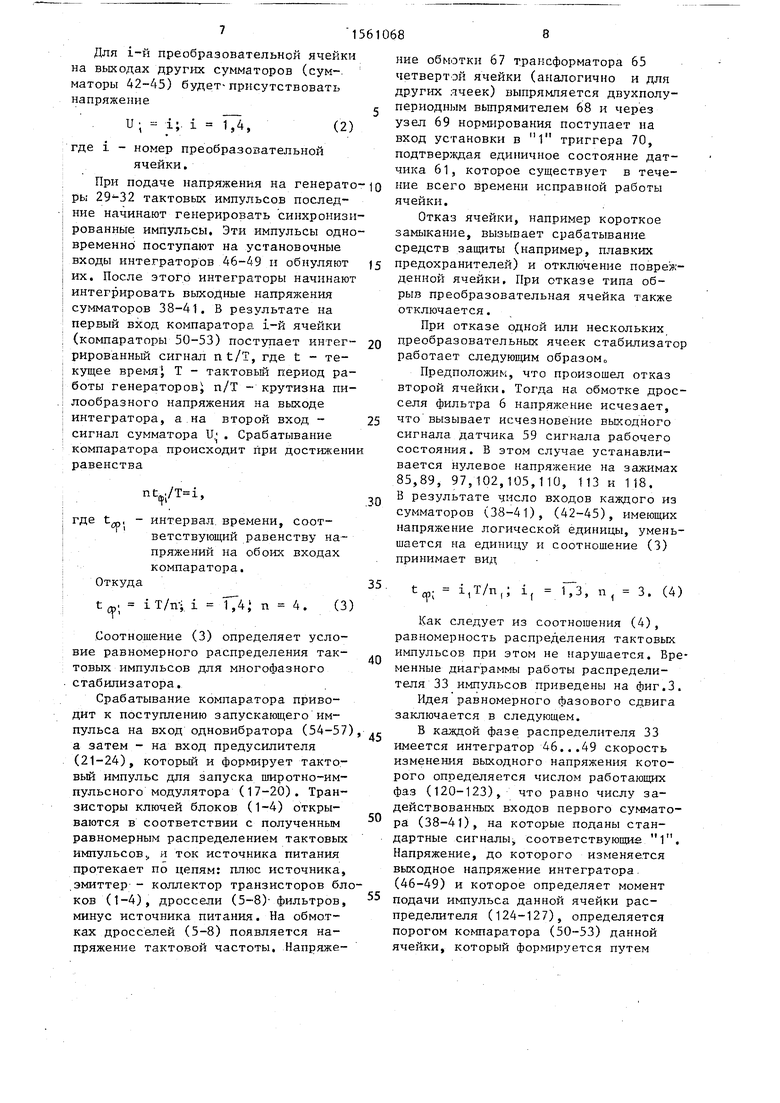

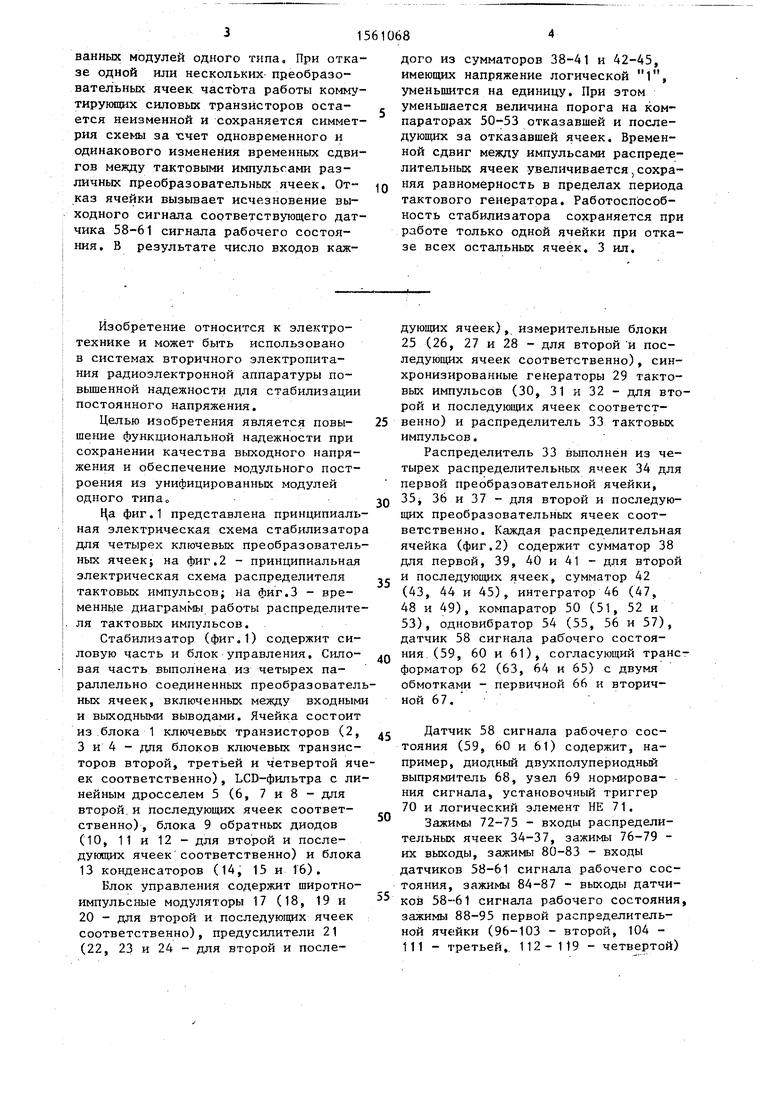

Ца фиг.1 представлена принципиальная электрическая схема стабилизатора для четырех ключевых преобразовательных ячеек; на фиг.2 - принципиальная электрическая схема распределителя тактовых импульсов; ria фиг.З - временные диаграммы работы распределителя тактовых импульсов.

Стабилизатор (фиг.1) содержит силовую часть и блок управления. Сило- вал часть выполнена из четырех параллельно соединенных преобразовательных ячеек, включенных между входными и выходными выводами. Ячейка состоит из блока 1 ключевых транзисторов (2, 3 и 4 - для блоков ключевых транзисторов второй, третьей и четвертой ячеек соответственно), LCD-фильтра с линейным дросселем 5 (6, 7 и 8 - для

второй и последующих ячеек соответ

ственно), блока 9 обратных диодов (10, 11 и 12 - для второй и последующих ячеек соответственно) и блока 13 конденсаторов (14, 15 и 16).

Блок управления содержит широтно- импульсные модуляторы 17 (18, 19 и 20 - для второй и последующих ячеек соответственно), предусилители 21 (22, 23 и 24 - для второй и после

,

п 5

0

5

дующих ячеек), измерительные блоки 25 (26, 27 и 28 - для второй и последующих ячеек соответственно), синхронизированные генераторы 29 тактовых импульсов (30, 31 и 32 - для второй и последующих ячеек соответственно) и распределитель 33 тактовых импульсов.

Распределитель 33 выполнен из четырех распределительных я«еек 34 для первой преобразовательной ячейки, 35, 36 и 37 - для второй и последующих преобразовательных ячеек соответственно. Каждая распределительная ячейка (фиг.2) содержит сумматор 38 для первой, 39, 40 и 41 - для второй и последующих ячеек, сумматор 42 (43, 44 и 45), интегратор 46 (47, 48 и 49), компаратор 50 (51, 52 и 53), одновибратор 54 (55, 56 и 57), датчик 58 сигнала рабочего состояния (59, 60 и 61), согласующий трансформатор 62 (63, 64 и 65) с двумя обмотками - первичной 66 и вторичной 6 7.

Датчик 58 сигнала рабочего состояния (59, 60 и 61) содержит, например, диодный двухполупериодный выпрямитель 68, узел 69 нормирования сигналаs установочный триггер 70 и логический элемент НЕ 71.

Зажимы 72-75 - входы распределительных ячеек 34-37, зажимы 76-79 - их выходы, зажимы 80-83 - входы датчиков 58-61 сигнала рабочего состояния, зажимы 84-87 - выходы датчиков 58-61 сигнала рабочего состояния, зажимы 88-95 первой распределительной ячейки (96-103 - второй, 104 - 111 - третьей, 112-119 - четвертой)

5

являются входами сумматоров 38-41 и 42-45.

К зажимам 72-75 подключены синхронизированные генераторы 29-32 тактовых импульсов соответственно, а к зажимам 76-79 - входы предусилите- лей 21-24.

Зажим 84 (выход датчика 58 сигнала рабочего состояния ячейки 34) соединен с зажимами 88 (вход сумматора 38 ячейки 34), 95 (вход сумматора

42ячейки 34), 96 (вход сумматора 39 ячейки 35), 103 (вход сумматора 43 ячейки 35), 104 (вход сумматора 40 ячейки 36), 111 (вход сумматора 44 ячейки 36), 112 (вход сумматора 41 ячейки 37) и 119 (вход сумматора 45 ячейки 37).

Зажим 85 (выход датчика 59 сигнала рабочего состояния ячейки 35) соединен с зажимами 89 (вход сумматора

38ячейки 34), 97 (вход сумматора

39ячейки 35), 102 ( вход сумматора

43ячейки 35), 105 (вход сумматора

40ячейки 36), 110 (вход сумматора

44ячейки 36), 113 (вход сумматора

41ячейки 37) и 118 (вход сумматора

45ячейки 37).

Зажим 86 (выход датчика 60 сигнала рабочего состояния ячейки 36) соединен с зажимами 90 (вход сумматора

38ячейки 34), 98 (вход сумматора

39ячейки 35), 106 (вход сумматора

40ячейки 36), 109 (вход сумматора

44ячейки 36), 114 (вход сумматора

41ячейки 37) и 117 (вход сумматора

45ячейки 37).

Зажим 87 (выход датчика 61 сигнала рабочего состояния ячейки 37) соединен с зажимами 91 (вход сумматора 38 ячейки 34), 99 (вход сумматора 39 ячейки 35), 107 (вход сумматора 40 ячейки 36), 115 (вход сумматора 41 ячейки 37) и 116 (вход сумматора 45 ячейки 37).

Зажим 72 (73-75) соединен с установочным входом интегратора 46 (47- 49)„ Вход интегратора 46 (47-49) соединен с выходом сумматора 38 (39-41), а выход интегратора 46 подключен к первому входу компаратора 50 (51-53). Второй вход компаратора подключен к выходу сумматора 42 (43-45)„ Выход компаратора 50 (51-53) подключен к входу одновибратора 54 (55-57). Выход одновибратора 54 (55-57) подключен к зажиму 76 (77-79)0 Зажимы 80- 83 согласующих трансформаторов под10

filui)8

ключены к обмоткам дросселей 5-8 соответственно. К вторичным обмоткам трансформатора 62 (63-65) подключен датчик 58 (59-Ы) сигнала рабочего

состояния. Выход 87 датчика 61 сигнала рабочего состояния четвертой ячейки соединен с выходом установочного триггера 70. Один вход установочного триггера 70 подключен к выходу узла 69 нормирования сигналов, другой вход - к выходу логического элемента НЕ 71, который подключен к выходу узла 69 нормирования сигнала.

.,- Вход узла 69 нормирования сигнала

подключен к выходу двухполупериодного выпрямителя 68, вход которого подключен к вторичной обмотке согласующего трансформатора 67. Генераторы 29-32

20 работают синхронно, причем отказ любого из них не влияет на синхронность работы оставшихся генераторов. Работа стабилизатора рассматривается в режиме запуска и установившем25 ся режима с исправными ячейками, и в режиме работы при отказе одной или нескольких преобразовательных ячеек0 В режиме запуска стабилизатор работает следующим образом.

30 I

В исходном состоянии ключевые

транзисторы блоков 1-4 закрыты, ток через дроссели 5-8 не протекает, напряжение на них равно нулю. Напряжение на выводах датчиков 58-61 сигнала 35 рабочего состояния равно напряжению логического нуля. Установочные триггеры датчиков (триггер 70 для четвертой распределительной ячейки) через

установочные входы при пуске стаби40

лизатора переводятся в состояние,

когда на их выходах устанавливаются напряжения логической единицы. Эти напряжения устанавливаются на четырех входах сумматора 45, на трех входах сумматора 44, на двух входах сумматора 43 и на одном входе сумматора 42.Напряжение, равное нулю, будет присутствовать на одном входе сумматора 44, на двух входах сумматора 43 и на трех входах сумматора 42. Таким образом, на выходах сумматоров 38-41 будет присутствовать напряжение

50

55

,

где п - число преобразовательных ячеек (в примере ).

Для i-й преобразовательной ячейки на выходах других сумматоров (сумматоры 42-45) будет-присутствовать напряжение

U; i; 1

М,

(2)

где г - номер преобразовательной

ячейки.

При подаче напряжения на генерато ю ры 29-32 тактовых импульсов последние начинают генерировать синхронизированные импульсы. Эти импульсы одновременно поступают на установочные входы интеграторов 46-49 н обнуляют 15 их. После этого интеграторы начинают интегрировать выходные напряжения сумматоров 38-41. В результате на первый вход компаратора i-й ячейки (компараторы 50-53) поступает интег- 20 рированный сигнал nt/T, где t - текущее времяJ Т - тактовый период работы генераторов п/Т - крутизна пилообразного напряжения на выходе интегратора, а на второй вход - 25 сигнал сумматора U- . Срабатывание компаратора происходит при достижении равенства

,

где t, - интервал времени, соответствующий равенству напряжений на обоих входах компаратора. Откуда

tq,. iT/n-j i 774J n 4. (3)

Соотношение (3) определяет условие равномерного распределения тактовых импульсов для многофазного стабилизатора.

Срабатывание компаратора приводит к поступлению запускающего импульса на вход одновибратора (54-57 а затем - на вход предусилителя (21-24), который и формирует тактовый импульс для запуска широтно-им- пульсного модулятора (17-20), Транзисторы ключей блоков (1-4) открываются в соответствии с полученным равномерным распределением тактовых импульсов,, и ток источника питания протекает по цепям: плюс источника, эмиттер - коллектор транзисторов блков (1-4), дроссели (5-8) фильтров, минус источника питания. На обмотках дросселей (5-8) появляется напряжение тактовой частоты. Напряже

5 0 5

0

0

5

5

0

ние обмотки 67 трансформатора 65 четвертэй ячейки (аналогично и для других лчеек) выпрямляется двухполу- периодным выпрямителем 68 и через узел 69 нормирования поступает на вход установки в 1 триггера 70, подтверждая единичное состояние датчика 61, которое существует в течение всего времени исправной работы ячейки.

Отказ ячейки, например короткое замыкание, вызывает срабатывание средств защиты (например, плавких предохранителей) и отключение поврежденной ячейки. При отказе типа обрыв преобразовательная ячейка также отключается.

При отказе одной или нескольких преобразовательных ячеек стабилизатор работает следующим образом

Предположим, что произошел отказ второй ячейки. Тогда на обмотке дросселя фильтра 6 напряжение исчезает, что вызывает исчезновение выходного сигнала датчика 59 сигнала рабочего состояния. В этом случае устанавливается нулевое напряжение на зажимах 85,89, 97,102,105,110, 113 и 118. В результате число входов каждого из сумматоров О8-41), (42-45), имеющих напряжение логической единицы, уменьшается на единицу и соотношение (3) принимает вид

ty. 1,1/11,; i, ГГз, n, з. (4)

Как следует из соотношения (4), равномерность распределения тактовых импульсов при этом не нарушается. Временные диаграммы работы распределителя 33 импульсов приведены на фиг.З.

Идея равномерного фазового сдвига заключается в следующем.

В каждой фазе распределителя 33 имеется интегратор 46...49 скорость изменения выходного напряжения которого определяется числом работающих фаз (120-123), что равно числу задействованных входов первого сумматора (38-41), на которые поданы стандартные сигналы, соответствующие 1, Напряжение, до которого изменяется выходное напряжение интегратора (46-49) и которое определяет момент подачи импульса данной ячейки распределителя (124-127), определяется порогом компаратора (50-53) данной ячейки, который формируется путем

подачи на вход второго сумматора (42-45) этих же стандартных сигналов И1, но на вход сумматора 38 первой ячейки 34 подается 1 на один вход, на все другие входы - О, у второй ячейки 35 1 подается на два входа, на другие - О и у третьей ячейки 36 1 подается на три входа, на другие - О и т.д. Таким образом, выходное напряжение первого интегратора 46 достигнет порогового значения первой ячейки 34 в два раза быстрее,чем второй 35, так как скорость изменения выходного напряжения интеграторов 46 и 47 одинакова, а пороги отличаются в два раза (120-123)

Аналогичные рассуждения можно привести для всех последующих ячеек по сравнению с первой. Порог i-й ячейки в i раз больше порога первой. Следовательно, выходной импульс 126 третьей ячейки 36 появится в три раза позднее относительно тактового, чем первой ячейки 34(124). Тактовый импульс обнуляет (устанавливает в исходное состояние) все интеграторы (4b-49j и начинается новый цикл распределения.

При отказе ячейки, например второй, обнуляется 1 с датчика 59 этой ячейки на входе первого сумматора (38-41). Таким образом, уменьшается скорость интегрирования интегратора (46-49), что позволяет разделить тот же период, задаваемый тактовым генератором (29-32) на п-1 интервал. При этом также изменяется величина порога (121-123) на компараторах (51...53) второй ячейки и последующих за отказавшей, так как при обнулении 1 отказавшей ячейки уменьшается число входов с 1 вторых сумматоров (43...45) в последующих ячейках. Таким образом, временно сдвиг между импульсами распределителя 33 увеличивается (124-127), сохраняя равномерность в пределах периода тактового генератора.

56)068

где

10

п 15

30

40

k 10

максимальное число преобразовательных ячеек многофазного стабилизатора,предусмотренное конструкцией распределителя тактовых импульсовj

число отказавших преобразовательных ячеек; - временной сдвиг тактовых импульсов i-й работающей преобразовательной ячейки внутри тактового периода Т.

Из соотношения (5) вытекает вывод о возможности включения преобразовательных ячеек в состав многофазного стабилизатора без нарушения условия равномерного распределения тактовых импульсов при отказе некоторых преобразовательных ячеек.

Изобретение позволяет повысить функциональную надежность, технологичность, безотказность и ремонтопригодность. Работоспособность стабилизатора сохраняется при работе только одной ячейки в случае отказа всех остальных ячеек. Децентрализация блока управления позволяет выполнить весь стабилизатор по модульному принципу и проектирование стабилизатора можно осуществлять на основе сборки из унифицированных преобразовательных модулей одного типа. При этом повышение безотказ- 35 ности устройства достигается введением функционально-избыточных узлов. Улучшение ремонтопригодности достигается возможностью ремонта стабилизатора простой заменой неисправного модуля на исправный при работающем стабилизаторе.

20

25

Формула изобретения

Многофазный импульсный стабилизатор постоянного напряжения, содержащий п параллельно соединенных кпюче- вых преобразовательных ячеек, включенных между входными и выходными

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386977A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386976A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Устройство для управления многофазным импульсным регулятором | 1981 |

|

SU957411A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Стабилизирующий преобразователь постоянного напряжения | 1986 |

|

SU1415367A1 |

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания радиоэлектронной аппаратуры повышенной надежности для стабилизации постоянного напряжения. Цель изобретения - повышение функциональной надежности при сохранении качества выходного напряжения и обеспечение модульного построения из унифицированных модулей одного типа. При отказе одной или нескольких преобразовательных ячеек частота работы коммутирующих силовых транзисторов остается неизменной и сохраняется симметрия схемы за счет одновременного и одинакового изменения временных сдвигов между тактовыми импульсами различных преобразовательных ячеек. Отказ ячейки вызывает исчезновение выходного сигнала соответствующего датчика 58-61 сигнала рабочего состояния. В результате число входов каждого из сумматоров 38-41 и 42-45, имеющих напряжение логической "1", уменьшится на единицу. При этом уменьшается величина порога на компараторах 50-53 отказавшей и последующих за отказавшей ячеек. Временной сдвиг между импульсами распределительных ячеек увеличивается, сохраняя равномерность в пределах периода тактового генератора. Работоспособность стабилизатора сохраняется при работе только одной ячейки при отказе всех остальных ячеек. 3 ил.

выводами, каждая из которых содержит

Описанный принцип работы схемы мо50 блок ключевых транзисторов и LCD- фильтр, и блок управления, состоящий из широтно-импульсных модуляторов, выходами подключенных к управляющим уходам соответствующих преобразовательных ячеек, а входами - к выходам предусилителей, первые входы которых подключены к выходам измерительных блоков, входы которых соединены с

жет быть распространен напячеек многофазного стабилизатора постоянного напряжения. При этом распределение тактовых импульсов будет определяться соотношением

55

iKT/nK; iK i,(n-k);

пк п - k,

(5)

мо(5)

выходными выводами генераторов тактовых импульсов по числу преобразовательных ячеек, подключенных к входам распределителя тактовых импульсов, выполненного в виде п распределительных ячеек, входы которых образуют входы распределителя тактовых импульсов, каждая из распределительных ячеек включает датчик сигнала рабочего состояния, вход которого подключен к дросселю LCD-фильтра соответствующей преобразовательной ячейки непосредственно или через разделительный трансформатор, выходы распределителя тактовых импульсов образованные выходами распределительных ячеек, подключены к вторым входам соответствующих предусилителей, отличающийся тем, что, с целью повышения функциональной надежности при сохранении качества выходного напряжения и обеспечения модульного построения из унифицированных модулей одного типа, в каждую из

распределительных ячеек введены два п входных сумматора, интегратор, компаратор и одновибратор, причем выходы всех датчиков сигнала рабочего сое- | тояния подключены к входам первого сумматора каждой распределительной ячейки, выход которого подключен к входу интегратора, выходом соединенного с первым входом компаратора,вы- лод которого подключен к входу одно- вибратора, выходом подключенного к выходу распределительной ячейки, i входов второго сумматора i-й распределительной ячейки подключены к выходам датчиков сигнала рабочего состояния всех предыдущих и i-й ячеек, остальные n-i входов второго сумматора подключены к линии нулевого потенциала, при этом выход второго сумматора каждой распределительной ячейки подключен к второму входу компаратора, вход начальной установки интегратора подключен к входу

распределительной ячейки.

Фиг.З

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-04-30—Публикация

1988-01-05—Подача