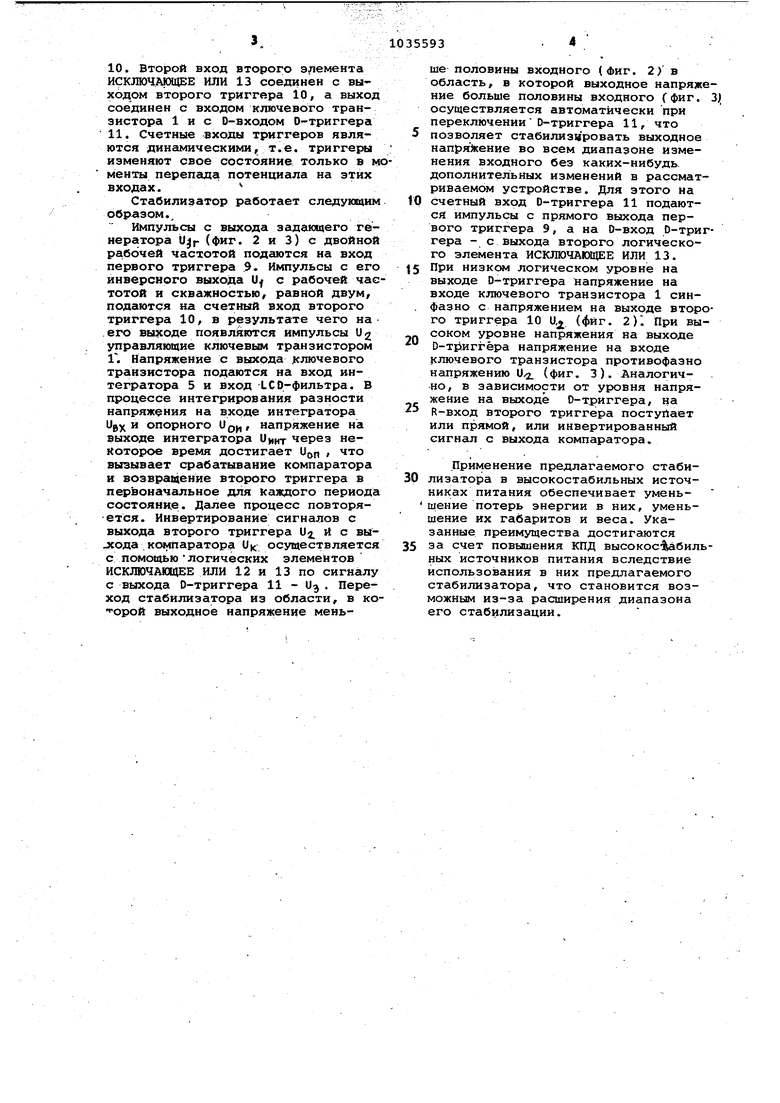

Изобретение относится к электротехнике, а именно к промьшшенности средств связи, и может быть исполь зовано при построении универсальны высокостабильных вторичных источни ков питания радиоэлектронной аппаратуры, например телевизионной. По основному авт. св. 935929 известен параметрический импульсный стабилизатор постоянного напряжения, содержащий последователь но соединенные и включенные в силовую шину ключевой транзистор и дроссель LCD-фильтра, конденсатор которого соединен с выводами для п ключения к нагрузке, интегратор, один вход которого соединен с обще точкой ключевого транзистора и дро селя LCD-фильтра, другой вход - с источником опорного напряжения, компаратор, задающий генератор, два триггера и логический элемент. Один вход компаратора соединен с источником опорного напряжения, др гой вход - с выходом, интегратора. Выход здцающего генерат.ора соединен с входом первого триггера, вых которого соединен с входом второго триггера и одним из входов логичес го элемента. Другой вход логического элемента соединен с выходом в рого триггера, второй вход которого соединен с выходом компаратора. Выход логического элемента подключ к входу ключевого транзистора flj. Недостатком этого стабилизатора является узкий диапазон стабилизации выходного напряжения. Это обус ловлено тем, что для устойчивой работы стабилизатора длительность времени от начала каждого периода до гломента срабатывания компаратор ограничена на уровне половины периода. Поэтому стабилизатор может работать или только при выходном напряжении меньше, чем половин входного, или, соответственно, бол ше, Цель изобретения - увеличение функциональных возможностей путем расширения диапазона стабилизации. Поставленная иель достигается тем, что в параметрическом импульсном стабилизаторе постоянного напряжения по авт. св. 935929, содержащем последовательно соединенные и включенные в силовую шину ключевой трайзистор и дроссель LCD-фильтра, конденсатор которого соединен с выводами для подключения к нагрузке, интегратор, один вход которого соединен с общей точкой ключевого транзистора и дросселя LCD-фильтра, другой вход с источником опорного напряжения, компаратор, один вход которого сое динен с источником опорного напряжения , а другой вход - с выходом интегратора, последовательно соединенные задающий генератор и первый триггер, второй триггер и логический элемент, причем выход первого триггера соединен со счетным входом второго триггера и одним входом логического элемента, другой вход логического элемента соединен с-выходом второго триггера, второй вход которого соединен с выходом компара тора7 э выход логического элемента подключен к входу ключевого транзистора, указанная связь выхода первого триггера с одним входом логического элемента, в качестве которого используется первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выполнена через D-триггвр, счетный вход которого подключен к неинвертирующему выходу первого триггера, а связь второго входа второго Триггера с выходом компаратора выполнена через второй логический элемент ИСКЛЮЧАЩЕЕ ИЛИ, причем другой вход вт ррого логического элемента ИСКЛЮЧАЮШЕЕ ИЛИ Яодсоединен к выходу D-триггера, а выход подключен к R-входу второго триггера, вход ключевого транзистора подсоединен к D-входу D-триггера. На фиг. 1 изображена структурная схема параметрического импульсного стабилизатора постоянного напряжения/ на фиг. 2 - диаграм1 ы при выходном напряжении стабилизатора меньше половины входного; на фиг.Здиаграммы напряжений при выходном напряжении больше половины входного напряжения. Параметрический импульсный стабилизатор постоянного напряжения {фиг. 1} содержит последовательно t соединенные и включенные в силовую шину ключевой транзистор 1 и сглаживаюьшй LCD-фильтр, состоящий из диода 2, дросселя 3 и соединенного с выводами для подключения к нагрузке конденсатора 4. Общая точка ключевого транзистора 1 и дросселя 3 соединена с инверсным входом интегратора 5, выход которого соединен с одним из входов компаратора 6. Другой вход компаратора б соедиНен с прямым входом интегратора 5 И источником опорного напряжения 7. Задакяций генератор 8, определяющий рабочую частоту стабилизатора, соединен со счетным входом первого триггера 9, инверсный выход которого подключен к счетному входу второго триггера 10. Прямой выход первого триггера 9 соединен со счетным входом D-триггера 11, управляющего логическими элементами ИСКЛЮЧАЩЕЕ ИЛИ 12 и 13. Выход D-триггера 11 подключен к одному из входов этих элементов . Второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 соединен с выходом компаратора 6, а выход подключен к R-входу второго триггера

10.Второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 соединен с выходом второго триггера 10, а выход соединен с входом ключевого транзистора 1 и с О-входом 0-триггера

11.Счетные входы триггеров являются динамическими, т.е. триггеры изменяют свое состояние только в мменты перепада потенциала на этих входах.

Стабилизатор работает следующим образом..

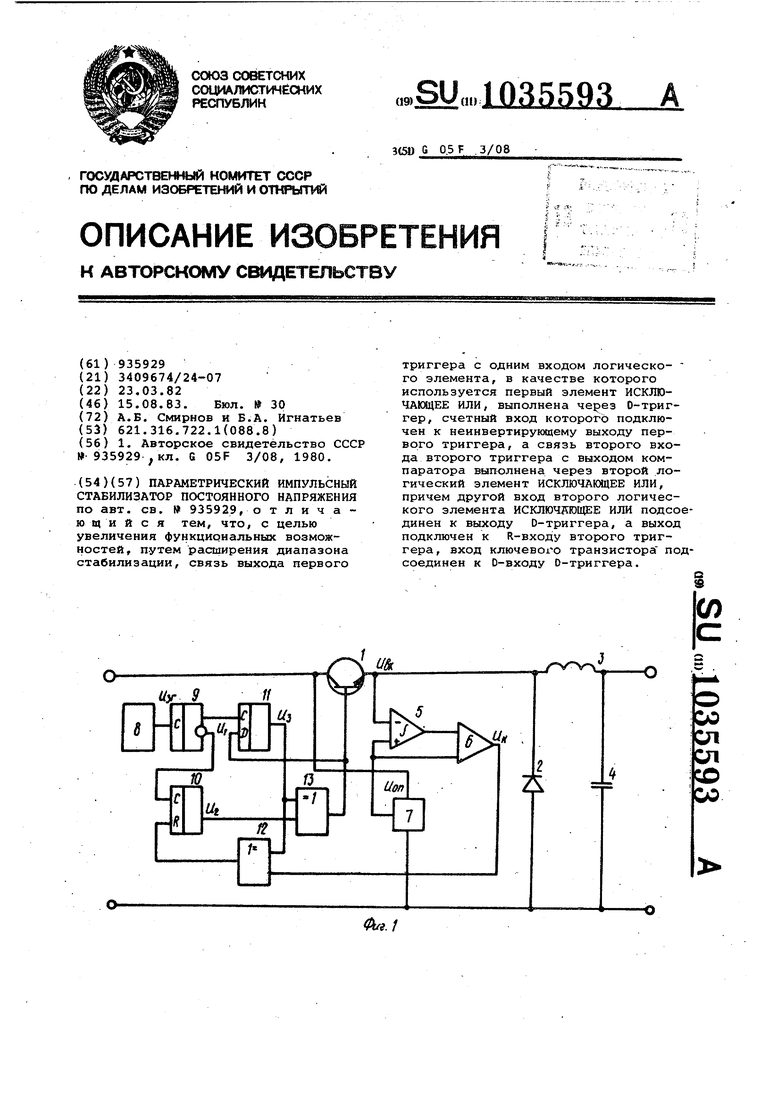

Импульсы с выхода задающего генератора U|r (фиг. 2 и 3) с двойной рабочей частотой подаются на вход первого триггера 9. Импульсы с его инверсного выхода U с рабочей частотой и скважностью, равной двум/ подаются на счетный вход второго триггера 10, в результате чего на его выходе появляются импульсы Ug управляющие ключевым транзистором 1. Напряжение с выхода ключевого транзистора подаются на вход интегратора 5 и вход LCD-фильтра. В процессе интегрирования разности напряжения на входе интегратора Ug)( и опорного UQ, напряжение на выходе интегратора UHHT через некоторое время достигает / что вызывает срабатывание компаратора и возвращение второго триггера в первоначальное для каждого периода состояние. Далее процесс повторяется. Инвертирование сигналов с выхода второго триггера U. и с вывода компаратора Уц; осуществляется с помощьюлогических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и 13 по сигналу с выхода О-триггера 11 - U . Переход стабилизатора из области, в выходное напряжение меньше половины входного (Фиг. 2) в область, в которой выходное напряжение больше половины входного (фиг. 3J| осуществляется автоматически при переключенииD-триггера 11, что 5 позволяет стабилизировать выходное напря ение во всем диапазоне изменения входного без каких-нибудь дополнительных изменений в рассматриваемом устройстве. Для этого на

o счетный вход D-триггера 11 подаются импульсы с прямого выхода первого триггера 9, а на D-вход О-триггера - с выхода второго логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13.

5 При низком логическом уровне на выходе D-триггера напряжение на входе ключевого транзистора 1 син, фазно с напряжением на выходе второго триггера 10 U, (фИг. 2) При вы соком уровне напряжения на выходе D-TjiHrrepa напряжение на входе } лючевого транзистора противофазно напряжению U (фиг. 3). Аналогич-но, в зависимости от уровня напряжение на выходе О-триггера, на

5 R-вход второго триггера поступает или прямой, или инвертированный сигнал с выхода компаратора.

Применение предлагаемого стабилизатора в высокостабильных источниках питания обеспечивает уменьшение потерь энергии в них, уменьшение их габаритов и веса. Указанные преимущества достигаются 5 за счет повышения КПД высокос бильных источников питания вследствие использо вания в них предлагаемого стабилизатора, что становится возможным из-за расширения диапазона его стабилизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параметрический импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935929A1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1324016A2 |

| Импульсный параметрический стабилизатор постоянного напряжения | 1983 |

|

SU1141390A1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1984 |

|

SU1159006A1 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1559333A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Импульсный стабилизатор постоянного напряжения | 1984 |

|

SU1205134A1 |

| Ключевой стабилизатор постоянного напряжения | 1991 |

|

SU1815628A1 |

| Импульсный стабилизатор постоянного напряжения | 1984 |

|

SU1182499A1 |

| Стабилизирующий преобразователь постоянного напряжения | 1985 |

|

SU1285449A1 |

ПАРАМЕТРИЧЕСКИЙ ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ по авт. св. 935929, о т л и ч а ю щ и и с я тем, что, с целью увеличения функциональных возможностей, путем расширения диапазона стабилизации, связь выхода первого триггера с одним входом логического элемента, в качестве которого используется первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выполнена 0-триггер, счетный вход которого подключен к неинвертирующему выходу первого триггера, а связь второго входа второго триггера с выходом компаратора выполнена через второй .логический элемент ИСКЛЮЧАКВДЕЕ ИЛИ, причем другой вход второго логического элемента ИСКЛЮЧ ШЩЕЕ ИЛИ подсоединен к выходу D-триггера, а выход подключен к R-входу второго триггера, вход ключевого транзистора подсоединен к О-входу О-триггера. со ел сл х :о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935929A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-08-15—Публикация

1982-03-23—Подача