Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств в этих областях.

Известны дискретные синхронные устройства, содержащие блок элементов памяти и комбинационные цепи, реализующие функции выходсз и переключений. Недостатком этих устройств является отсутствие четкой-синхронизации срабатывания элементов, что в свою очередь повышает вероятность возникновения риска сбоя, для устранения которого требуется сложное распределение и учет задержек в критических точках асинхронных схем (1).

Известны синхронные дискретные устройства, в которых исключение риска сбоя за счет неравенства задержки распространения сигналов в логических цепях обеспечивается синхронизирующими сигналами (2).

Недостатком этих устройств является то, что сбои в блоке памяти полностью нарушают алгоритм функционирования.

Известно синхронное избыточно-кодированное дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, которое позволяет скорректировать часть сбоев (3).

По своей технической сущности и достигаемому положительному эффекту это устройство является наиболее близким к .предлагаемому. .

Недостатком известного устройства является то, что в его блоке памяти могут накапливаться сбои в интервалах между с и н х р о нши ру ю щ ййгйг сШШЖйТчТo if cf о ю очередь нарушает процесс восстановления информации восстанавливающим органом и снижает устойчивость к сбоям.

Целью изобретения является повышение устойчивости к сбоям. Поставленная цель достигается тем, что в синхронное дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, вход которого связан с выходом блока памяти, а выход --с одним из входов комбинационного блока, другой вход которого яп- ляется информационным входом устройства, а один из выходов - информационным выходом устройства, снабженного также тактоел

с

XI

00

о

4

со

00

ым входом, введены первый, второй и треий коммутаторы, блок инверторов, инверг ор, элемент задержки и три шины огических констант, каждая из которых подключена ко второму информационному ходу соответствующего коммутатора, выод восстанавливающего органа соединен акже с первым информационным входом первого коммутатора и с входом блока инверторов, выход которого подключен к первому информационному входу второго коммутатора, первый информационный вход третьего коммутатора подсоединен ко второму выходу комбинационного блока, выход - к информационному входу блока памяти, а управляющий вход третьего коммутатора является входом управления начальной установкой устройства, выходы первого и второго коммутаторов связаны соответственно с инверсным и с прямым установочными входами блока памяти, а управляющие входы первого и второго коммутаторов объединены и подключены через инвертор к тактовому входу устройства, соединенного также через элемент задержки с синхронизирующим входом блока памяти.

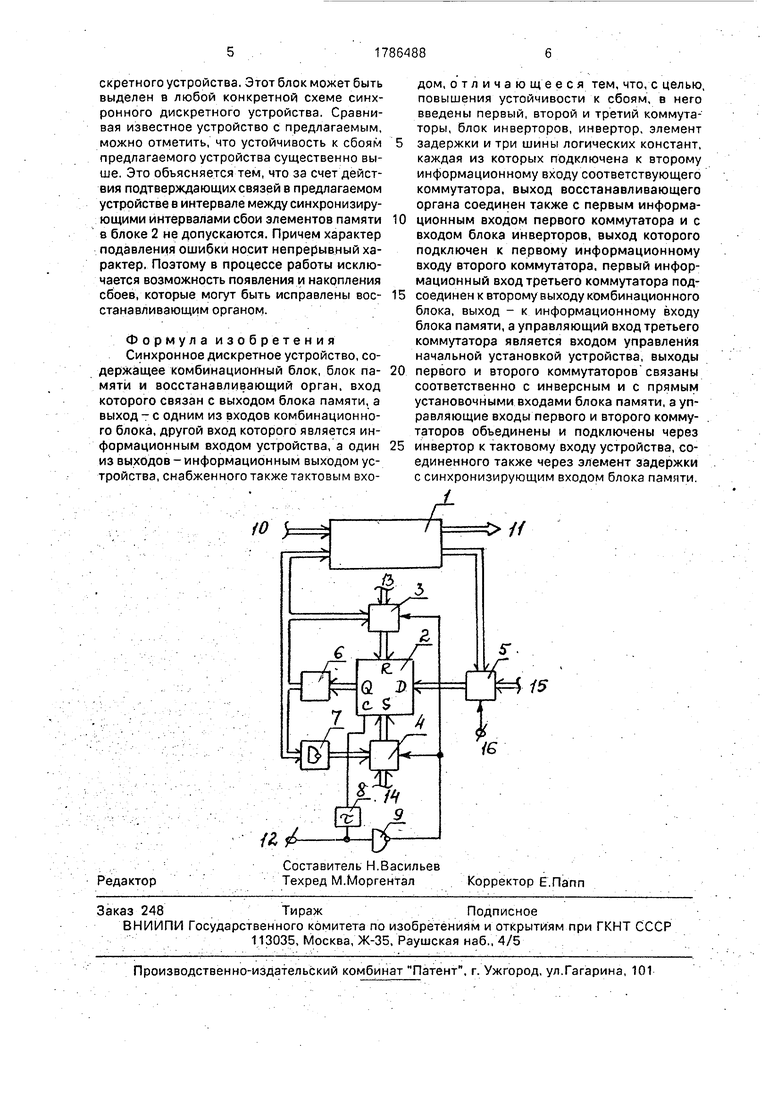

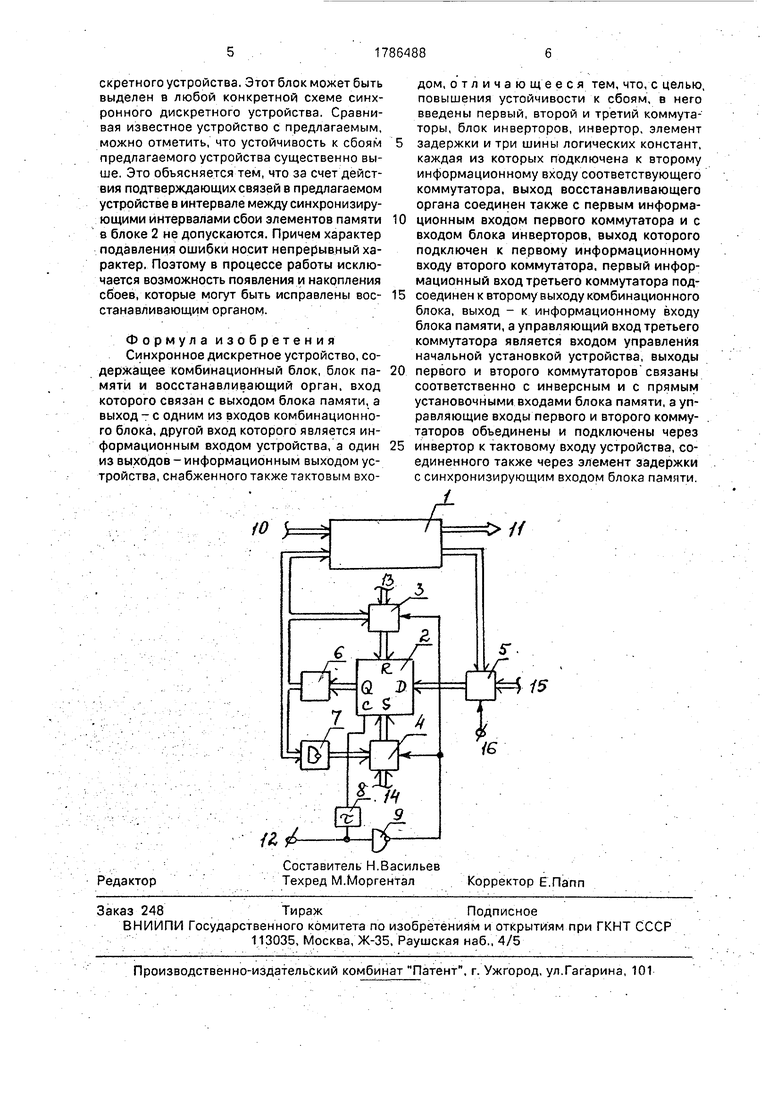

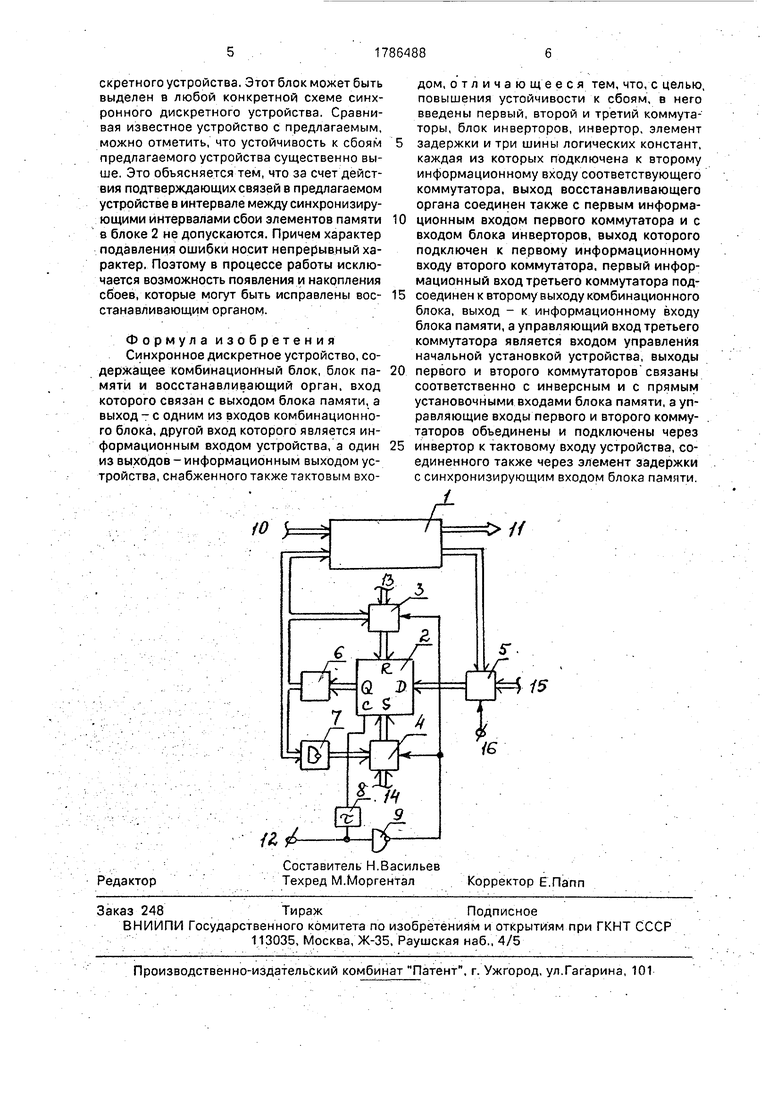

На чертеже представлена блок-схема синхронного дискретного устройства.

Устройство содержит комбинационный блок 1, блок 2 памяти, коммутаторы 3, 4 и 5, восстанавливающий орган 6, блок 7 инверторов, элементе задержки, инвертор9, вход 10, выход 11, тактовый вход 12, шины 13,14, 15 логических констант и установочный

ВХОД 16. ; ... . :- ; / . : .

Вход 10 соединен с входом блока 1, первый Выход которого сокединен с выходом 11. Второй выход блока 1 соединен с входом коммутатора 5, второй вход которого соединен с шиной 15, а управляющий вход - с входом 16. Выход коммутатора 5 соединен с информационным входом блока 2; выход которого через восстанавливаю-; щий орган 6 связан с вторым входом блока 1, входом коммутатора 3 и через блок 7 Инверторов- С входом коммутатора 4. Выходы коммутаторов 3, 4 соединены соответственно с входами установки в нулевые и единичные стостояния элементов памяти блока 2, памяти.

Шины 13, 14, 15 логических констант соединены с вторыми входами коммутаторов 3,4,5. , . .,... .. . . : . . ,

Тактовый вход 12 через элемент 8 задержки связйн с синхронизирующим входом блока 2 и через инвертор 9 - с управляющими входами коммутаторов 3,4. Установочный вход 16 соединен с управляющим входом коммутатора 5. Перед началом работы на вход 16 подается сигнал.

подключающий код на шине 15 к информационным входам блока 2. В этом случае тактовому сигналу на входе 12 код начальной установки вводится в разряды блока 2. В

процессе работы устройство синхронным способом производит преобразование кодов на входе 10 в выходные коды.|

При этом избыточная информация с в;ы- хода блока 2 подвергается операции восста0 новЛёнйяГ с помощью восстанавливающего органа 6 и через коммутаторы 3,4 воздей0т- вуют на установочные (асинхронные) входы элементов памяти блока 2. Это воздействие носит непрерывный характер и сохраняется

5 до следующего синхронизирующего сигнала.

С приходом следующего синхронизирующего сигнала сначала коммутаторы 3, 4 переключаются в режим коммутации сигйа0 лов с шин 13, 14, на которых установлены нулевые коды. Это соответствует отклю е- нию установочных воздействий от блока 2. Затем синхронизирующий сигнал поступает на блок 2, который воспринимает код с

5 выхода коммутатора 5.

Таким образом на асинхронных устайо- врчных входах блока 2 в интервалах между тактовыми сигналами формируются сИгНа- лы, подтверждающие состояния элементов

0. памяти. Эти сигналы, сформированные с (ю- мощью восстанавливающего органа, препятствует накоплению сбоев в блоке .2-k и тем самым повышают устойчивость к сббям синхронного устройства.

5 Блок 2 памяти представляет собой о|бъ- единение синхронных D-триггеров, имеющих общую шину синхронизации. Избыточность блока 2 заключается в использовании большего количества D-триггеров, чем это нерб0 ходимо для представления состояний

дискретного устройства. Выхрды 0-три(ге ров составляют выход блока 2. Устанофчные R и S-входы D-трйггеров составляют

первый и второй установочные входы блЬка

5 2. D-входы. D-входы D-триггеров образуют информационные входы блока 2. Коммутаторы 3,4,5 представляют собой мультипг ек- соры, осуществлйющие подключени г к своим выходам первого или второго инфор0 мацйонных входов в зависимости от управляющего сигнала.I

Восстанавливающий орган в случае,ёс- ли, например, используются троировайие блока 2, представляет собой объединение поразрядных мажоритарных элементов.

5

Блок 7 инверторов представляет собой набор поразрядных инверторов.

Комбинационный блок 1 является одноактной логической схемой, формирующей выходную и переключательную функцию дискретного устройства. Этот блок может быть выделен в любой конкретной схеме синхронного дискретного устройства. Сравнивая известное устройство с предлагаемым, можно отметить, что устойчивость к сбоям предлагаемого устройства существенно выше. Это объясняется тем, что за счет действия подтверждающих связей в предлагаемом устройстве в интервале между синхронизирующими интервалами сбои элементов памяти в блоке 2 не допускаются. Причем характер подавления ошибки носит непрерывный характер. Поэтому в процессе работы исключается возможность появления и накопления сбоев, которые могут быть исправлены вое- станавливающим органом.

Фор мула изобретения Синхронное дискретное устройство, содержащее комбинационный блок, блок па- мятй и восстанавливающий орган, вход которого связан с выходом блока памяти, а выход-с одним из входов комбинационного блока, другой вход которого является информационным входом устройства, а один из выходов -информационным выходом устройства, снабженного также тактовым входом, отличающееся тем, что, с целью, повышения устойчивости к сбоям, в него введены первый, второй и третий коммутаторы, блок инверторов, инвертор, элемент задержки и три шины логических констант, каждая из которых подключена к второму информационному входу соответствующего коммутатора, выход восстанавливающего органа соединен также с первым информационным входом первого коммутатора и с входом блока инверторов, выход которого подключен к первому информационному входу второго коммутатора, первый информационный вход третьего коммутатора подсоединен к второму выходу комбинационного блока, выход - к информационному входу блока памяти, а управляющий вход третьего коммутатора является входом управления начальной установкой устройства, выходы первого и второго коммутаторов связаны соответственно с инверсным и с прямым установочными входами блока памяти, а управляющие входы первого и второго коммутаторов объединены и подключены через инвертор к тактовому входу устройства, соединенного также через элемент задержки с синхронизирующим входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное устройство | 1987 |

|

SU1786487A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| Устройство для многоканальной магнитной записи и воспроизведения последовательности импульсов | 1987 |

|

SU1483482A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение устойчивости к сбоям - достигается тем, что а синхронное дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, введены три коммутатора, блок инверторов, инвертор, элемент задержки и три шины логических констант. 1 ил.

Авторы

Даты

1993-01-07—Публикация

1987-04-06—Подача