(54) А НА ЛОГО-, ДИСКРЕТНЫЙ ПРЕОБРАЮВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-дискретный преобразователь | 1977 |

|

SU677074A1 |

| Аналого-дискретный преобразователь | 1978 |

|

SU782135A1 |

| Аналого-дискретный преобразователь | 1979 |

|

SU1094144A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Устройство дискретной автоподстройки частоты | 1989 |

|

SU1688408A1 |

| Устройство для выделения и анализа R-зубцов электрокардиосигнала | 1986 |

|

SU1364298A1 |

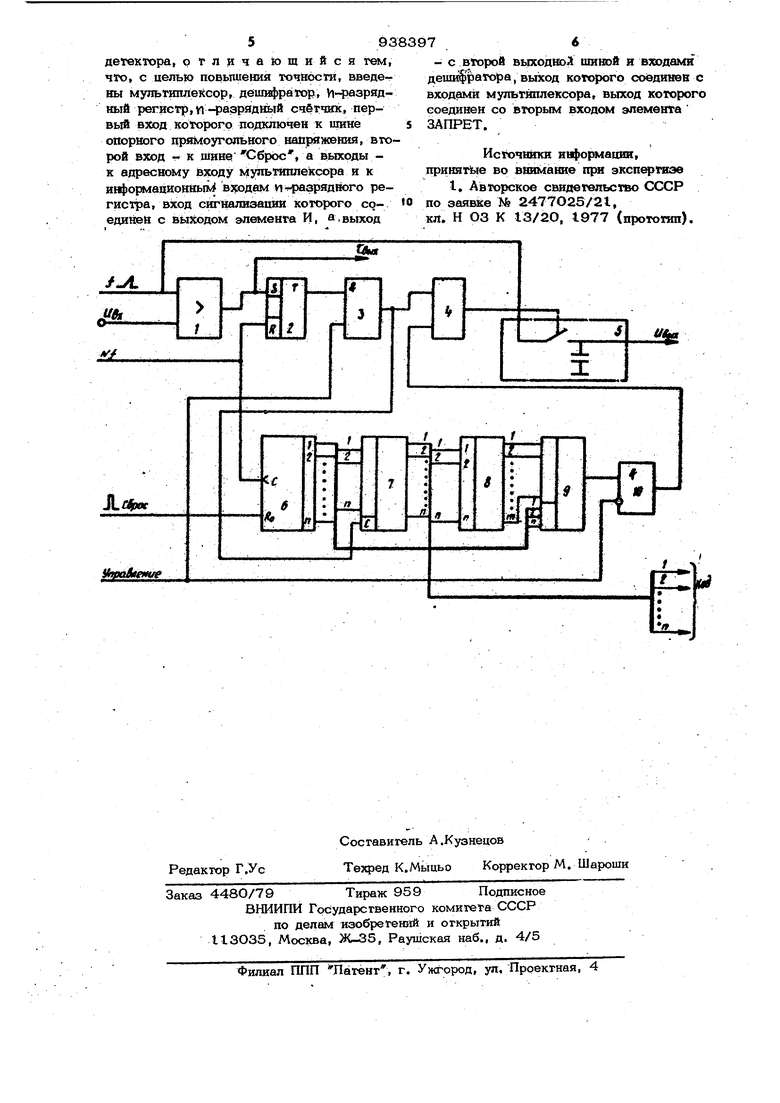

Изобрегеше огносигся к авгоматике и вычислительной технике и испопьэуегся в системах автоматического контроля и распознавания образцов. Известен аналого-дискретныЙСпреобразователь, включающий в себя оптроншакй многоустойчивый элемент, элемент ИЛИ, компаратс э, триггер и элемент ЗАПРЕТ Недостатком известного устройства является низкая точность преобразования Цель изобретения - повышение точнос ти устройства. Поставленная цель достигается тем, что в известный аналого-дискретный преобразователь, содержащий компаратор, пёрвь1й вход которого соединен с входной шиной, второй вход - с шиной опорного пилообразного напряжения и первым входом пикового детектора, а выход - с первой выходной шиной и первым входом триггера, второй вход которого соединен с шиной опорного прямоугольного напряжения, а выход - с первым входом элемента И, второй вход которого соединен с шиной сигнала управления и первым входом элемента ЗАПРЕТ, а выход - с первым входом элемента ИЛИ, второй вход KoTopcwo соединен с выходом элемента ЗАПРЕТ, а выход со вторым входом пикового детектора, введены мультиплексор, дешифратор,У -разрядный регистр, У -разрядный счётчик, первый вход которого подключен к шине опорного прямоугольного напряжения, второй вход - к шине Сброс, а выходы -к адресному входу мультиплексора и к информационным входам ii-разрядного регистра, вход сигнаш1зации которого соединен с выходом элемента И, а выход -с второй выходной шиной и входами дешифратора, выход которого соединен с входами Мультиплексора, выход которого соединен с вторым входом элемента ЗАПРЕТ. На чертеже представлена структурная схема аналого-дискретного преобразователя.

Преобразовагель вк,:-;:очаег в себя компаратор I, триггер 2, эпеменг ИЗ, элеменг ИЛИ 4, пиковьгй детектор 5, ц-разрядный счётчик 6, и-разрядный регистр 7, дешифратор 8, мультиплексор 9, элемент ЗАПРЕТ 1О.

Аналого дискретный преобразователь работает следующим образом.

Первоначально, импульсом сброса, в момент качала поступления пилообразного напряжения и-разрядный счётчик 6 усганавливается в начальное состояние. Посл на первый вход компаратора 1й на первый вход пикового детектора 5 подается опорное пилообразное напряжение частоты f, на вход установки в нуль триггера 2 и на счётный вход счётчика 6 подается опорное прямоугольное напряжение частоты Ы , а на второй вход компаратора - вход Ной сигнал, при

этом сигнал управления, который подается на первой вход элемента И 3 и на запрещакяций вход элемента ЗАПРЕТ 1О определяет режим работы аналого-дискретного преобразователя запоминание И1и})ормации или слежегше. При равенстве входного напряжения Ug с пилообразным напряжением частоты , на компараторе I формируется импульс, устанавливающий триггер 2 в единичное состояние. Триггер 2 находится в.этом состоянии до момента прихода переднего фронта ближайшего импульса опорного прямоугольного напряжения, который перебросит его в нулевое состояние, в рёзупьта те чего сфорж ируется импульс на выходе триггера 2. При наличии сигнала управления на слежение информации импульс с выхода триггера 2 проходит через элемент ИЗ, первый вход элемента ИЛИ 4 и на второй вход пикового детектора 5, При этом на выходе пикового детектора 5 появится напряжение равное текущему значению пилообразного напряжения. Одновременно импульсы частоты N f поступают на счётный вход счётчика 6,

Пбсле сформирования сигнала на выходе элемента И 3 состояние счётчика

6переписывается в yi-разрядтаШ регистр

7и на выходе Vi-разрядного регистра формируется код, соответствующий величине входного сигнала.

Сигналы с выхода у -разрядного ре-. гистра 7 поступают на дешифратор 8, в результате нн одном изуи-выходов дешифратора 8, соответствующего комбинации на входе, появится сигнал. Выходы

дешифратора 8 соединены со входами . мультиплексора 9. Адресные входы мультиплексора 9 опрашиваются сигналами с выхода у -разрядного счётчика 6. При совпадении кодов на адресных входах мудьтиплексора 9 и выходах регистра 7 на выходе мультиплексора 9 появится сигнал, которьгй повторяется периодически один раз за время существования пилообразного напряжения и соответствует моменту сравнения на компараторе входного сигнала с опорным, при этом сигнал с выхода мультиплексора 9 не проходит через элемент ЗАПРЕТ Ю и не поступит на элемент ИЛИ 4.

В режиме слежения вьшолняется следящее преобразование входной электрической величины постоянного напряжения во временной сдвиг С и цифровой код.

В отличие от режима слежения, в режиме запоминания сигнал с мультиплексора 9 через элемент Ю и 4 поступит на второй вход пикового детектора 5, на его выходе появится напряжение, равное значению пилообразного напряжения в момент поступления команды на аапоминанке, независимо от величины входного электрического сигнала. Кроме того, сигнал с выхода элемента И 3 прекращает поступать на вход синхронизации у1-разрядного регистра 7 и код, установленный ррнее в режиме слежения запоминается. В режиме запоминания запоминается величина входного аналогового сигнала, производится дискретное преобразоваше входной аналоговой величины в аналоговое значение выходного напряжения 1),.

..оЫ-л

Временной сдвиг и код.

Формула изобретения

А налого-дискретный преобразователь, содержащий компаратор, первый вход которого соединен с входной щиной, второй вход - с шиной опорного пилообразного напряжения и первым входом пикового детектора, а выход - с первой выходной шиной и первым ВХОДОМ; триггера, второй вход которого соединен с шиной опорного прямоугольного напряжения, а выход - с первым входом элемента И, второй вход которого соединен с шиной сигнала управления и первым входом элемента ЗАПРЕТ, а вьрсод - с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ЗАПРЕТ, а выход - со вторым входом пикового детектора, о тли чающийся тем, что, с целью повышешш точности, введены мупьтщшетссор, дёши)ратор;, Vi-раэрядный регистр, VI -разрядный счётчик, первый вход которого подключен к игане оПорвого прямоугольного наоряжания, вто рой вход - к шине Сброс, а выходы к адресному взсоду мультиплексора и к информационны входам И азрядвого регистра, вход сигнализашш которого соединен с выходом элемента И, а,выход

гть

fJL

т

уу

«fee - с второй вьпсодной шиной я входами деши ратора, выход которого соединен с входами мультиплексора, выход которого соединен со вторым входом элемента ЗАПРЕТ. Источники информации, принятые во внн 1ание прн экспертизе I, Авторское свидетельство СССР по заявке N 2477О25/21, кл. Н 03 К 13/20, 1977 (прототип).

п

тЕР

9

Авторы

Даты

1982-06-23—Публикация

1979-08-30—Подача