W J-1

Изобретение относится к вычислительной технике и технике связи и может быть использовано в многоканальных системах цифровой обработ- ки информации.

Цель изобретения - повышение достоверности и расширение области применения дельта-модулятора путем обеспечения возможности надежного и достоверного формирования многоканального дельта-кода.

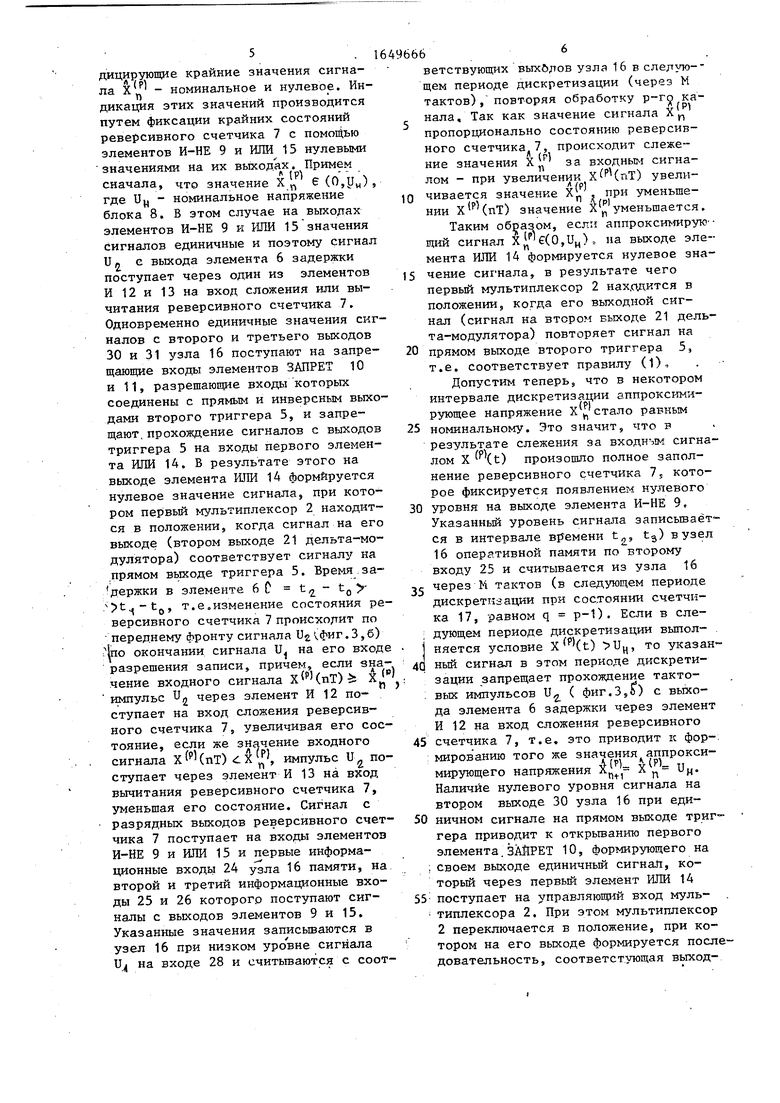

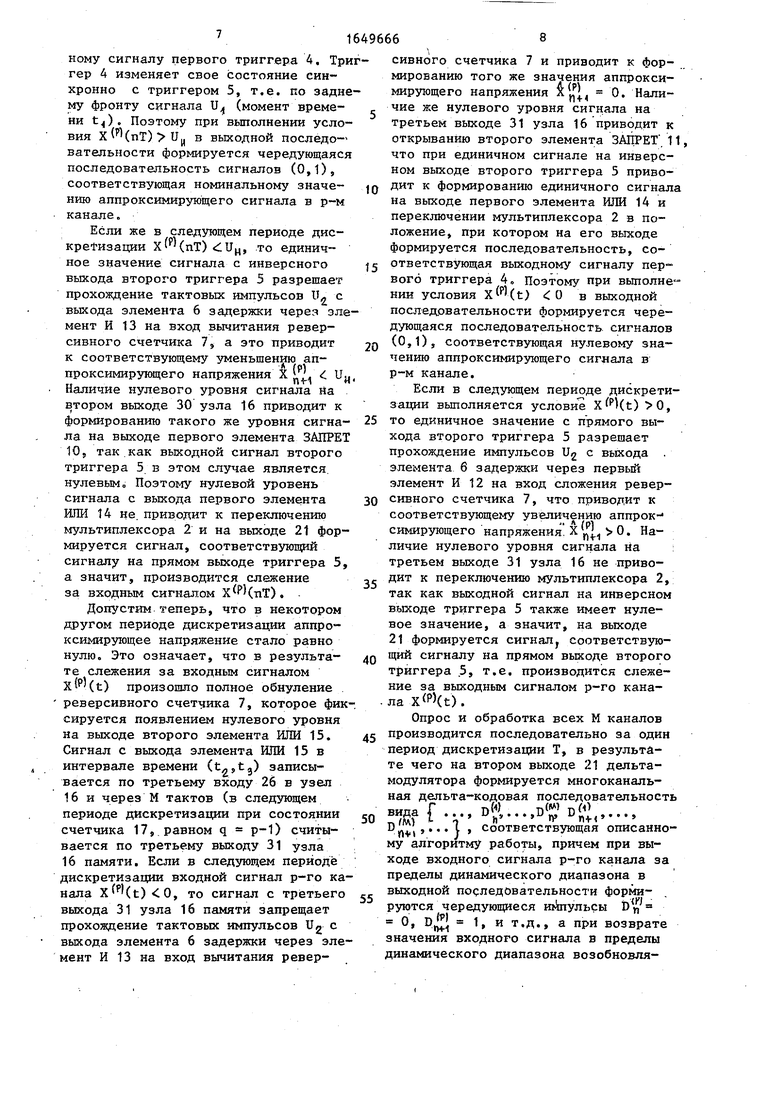

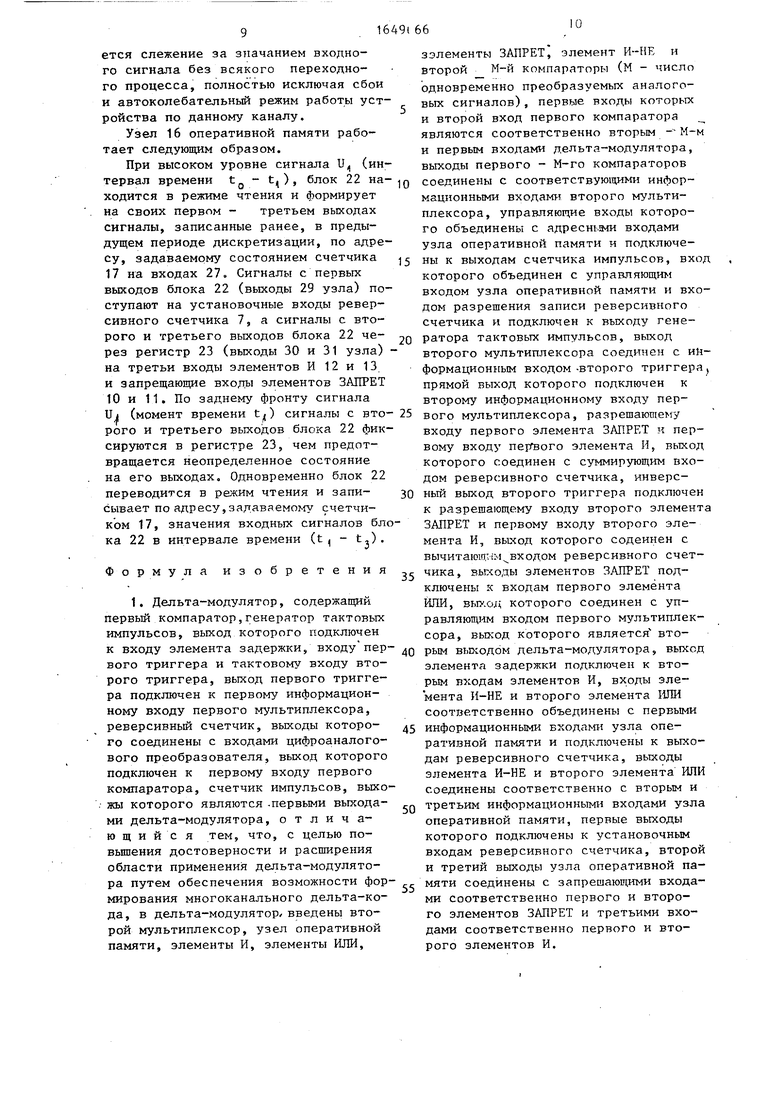

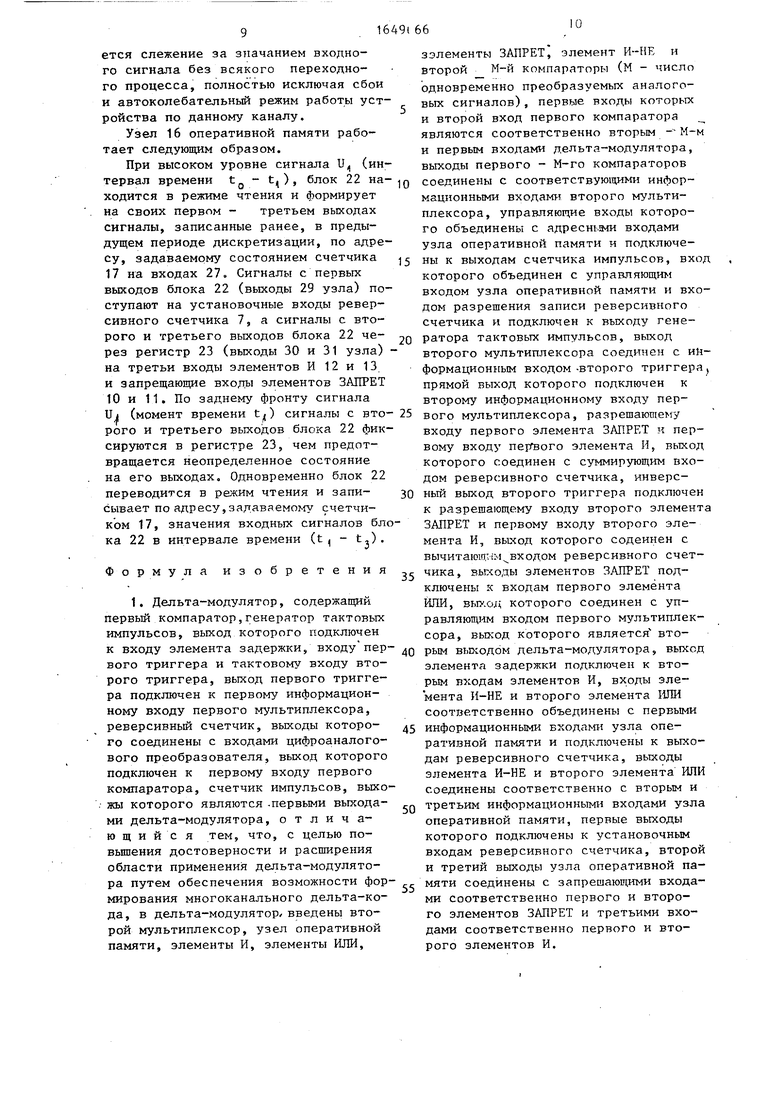

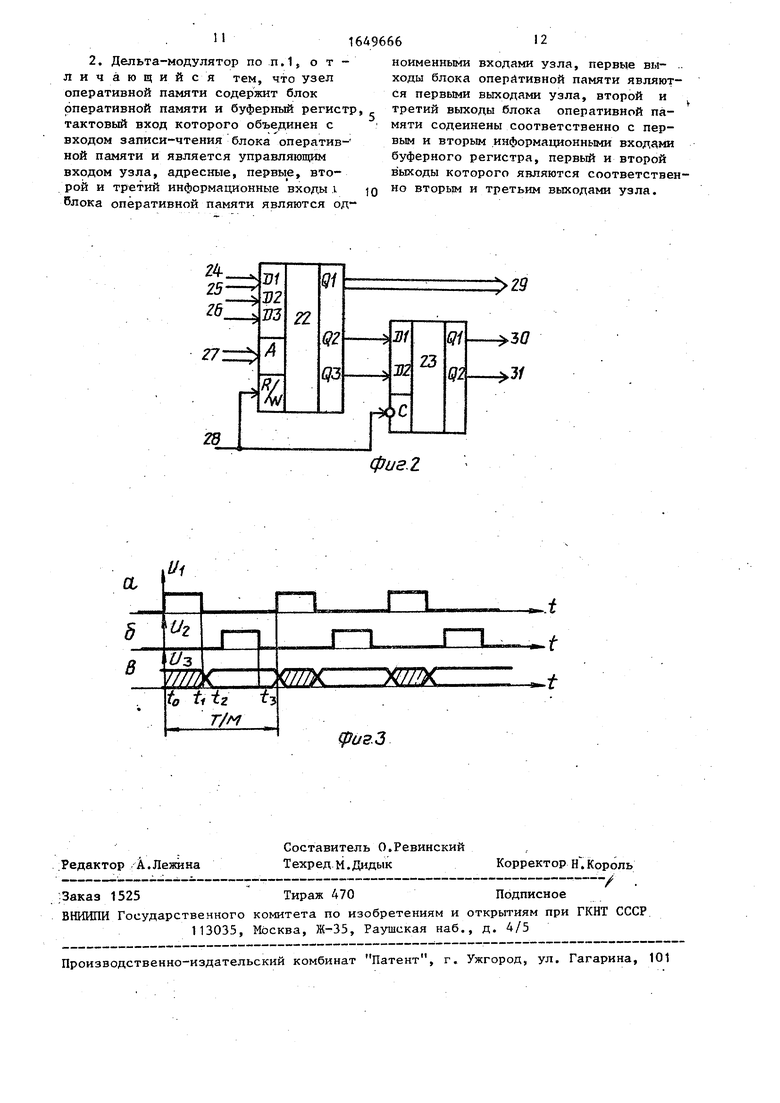

На фиг. 1 изображена блок-схема дельта-модулятора; на фиг.2 - схема узла оперативной памяти, на фиг. 3 - временные диаграммы работы.

Дельта-модулятор содержит компаратор 19 первый и второй мультиплексоры 2 и 3, первый и второй триггеры 4 и 5, элемент 6 задержки, ревер- сивный счетчик 7, цифроаналоговый преобразователь 8, элемент И-НЕ 9, первый и второй элементы ЗАПРЕТ 10 и 11, первый и второй элементы И 12 и 13, первый и второй элементы ИЛИ 14 и 15, узел 16 оперативной памяти, счетчик 17 импульсов, генератор 18 тактовых импульсов, входы 19, первый и второй выходы 20 и 21.

Узел 16 оперативной памяти выпол- нен (фиг.2) на блоке 22 оперативной памяти и буферном регистре 23 и содержит первый, второй и третий информационные входы 24-26, адресные входы

27, управляющий вход 28, первый, вто- 35 ПИСИ РевеРсивного счетчика

рой и третий выходы 29-31.

Дельта-модулятор работает следующим образом.

В дельта-модуляторе производится преобразование в цифровой последова- 40 тельный код входных аналоговых сигРассмотрим обработку и п вание р-го. входного сигнала модулятора )(t), р е { 1,М состоянии счетчика 17, равн выход компаратора 1.р подк к информационному входу три Одновременно при высоком уро ла поступающего на вход у ративной памяти и вход разреш

узла 16 считывается и запис в реверсивный счетчик 7 зна кода,

налов XW (t) - Xм (t), поступающих на входы 19.1-19.М, по правилу

соответствующее аппр

рующему сигналу р-го канал сформированное в предыдущем дискретизации.Сигнал с раз выходов реверсивного счетчи ступает на входы цифроанало преобразователя 8, на выход рого формируется значение с

D

W

- eignfxW(nT) ,1

де g 1, М - Х((пТ) X

W

т номер преобразуемого канала;

значение вхбдного сиг- нала q-ro канала в n-й момент дискретизации

период дискретизации; аппроксимирующее напряжение q-ro канала,

sign(Q) .

1,, О,а 0.

0 5

0

5 ПИСИ РевеРсивного счетчика

0

Генератор 18 тактовых импульсов ) генерирует непрерывную последовательность импульсов U (фиг.З) с частотой МТ . Указанная последовательность поступает на вход счетч ика 17 с коэффициентом пересчета М, изменяя состояние счетчика 17 по переднему фронту импульсов U.J (момент времени t0 на фиг.З). Сигнал с разрядных выходов счетчика 17 о Ј Г C,M-ll поступает на управляющие входы муль- типлексора 3, подключая выход q+1-го компаратора 1,(q+1) к информационному входу второго триггера 5, и одновременно на первые выходы 20 дельта- модулятора, индицируя номер обрабатываемого канала. Сигнал с разрядных выходов счетчика 17 поступает также на адресные входы 27 узла 16 оперативной памяти, поэтому опрос и обработка каждого входного сигнала повторяются периодически через М тактов сигнала т.е. с частотой дискретизации Т

Рассмотрим обработку и преобразование р-го. входного сигнала дельта- модулятора )(t), р е { 1,М| . При состоянии счетчика 17, равном q выход компаратора 1.р подключается к информационному входу триггера, Одновременно при высоком уровне сигнала поступающего на вход узла 16 ппе ративной памяти и вход разрешения за7, из

узла 16 считывается и записывается в реверсивный счетчик 7 значение кода,

5

0

5

соответствующее аппроксимиА / р

рующему сигналу р-го канала X , сформированное в предыдущем периоде дискретизации.Сигнал с разрядных выходов реверсивного счетчика / поступает на входы цифроаналогового преобразователя 8, на выходе которого формируется значение сигнала

Ti I п

X . Компаратор 1.р сравнивает значения (пТ) и формирует на своем выходе сигнал в соответствии с правилом (1). По заднему фронту сигнала U (момент времени t) указанное значение фиксируется во втором триггере 5, сигнал с прямого и инверсного выходов которого подается на первые входы соответственно первого и второго элементов И 12 и 13. На третьи входы указанных элементов И 12 и 13 с второго и третьего выходов 30 и 31 узла 16 оперативной памяти поступают сигналы, индотирующие крайние значения сигнала X

-MPl

номинальное и нулевое. Индикация этих значений производится путем фиксации крайних состояний реверсивного счетчика 7 с помощью элементов И-НЕ 9 и ИЛИ 15 нулевыми значениями на их выходах. Примем

К 1г

сначала, что значение X „ 6 (0,у„), где OH номинальное напряжение блока 8. В этом случае на выходах элементов И-НЕ 9 и ИЛИ 15 значения сигналов единичные и поэтому сигнал U n с выхода элемента 6 задержки поступает через один из элементов И 12 и 13 на вход сложения или вычитания реверсивного счетчика 7. Одновременно единичные значения сигналов с второго и третьего выходов 30 и 31 узла 16 поступают на запрещающие входы элементов ЗАПРЕТ 10 и 11, разрешающие входы которых соединены с прямым и инверсным выходами второго триггера 5, и запрещают, прохождение сигналов с выходов триггера 5 на входы первого элемента ИЛИ 14. В результате этого на выходе элемента ИЛИ 14 формируется нулевое значение сигнала, при котором первый мультиплексор 2 находит™ ся в положении, когда сигнал на его выходе (втором выходе 21 дельта-модулятора) соответствует сигналу на прямом выходе триггера 5. Время за- держки в элементе 6 С t - .е.изменение состояния рео

.,-t

версивного счетчика 7 происходит по переднему Фронту сигнала UЈ фиг .3,6)

Нпо окончании сигнала U. на

П

его входе

разрешения записи, причем, если значение входного сигнала x p (nT) xjp импульс U Ј через элемент И 12 поступает на вход сложения реверсивного счетчика 7, увеличивая его состояние, если же значение входного сигнала Х(пТ) , импульс U поступает через элемент И 13 на вход вычитания реверсивного счетчика 7, уменьшая его состояние. Сигнал с разрядных выходов реверсивного счетчика 7 поступает на входы элементов И-НЕ 9 и ИЛИ 15 и первые информационные входы 24 узла 16 памяти, на второй и третий информационные входы 25 и 26 которого поступают сигналы с выходов элементов 9 и 15. Указанные значения записываются в узел 16 при низком уровне сигнала на входе 28 и считываются с соот

5

0

ветствующих выходов узла 16 в следую-- щем периоде дискретизации (через М тактов), повторяя обработку p-rcj канала. Так как значение сигнала Хи пропорционально состоянию реверсивного счетчика.7, происходит слеже( Р ние значения X., за входным сигнап

лом - при увеличении ) увеличивается значение х п , при уменьшении X (пТ) значение л Ј уменьшается.

Таким образом, если аппроксимирую щий сигнал (0,UH) , на выходе элемента ИЛИ 14 формируется нулевое значение сигнала, в результате чего первый мультиплексор 2 находится в положении, когда его выходной сигнал (сигнал на втором выходе 21 дельта-модулятора) повторяет сигнал на прямом выходе второго триггера 5, т.е. соответствует правилу (1),

Допустим теперь, что в некотором интервале дискретизации аппроксими(PI

рующее напряжение XV стало равным

)

. 25

30

4G

номинальному. Это значит, что в результате слежения за входнътм сигналом X (t) произошло полное заполнение реверсивного счетчика 7, которое фиксируется появлением нулевого уровня на выходе элемента И-НЕ 9, Указанный уровень сигнала записывается в интервале времени t0, t3) в узел 16 оперативной памяти полвторому входу 25 и считывается из узла 16 ,с через М тактов (в следующем периоде дискретизации при состоянии счетчика 17, равном q р-1). Если в следующем периоде дискретизации выполняется условие X p (t) UH, то указан- ный сигнал в этом периоде дискретизации запрещает прохождение тактоU,

( фиг.3,б) с выхо45

вых импульсов

да элемента 6 задержки через элемент И 12 на вход сложения реверсивного счетчика 7, т.е. это приводит к формированию того же значения аппроксимирующего напряжения Х UH. Наличие нулевого уровня сигнала на втором выходе 30 узла 16 при еди50 ничном сигнале на прямом выходе триггера приводит к открыванию первого элемента.ЗАПРЕТ 10, формирующего на , своем выходе единичный сигнал, который через первый элемент ИЛИ 14

55 поступает на управляющий вход мультиплексора 2. При этом мультиплексор 2 переключается в положение, при котором на его выходе формируется последовательность, соответстующая выходному сигналу первого триггера 4. Тригер 4 изменяет свое состояние синхронно с триггером 5, т.е. по заднему фронту сигнала U (момент време- ни t). Поэтому при выполнении условия Х(пТ)ии в выходной последо-1 вательности формируется чередующаяся последовательность сигналов (0,1), соответствующая номинальному значе- нию аппроксимирующего сигнала в р-м канале„

Если же в следующем периоде дискретизации X (nT) 1 UH, то единичное значение сигнала с инверсного выхода второго триггера 5 разрешает прохождение тактовых импульсов U« с выхода элемента 6 задержки череч элемент И 13 на вход вычитания реверсивного счетчика 7, а это приводит к соответствующему уменьшению аппроксимирующего напряжения X Л i Ujj Наличие нулевого уровня сигнала на втором выходе 30 узла 16 приводят к формированию такого же уровня сигна- ла на выходе первого элемента ЗАПРЕТ 10,, так как выходной сигнал второго триггера 5 в этом случае является нулевым. Поэтому нулевой уровень сигнала с выхода первого элемента ИЛИ 14 не приводит к переключению мультиплексора 2 и на выходе 21 формируется сигнал, соответствующий сигналу на прямом выходе триггера 5, а значит, производится слежение за входным сигналом X(tiT).

Допустим теперь, что в некотором другом периоде дискретизации аппроксимирующее напряжение стало равно нулю. Это означает, что в результате слежения за входным сигналом xfp4t) произошло полное обнуление реверсивного счетчика 7, которое фиксируется появлением нулевого уровня на выходе второго элемента ИЛИ 15. Сигнал с выхода элемента ИЛИ 15 в интервале времени (t-,t3) записывается по третьему входу 26 в узел 16 и через М тактов (в следующем периоде дискретизации при состоянии счетчика 17, равном q р-1) считывается по третьему выходу 31 уэла 16 памяти. Если в следующем периоде дискретизации входной сигнал р-го канала X(t) 0, то сигнал с третьего выхода 31 узла 16 памяти запрещает прохождение тактовых импульсов U2 с выхода элемента 6 задержки через элемент И 13 на вход вычитания ревер

, JQ

у$ 20, 25 30

45JQ $$6496668

сивного счетчика 7 и приводит к формированию того же значения аппрокси35

40

мирующего напряжения 0. Наличие же нулевого уровня сигнала на третьем выходе 31 узла 16 приводит к открыванию второго элемента ЗАПРЕТ 11, что при единичном сигнале на инверсном выходе второго триггера 5 приводит к формированию единичного сигнала на выходе первого элемента ИЛИ 14 и переключении мультиплексора 2 в положение, при котором на его выходе формируется последовательность, соответствующая выходному сигналу первого триггера 4„ Поэтому при выполне нии условия (t) 0 в выходной последовательности формируется чередующаяся последовательность сигналов (0,1), соответствующая нулевому значению аппроксимирующего сигнала в р-м канале.

Если в следующем периоде дискретизации выполняется условие ) 0, то единичное значение с прямого выхода второго триггера 5 разрешает прохождение импульсов Ug с выхода элемента б задержки через первый элемент И 12 на вход сложения реверсивного счетчика 7, что приводит к соответствующему увеличению аппрок-1 симирующего напряжения X 0. Наличие нулевого уровня сигнала на третьем выходе 31 узла 16 не приводит к переключению мультиплексора 2, так как выходной сигнал на инверсном выходе триггера 5 также имеет нулевое значение, а значит, на выходе 21 формируется сигнал соответствующий сигналу на прямом выходе второго триггера 5, т.е. производится слежение за выходным сигналом р-го канала )(t).

Опрос и обработка всех М каналов производится последовательно за один период дискретизации Т, в результате чего на втором выходе 21 дельта- модулятора формируется многоканальная дельта-кодовая последовательность

BI$f f v

D ™1,... I , соответствующая описанному алгоритму работы, причем при выходе входного сигнала р-го канала за пределы динамического диапазона в выходной последовательности формируются чередующиеся импульсы D, 0, 1, и т.д., а при возврате значения входного сигнала в пределы динамического диапазона возобновляется слежение за значанием входного сигнала без всякого переходного процесса, полностью исключая сбои и автоколебательный режим работы устройства по данному каналу.

Узел 16 оперативной памяти работает следующим образом.

При высоком уровне сигнала U, (интервал времени tQ - t, ), блок 22 на- ходится в режиме чтения и формирует на своих первом - третьем выходах сигналы, записанные ранее, в предыдущем периоде дискретизации, по адресу, задаваемому состоянием счетчика 17 на входах 27. Сигналы с первых выходов блока 22 (выходы 29 узла) поступают на установочные входы реверсивного счетчика 7, а сигналы с второго и третьего выходов блока 22 че- рез регистр 23 (выходы 30 и 31 узла) - на третьи входы элементов И 12 и 13 и запрещающие входы элементов ЗАПРЕТ 10 и 11. По заднему фронту сигнала U (момент времени t) сигналы с вто- рого и третьего выходов блока 22 фиксируются в регистре 23, чем предотвращается неопределенное состояние на его выходах. Одновременно блок 22 переводится в режим чтения и запи- сывает по адресу,задаваемому счетчиком 17, значения входных сигналов блока 22 в интервале времени (t - t-).

Формула изобретения

1. Дельта-модулятор, содержащий первый компаратор,генератор тактовых импульсов, выход которого подключен к входу элемента задержки, входу пер- вого триггера и тактовому входу второго триггера, выход первого триггера подключен к первому информационному входу первого мультиплексора, реверсивный счетчик, выходы которо- го соединены с входами цифроаналого- вого преобразователя, выход которого подключен к первому входу первого компаратора, счетчик импульсов, выхо- жы которого являются -первыми выходами дельта-модулятора, отличающийся тем, что, с целью повышения достоверности и расширения области применения дельта-модулятора путем обеспечения возможности формирования многоканального дельта-кода, в дельта-модулятор/ введены второй мультиплексор, узел оперативной памяти, элементы И, элементы ИЛИ,

- jn 25 зо ,Q 5

50

5

зэлементы ЗАПРЕТ, элемент И-НЕ и второй М-и компараторы (М - число одновременно преобразуемых аналоговых сигналов), первые входы которых и второй вход первого компаратора являются соответственно вторым - М-м и первым входами дельта-модулятора, выходы первого - М-го компараторов соединены с соответствующими информационными входами второго мультиплексора, управляющие входы которого объединены с адресами входами узла оперативной памяти ч подключены к выходам счетчика импульсов, вход которого объединен с управляющим входом узла оперативной памяти и входом разрешения записи реверсивного счетчика и подключен к выходу генератора тактовых импульсов, выход второго мультиплексора соединен с информационным входом-второго триггера, прямой выход которого подключен к второму информационному входу первого мультиплексора, разрешающему входу первого элемента ЗАПРЕТ ч первому входу первого элемента И, выход которого соединен с суммирующим входом реверсивного счетчика, инверсный выход второго триггера подключен к разрешающему входу второго элемента ЗАПРЕТ и первому входу второго элемента И, выход которого содеинен с вычитаюш 1М входом реверсивного счетчика, выходы элементов ЗАПРЕТ подключены к входам первого элемента ИЛИ, выход которого соединен с управляющим входом первого мультиплексора, выход которого является вторым выходом дельта-модулятора, выход элемента задержки подключен к вторым входам элементов И, входы элемента И-НЕ и второго элемента ИЛИ соответственно объединены с первыми информационными входами узла оперативной памяти и подключены к выходам реверсивного счетчика, выходы элемента И-НЕ и второго элемента ИЛИ соединены соответственно с вторым и третьим информационными входами узла оперативной памяти, первые выходы которого подключены к установочным входам реверсивного счетчика, второй и третий выходы узла оперативной памяти соединены с запрещающими входами соответственно первого и второго элементов ЗАПРЕТ и третьими входами соответственно первого и второго элементов И.

n

2. Дельта-модулятор по п.1, о т - личающийся тем, что узел оперативной памяти содержит блок

1649666

12

поименными входами узла, первые выходы блока оперативной памяти являются первыми выходами узла, второй и

оперативной памяти и буферный регистр, третий выходы блока оперативной патактовый вход которого объединен с входом записи-чтения блока оператив- ной памяти и является управляющим входом узла, адресные, первые, второй и третий информационные входы i блока оперативной памяти являются од10

мяти содеинены соответственно с первым и вторым информационными входами буферного регистра, первый и второй выходы которого являются соответствен но вторым и третьим выходами узла.

12

поименными входами узла, первые выходы блока оперативной памяти являются первыми выходами узла, второй и

мяти содеинены соответственно с первым и вторым информационными входами буферного регистра, первый и второй выходы которого являются соответственно вторым и третьим выходами узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1501085A1 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

Изобретение относится к вычислительной технике и технике связи, .м.б. использовано в многоканальных системах цифровой обработки информации и позволяет повысить достоверность и расширить область применения дельта-модулятора путем обеспечения возможности достоверного формирования многоканального дельта- Кода. Дельта-модулятор содержит компаратор 1.1, мультиплексор 2, триг- . гер 4 и 5, элемент 6 задержки, реверсивный счетчик 7, цифроаналого- вый преобразователь 8, счетчик 17 импульсов и генератор 18 тактовых импульсов. Цель достигается благодаря введению компараторов 1.2-1.К (М - число одновременно преобразуемых аналоговых сигналов), мультиплексора 3, элемента И-НЕ 9, элементов ЗАПРЕТ 10, 11, элементов И 12, 13, элементов ШШ 14, 15 и узла 16 оперативной памяти. 1 з.п. ф-лы, 3 ил.

а

Ui

фиг.I

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР по заявке № 4415379/24, кл Н 03 М 3/02, 1988 | |||

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-03—Подача