1

Изобретение относится к гибридной вычислительной технике и предназначено для решения с помощью RC сеток задач оптимального управления конечным состоянием (финитное управ- ление) теплофизических объектов при наличии ограничений на координаты состояния объекта.

Цель изобретения - расширение класса решаемых задач за счет решения задачи с двусторонним управлением от двух независимых источников управляющего воздействия и повышения точности.

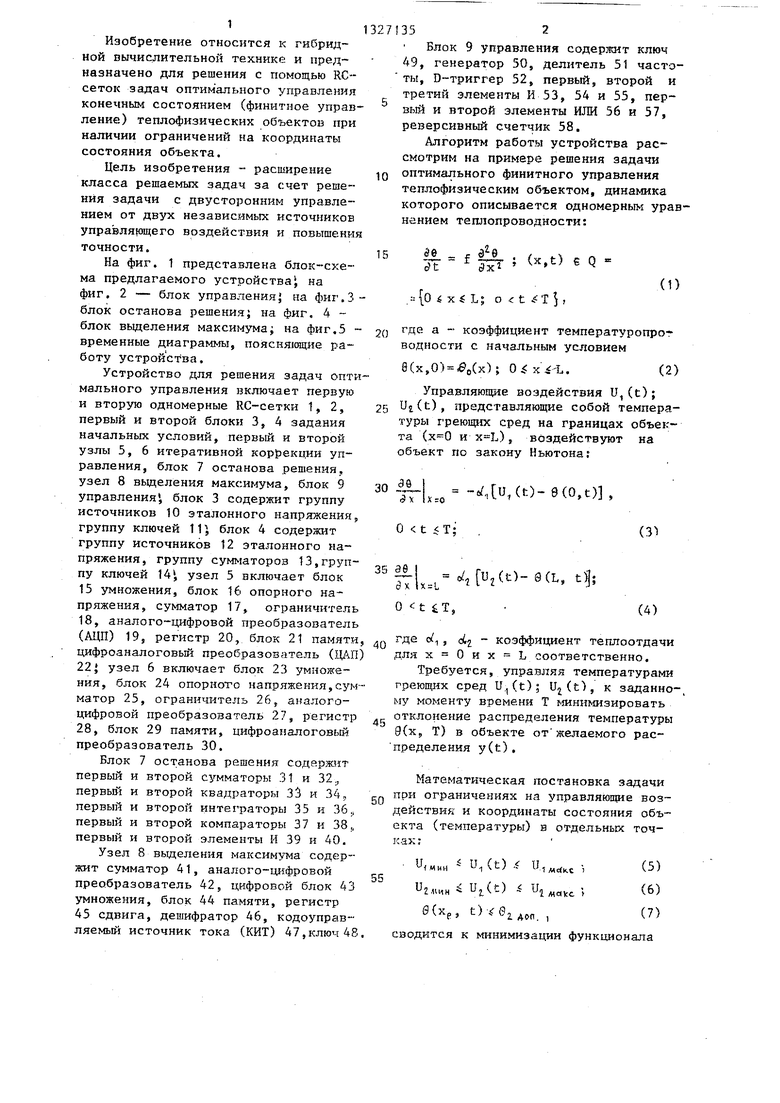

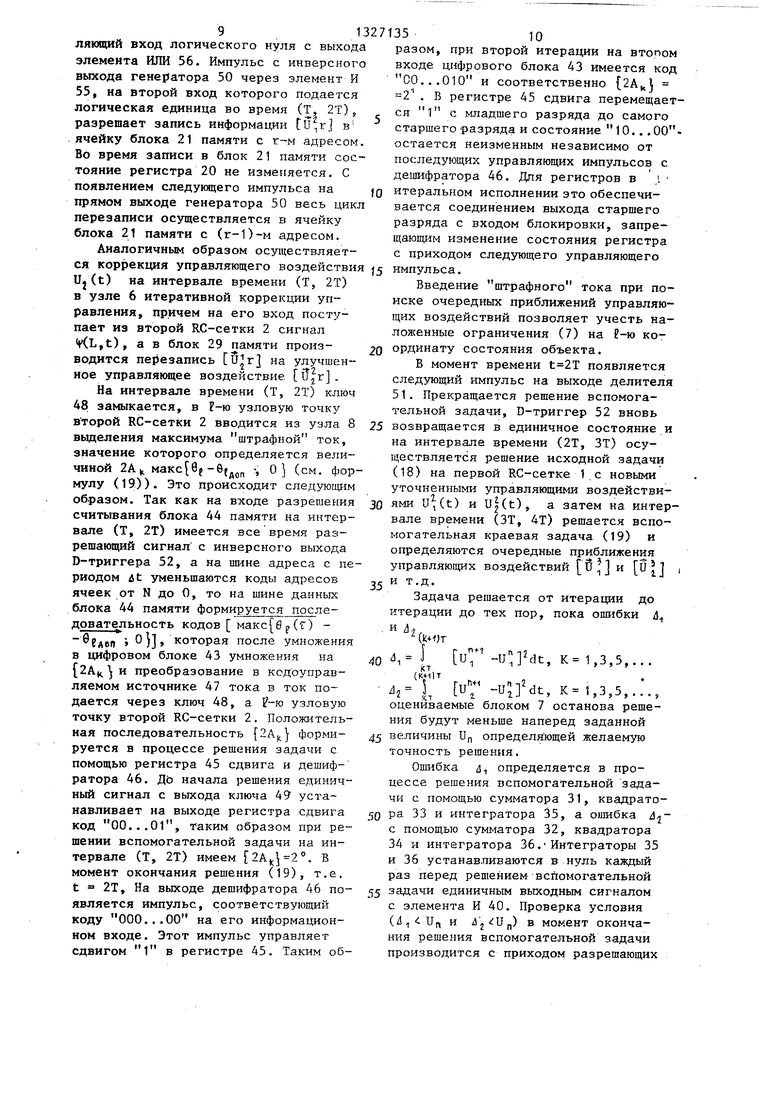

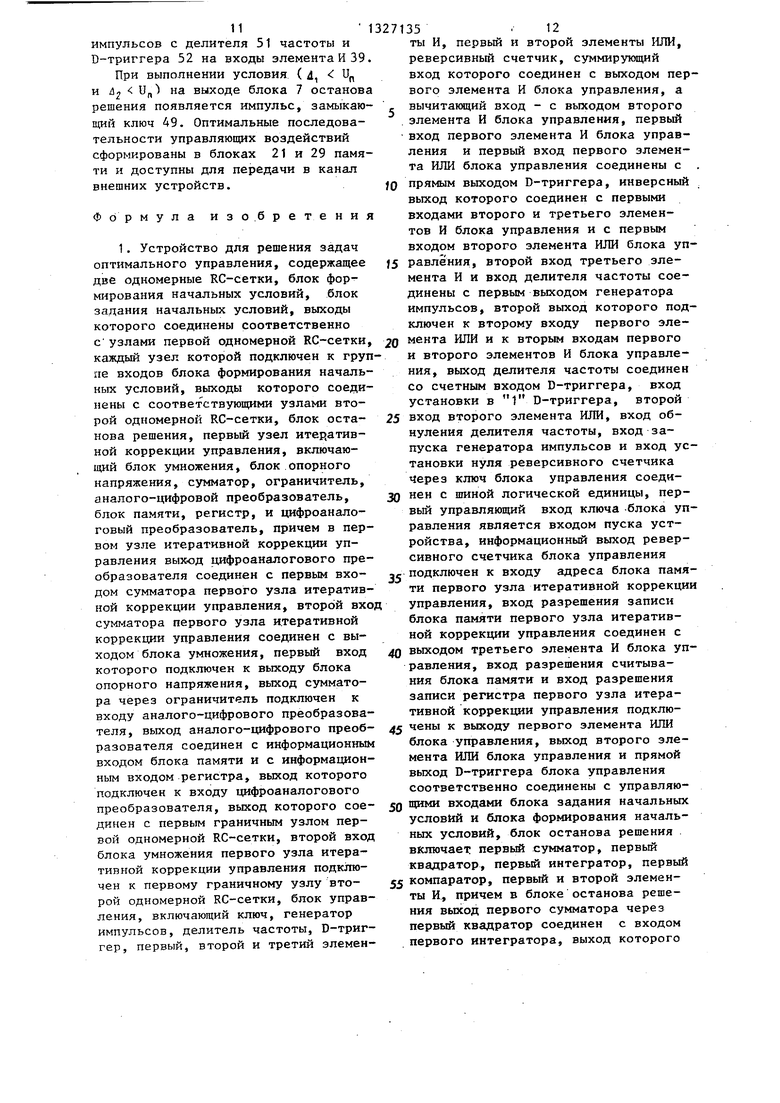

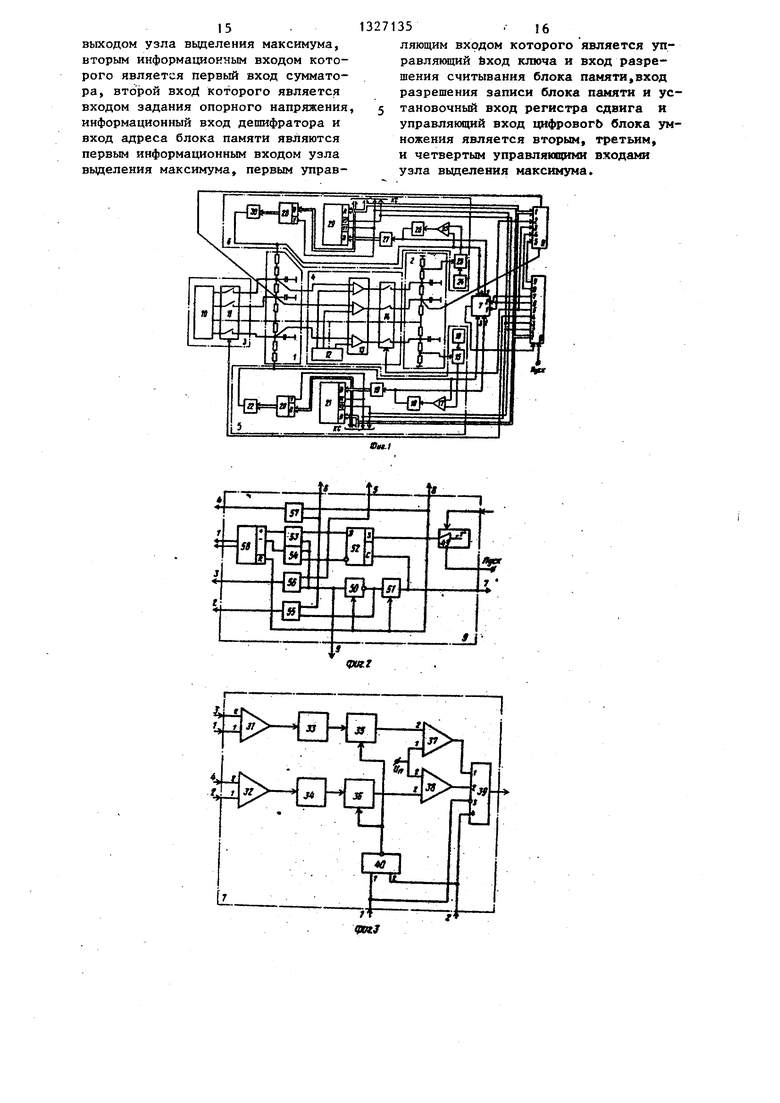

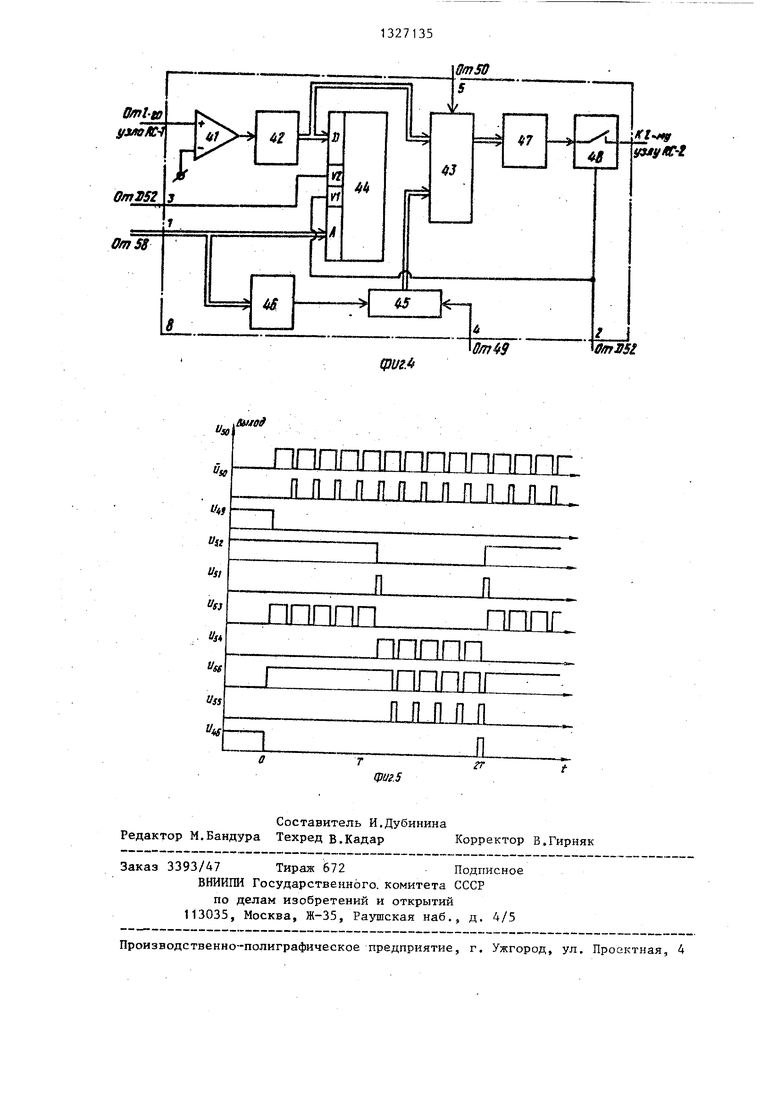

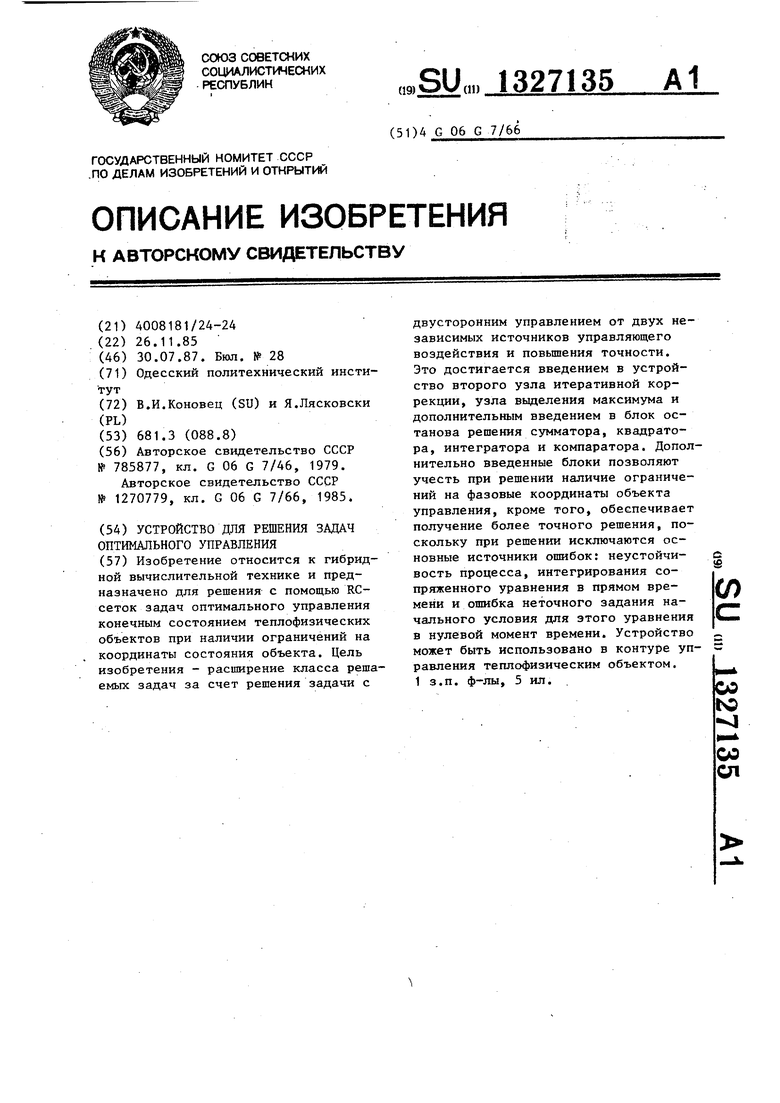

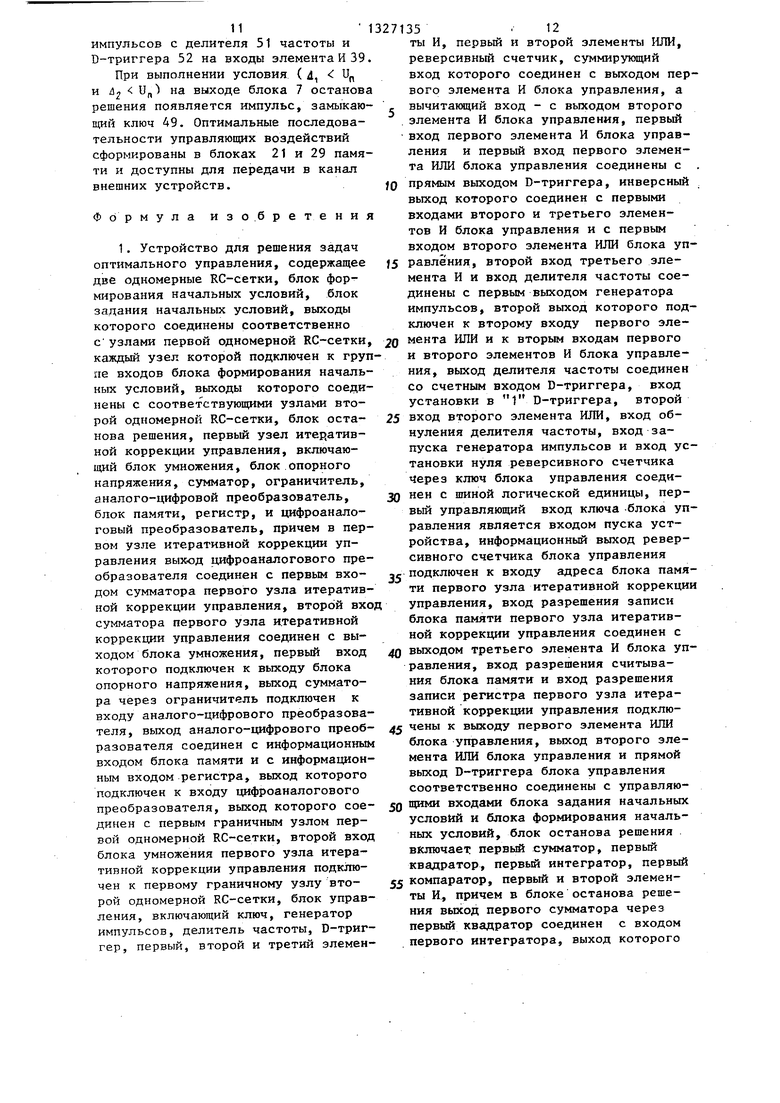

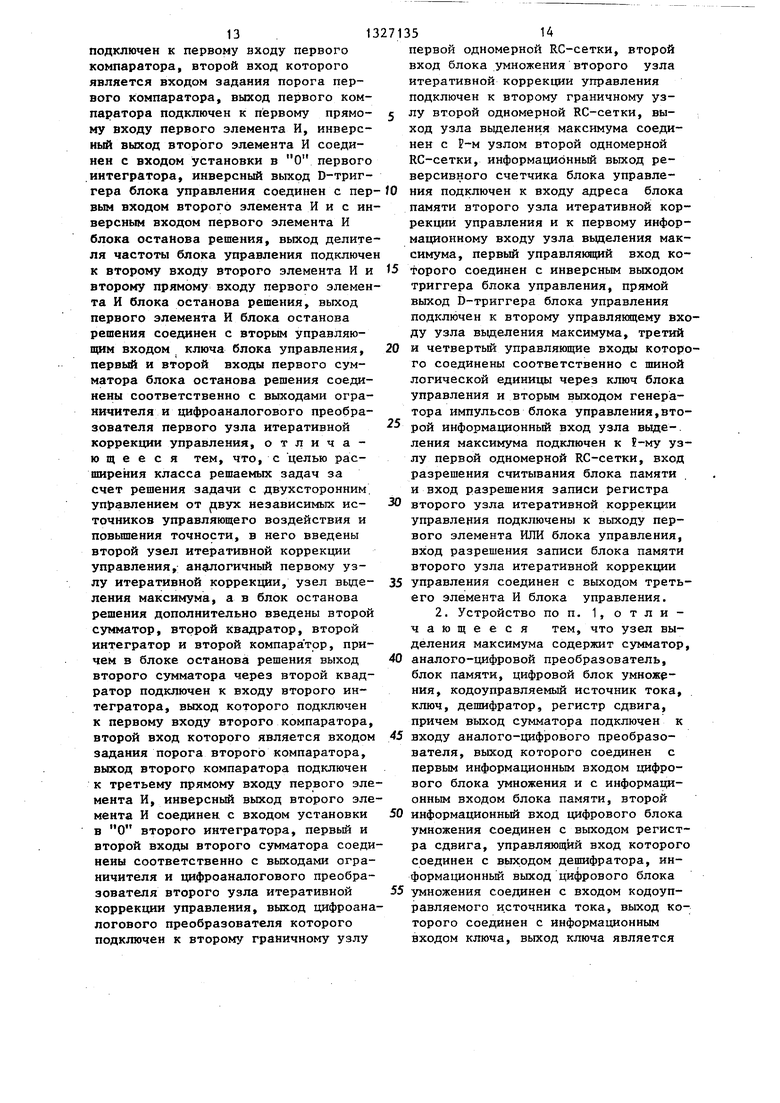

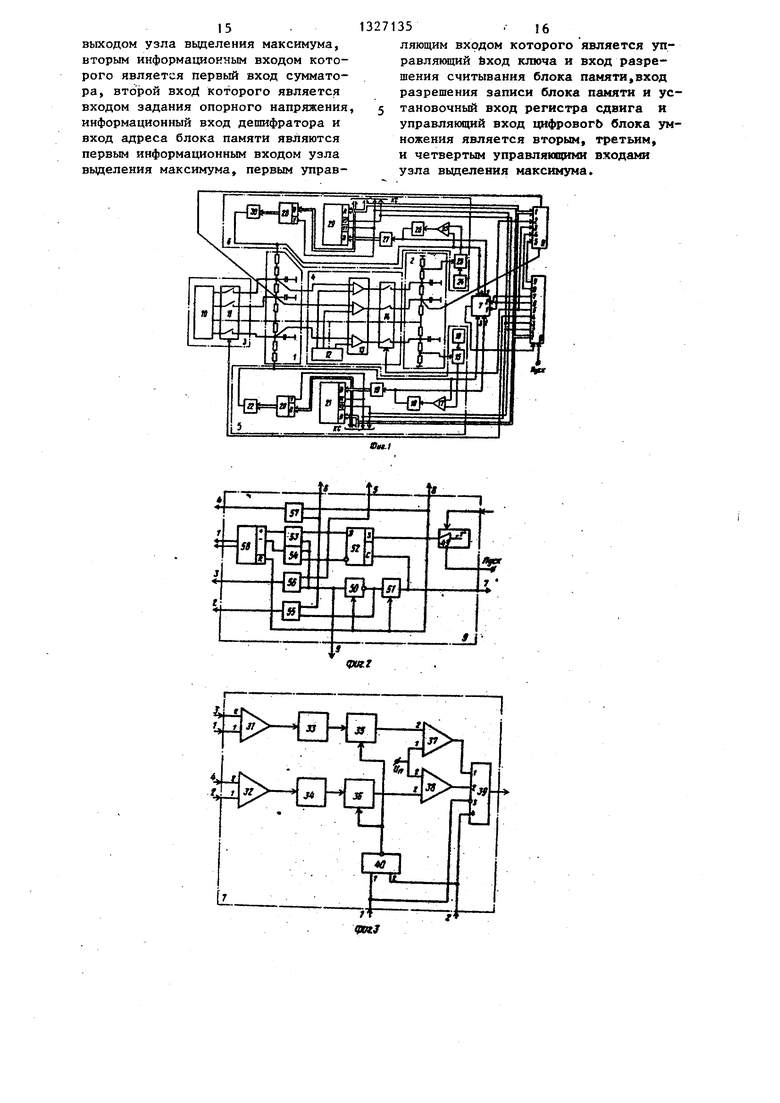

На фиг. 1 представлена блок-схема предлагаемого устройства на фиг. 2 - блок управления; на фиг.З- блок останова решения; на фиг. 4 - блок выделения максимума; на фиг.5 - временные диаграммы, поясняющие работу устройства.

Устройство для решения задач оптимального управления включает первую и вторую одномерные RC-сетки 1, 2, первый и второй блоки 3, 4 задания начальных условий, первый и второй узлы 5, 6 итеративной коррекции управления, блок 7 останова решения, узел 8 вьщеления максимума, блок 9 управления , блок 3 содержит группу источников 10 эталонного напряжения, группу ключей 11} блок 4 содержит группу источников 12 эталонного напряжения, группу сумматоров 13,группу ключей 14, узел 5 включает блок 15 умножения, блок 16 опорного напряжения, сумматор 17, ограничитель 18, аналого-цифровой преобразователь (АЦП) 19, регистр 20, блок 21 памяти цифроаналоговый преобразователь (ДАН 22i узел 6 включает блок 23 умножения, блок 24 опорного напряжения,сум матор 25, ограничитель 26, аналого- цифровой преобразователь 27, регистр 28, блок 29 памяти, цифроаналоговый преобразователь 30.

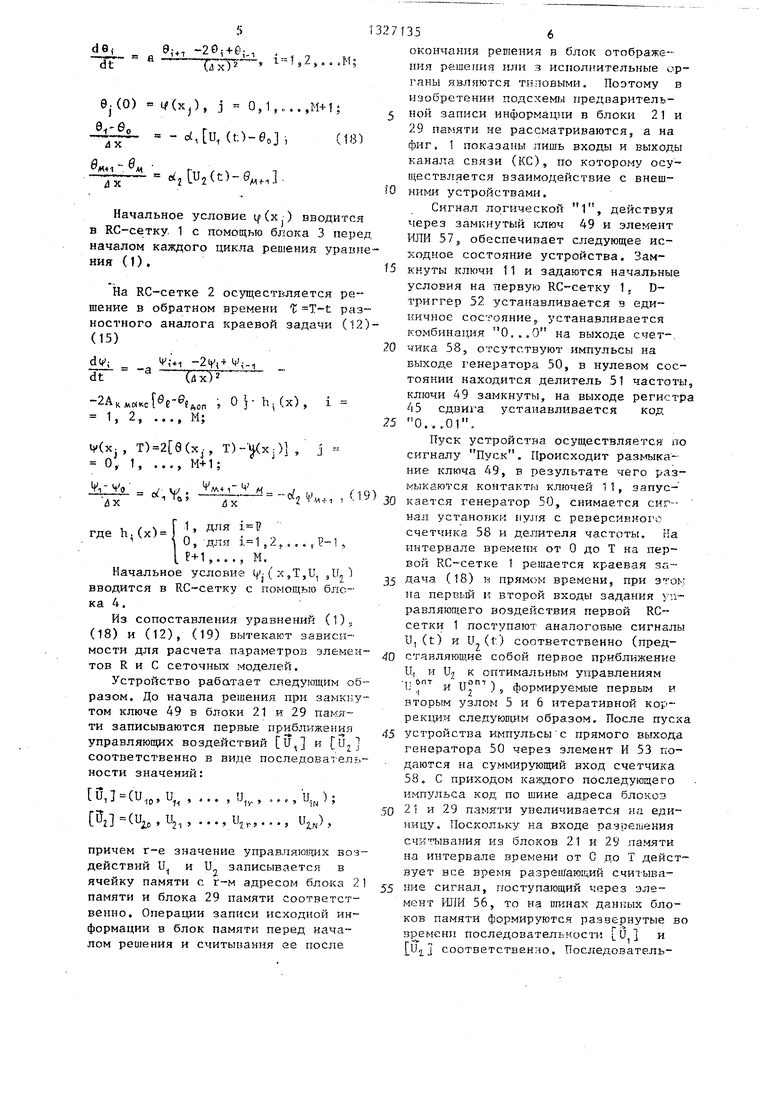

Блок 7 останова решения содерж.нт первый и второй сумматоры 31 и 32., первый и второй квадраторы 35 и 34, первый и второй интеграторы 35 и 36., первый и второй компараторы 37 и 38,, первый и второй элементы И 39 и 40.

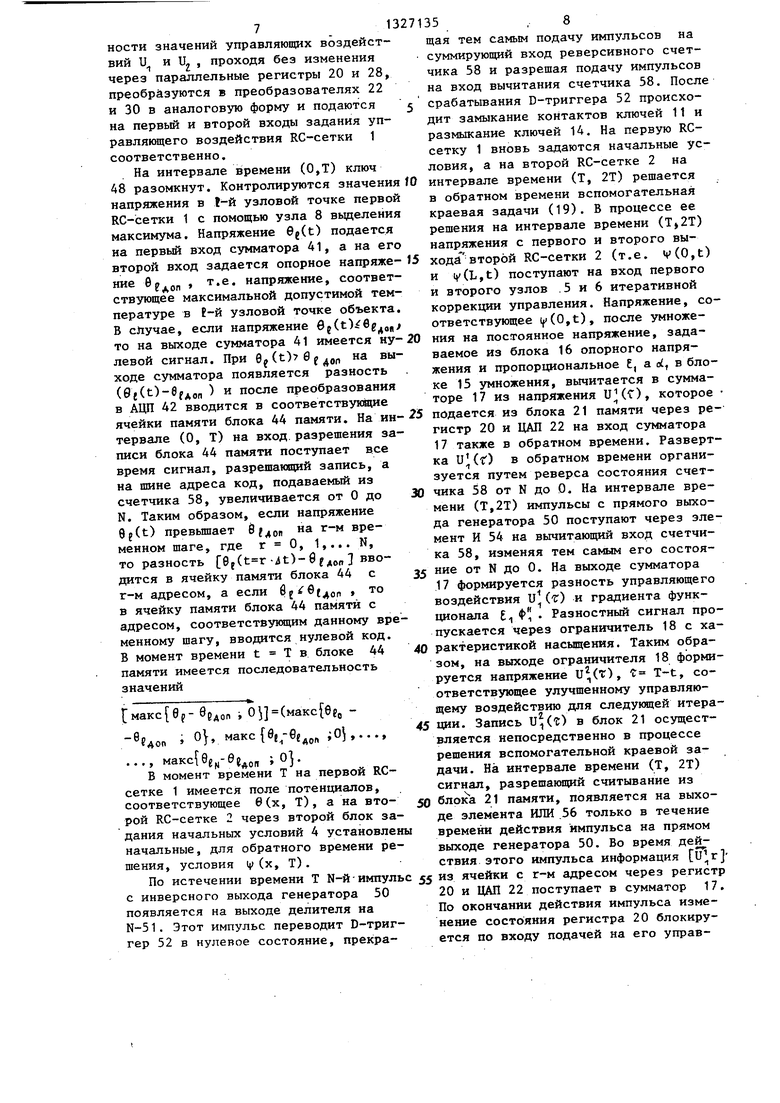

Узел 8 выделения максимума содержит сумматор 41, аналого-цифровой преобразователь 42, цифровой блок 43 умножения, блок 44 памяти, регистр 45 сдвига, дешифратор 46, кодоуправ- источник тока (КИТ) 47,ключ 48

352

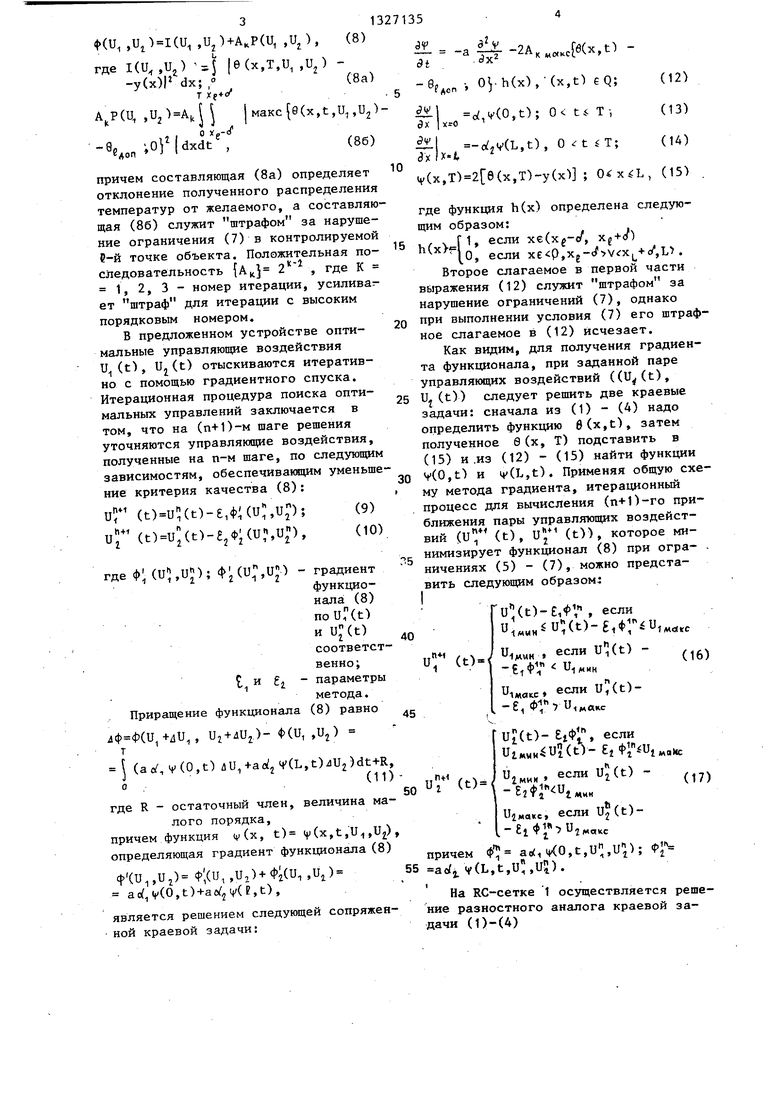

Блок 9 управления содержит ключ 49, генератор 50, делитель 51 частоты, D-триггер 52, первый, второй и третий элементы И 53, 54 и 55, первый и второй элементы ИЛИ 56 и 57, реверсивный счетчик 58.

Алгоритм работы устройства рассмотрим на примере решения задачи оптимального финитного управления теплофизическим объектом, динамика которого описывается одномерным уравнением теплопроводности:

15

|t..t).Q.

::{0 i х« L; о ft fl,

(1)

где а - коэффициент температуропрог водности с начальным условием

0(х,0) о(х) O fxi-L. (2)

Управляющие воздействия U,(t); Uj(t), представляющие собой температуры греющих сред на границах объекта ( и ), воздействуют на объект по закону Ньютона

°

36

iflr- tэ

,(t)-9(0,t),

1 А -О

О t Т; ,(3)

35

эе

ах

,,, -2 )- О :t iT,

где o , - коэффициент теплоотдачи ля X о и X L соответственно.

Требуется, управляя температурами греющих сред U;, (t); Uj,(t), к заданноу моменту времени Т минимизировать отклонение распределения температуры (х,, Т) в объекте от желаемого рас- ределения y(t).

Математическая постановка задачи при ограничениях на управляющие воздействия и координаты состояния объекта (температуры) н отдельных точкак;

. и,„,н Ui(t) -f u,Mc(K. -, (3)

иг«ин Ul(t) - UjMa.c (6)

0(хр, t).ei,n , (7)

сводится к минимизации функционала

ф(и, ,U,)I(U, ,U)(U, ,U), (8)

где I(U, ,Uj) --J |е(х,Т,Ц .Uj) -y(x)P dx; я(8a)

т Xf+o

(U, , |MaKc(e(x,t,U,U2)0 Xg-d

-Qe.nn ;of (dxdt

Aon

(86)

причем составляющая (8а) определяет отклонение полученного распределения температур от желаемого, а составляющая (86) служит штрафом за нарушение ограничения (7) в контролируемой Р-й точке объекта. Положительная по- следовательность Ац 2 , где К 1, 2, 3 - номер итерации, усиливает штраф для итерации с высоким порядковым номером.

В предложенном устройстве опти- мапьные управляющие воздействия и(t), и,(t) отыскиваются итеративно с помощью градиентного спуска. Итерационная процедура поиска оптимальных управлений заключается в том, что на (п+1)-м шаге решения уточняются управляющие воздействия, полученные на п-м шаге, по следующим зависимостям, обеспечивающим уменьшение критерия качества (8):

иГ (t)(t)-,Фuu;;,up; (9)

. + /. ч, /.ч Л Г/ттЛчПЧ(10)

(t)u(t)(u,up,

35

де Ф, (U.UJ); t 2(u;,Uj) - градиент

функционала (8) noUr(t)

40 соответственно; и f - параметры

метода. Приращение функционала (8) равно

45

(и,+4U, , и + ли)- Ф(и, ,Uj)

(as/, V(0,t) . 4(L,t)jU2)dt+R,

о(11)50

где R - остаточный член, величина малого порядка,

причем функция Ч (х, t) (t)(x,t ,U ,11) , определяющая градиент функционала (8)

(U,Uj) Ф ,(и,,и,)+Ф;(и, ,и) 55 ae/.,v(0,t)(,t),

является решением следующей сопряженной краевой задачи:

g

5t

- о 04

KMCXKCt

e(x,t) -. Oyh(x).-(x,t) 6Q; 1 o,v(0,t); 0 t. T-, I ,t), 0 t . T;

( Л V

v(x,T)(x,T)-y(x) ; , (15)

V Эх dv

ax

(12) (13) (14)

где функция h(x) определена следующим образом: h( если xe(, )

, если ,Xg-(,L .

Второе слагаемое в первой части выражения (12) служит штрафом за нарушение ограничений (7), однако при выполнении условия (7) его штрафное слагаемое в (12) исчезает.

Как видим, для получения градиента функционала, при заданной паре управляющих воздействий ((U(t), и, (t)) следует решить две краевые задачи: сначала из (1) - (4) надо определить функцию 6(x,t), затем полученное S(х. Т) подставить в (15) и .из (12) - (15) найти функции V(0,t) и iv(L,t). Применяя общую схему метода градиента, итерационный процесс для вычисления (п+1)-го приближения пары управляющих воздействий (и (t), (t)), которое минимизирует функционал (8) при огра- - ничениях (5) - (7), можно представить следующим образом:

U J()-,(; , если Уlм«н U ;(t)-,,,,

40

Г (t.)

45

50

55

UIM«H . если U ;(t) -е,Ф7 и1мик

UiMa«. если U(t)-е,,а,

Ui(t)- 1Ф; если и1м«« и1(Ь)-ЕгФ; и1

lM«K. если Ui(t) - -Ejtr UiMHH UjMetce, если U(t),

причем ф1 ae(,,t,U%U 3,); (L,t,,U).

I

Ha КС-сетке 1 осуществляется ние разностного аналога краевой дачи (1)-(4)

иГ (t)

а

;

8,.,, -20,-t-e;.,

ТГх)2

, ,...M;

9, (0) « 1/(хр, j - 0,1,M+l;

- c,u, (t:)-0,J, ci2tU2(t)-6,J.

(18)

Начальное условие t (x ) вводится

в RC-сетку. 1 с помощью блока 3 перед началом каждого цикла решения уравнения (1).

На RC-сетке 2 осуществляется решение в обратном времени разностного аналога краевой задачи (12)(15)

dV V.41 ..

dt

Тд1ГГ

-2Акмйкс Г гдоп , о J- h(x), i

1, 2, ..., М;25

V(x. , Т)(х. , Т)-ух:), j О, 1, ..., M-fl;

-.«,vi, .;,-„,.(W

, / «. Г 1 , для

гдеЬ.(х) ;, ,2....,-,

,..., М.

Начальное условие (x,T,U, ДО вводится в RC-сетку с помощью блс- ка 4.

Из сопоставления уравнений (1), (18) и (12), (19) вытекают зависимости для расчета параметров элементов R и С сеточных моделей.

Устройство рабатает следующим образом. До начала решения при замкп.у- том ключе 49 в блоки 21 и 29 памяти записываются первые Г риближения управляющих воздействий U и и соответственно в виде последовательности значений:

и,(и,,,,и, , ... ,и,., ,.., Ц.;

i(u, ,Uj, ...,115,,..., и,,,),

причем г-е значение управляюкгих воздействий U.J и и записывается в ячейку памяти с г-м адресом блока 2 памяти и блока 29 памяти соответственно. Операции записи исходной информации в блок памяти перед началом решения и считывания ее после

10

15

20

25

30

40

,

356

окончания реиения в блок отображения решения или :з испожштельные органы являются типовыми. Поэтому в нгзобретении подсхемы нредваритель- иой записи информации в блоки 21 и 29 не рассматриваются, а на фиг. 1 показаны лишь входы и выходы канала связи (КС), по которому осу- щecтвJfяeтcя взаимодействие с внешними устройствами.

Сигнал логической 1, действуя через замкнутый ключ 49 и элемент ИЛИ 57, обеспечивает следующее исходное состояние устройства. Зам- в:нуты ключи 11 и задаются начальные условия на первую RC-сетку 1, D- триггер 52 устанавливается в единичное состояние,, устанавливается комбинация 0...0 на выходе счет-, чика 58, отсутствуют импульсы на выходе генератора 50, в нулевом состоянии находится делитель 51 частоты, ключи 49 замкнуты, на выходе регистра 45 сдвига устанавливается код О..„01.

Пуск устройства осуществляется по сигналу Пуск. Происходит размыкание ключа 49, в результате чего размыкаются контакты ключей 1 I, запус- кается генератор 50, снимается сиг-нал установки нуля с реверсивного счетчика 58 и делителя частоты. На интервале времени от О до Т на первой RC-сетке t решается краевая задача (18) в прямом времени, при зтоы на первый и второй входы задания управляющего воздействия первой RC- сетки 1 поступают аналоговые сигналы и, (t) и и. (t.) соответственно (представляющие собой первое приближение и, и Uj к оптимальным управлениям

45

,- опт

и и.

)

2 - р формируемые первым и вторым узлом 5 и 6 итеративной коррекции следуюБЩм образом. После пуска устройства импульсы с прямого выхода генератора 50 через злемент И 53 подаются на суммирующий вход счетчика 58. С приходом каждого последующего импульса код по шине адреса блоков 21 и 29 памяти увеличивается на единицу. Поскольку на входе разрешения сч.и гъ1вания из блоков 21 и 29 памяти на интервале времени от С до Т действует все время разреи/ающий счи7-ыва- ние сигнал, поступающий через эле- мент 1 ШИ 56, то на шинах данных блоков памяти формируются развернутые во

f- Г -,

времени последовательности и lJ,j J соответственно. Последовательности значений управляющих воздействий и 1 проходя без изменения через параллельные регистры 20 и 28, преобразуются в преобразователях 22 и 30 в аналоговую форму и подаются на первый и второй входы задания управляющего воздействия RC-сетки 1 соответственно.

На интервале времени (О,Т) ключ

48 разомкнут. Контролируются значения 10 интервале времени (Т, 2Т) решается напряжения в 1-й узловой точке первой в обратном времени вспомогательная

краевая задачи (19). В процессе ее решения на интервале времени ()

КС-сетки 1 с помощью узла 8 выделения максимума. Напряжение {(t) подается на первый вход сумматора 41, а на его

напряжения с первого и второго вывторой вход задается опорное напряже-15 хода второй RC-сетки 2 (т.е. 4(0,t) ние 6g J, , т.е. напряжение, соответствующее максимальной допустимой температуре в Е-й узловой точке объекта. В случае, если напряжение ej(t)eg

и v(l ,t) поступают на вход первого и второго узлов .5 и 6 итеративной коррекции управления. Напряжение, соответствующее if(0,t), после умножето на выходе сумматора 41 имеется ну- 20 ния на постоянное напряжение, зада- левой сигнал. При 0f(t)00,op на вы- ваемое из блока 16 опорного напря- ходе сумматора появляется разность . жения и пропорциональное Е, а о(, в бло- (84(й)-будоп ) и после преобразования ке 15 умножения, вычитается в сумма- в АЦП 42 вводится в соответствующие торе 17 из напряжения U(T), которое ячейки памяти блока 44 памяти. На ин- 5 подается из блока 21 памяти через ретервале (О, Т) на вход.разрешения записи блока 44 памяти поступает все время сигнал, разрешающий запись, а на шине адреса код, подаваемый из счетчика 58, увеличивается от О до N. Таким образом, если напряжение 9f(t) превьш1ает 8(до„ на г-м временном шаге, где г О, 1,... N, то разность 0t( it)-9f до„ вводится в ячейку памяти блока 44 с г-м адресом, а если (дд„ , то в ячейку памяти блока 44 памяти с адресом, соответствунядим данному временному шагу, вводится нулевой код. В момент времени t Т в блоке 44 памяти имеется последовательность значений

макс{9р- 8рдоп ; 0( ОЬ MaKc{9j -ef, ;ОЬ..., ..., макс{9г -0е „ ; 0.

В момент времени Т на первой RC- сетке 1 имеется поле потенциалов, соответствующее в(х. Т), а на второй RC-сетке 2 через второй блок задания начальных условий 4 установлены начальные, для обратного времени ре50 блока 21 памяти, появляется на выходе элемента ИЛИ 56 только в течение времени действия импульса на прямом выходе генератора 50. Во время действия этого импульса информация Cui,

шения, условия v(х Т).

По истечении времени Т N-й-импульс 55 з ячейки с г-м адресом через регистр с инверсного выхода генератора 50 20 и ЦАП 22 поступает в сумматор 17. появляется на выходе делителя на По окончании действия импульса изме- N-51. Этот импульс переводит D-триг- некие состояния регистра 20 блокиру- гер 52 в нулевое состояние, прекра- ется по входу подачей на его управщая тем самым подачу импульсов на суммирующий вход реверсивного счетчика 58 и разрешая подачу импульсов на вход вычитания счетчика 58. После срабатывания D-триггера 52 происходит замыкание контактов ключей 11 и размыкание ключей 14. На первую RC- сетку 1 вновь задаются начальные условия, а на второй RC-сетке 2 на

напряжения с первого и второго выхода второй RC-сетки 2 (т.е. 4(0,t)

и v(l ,t) поступают на вход первого и второго узлов .5 и 6 итеративной коррекции управления. Напряжение, соответствующее if(0,t), после умножегистр 20 и ЦАП 22 на вход сумматора 17 также в обратном времени. Развертка ) в обратном времени организуется путем реверса состояния счет30 чика 58 от N до 0. На интервале времени (Т,2Т) импульсы с прямого выхода генератора 50 поступают через элемент И 54 на вычитающий вход счетчика 58, изменяя тем самым его состоя35 ние от N до 0. На выходе сумматора 17 формируется разность управляющего воздействия U () и градиента функционала Е Ф . Разностный сигнал пропускается через ограничитель 18 с ха40 рактеристикой насьщения. Таким образом, на выходе ограничителя 18 формируется напряжение U(T), t T-t, соответствующее улучшенному управляющему воздействию для следующей итера45 ции. Запись U-,(t) в блок 21 осуществляется непосредственно в процессе решения вспомогательной краевой задачи. На интервале времени (Т, 2Т) сигнал, разрешающий считывание из

50 блока 21 памяти, появляется на выходе элемента ИЛИ 56 только в течение времени действия импульса на прямом выходе генератора 50. Во время действия этого импульса информация Cui,r

55 з ячейки с г-м адресом через регистр 20 и ЦАП 22 поступает в сумматор 17. По окончании действия импульса изме- некие состояния регистра 20 блокиру- ется по входу подачей на его управляклций вход логического нуля с выхода элемента ИЛИ 56. Импульс с инверсного выхода генератора 50 через элемент И 55, на второй вход которого подается логическая единица во время (Т, 2Т), разрешает запись информации в ячейку блока 21 памяти с г-м адресом. Во время записи в блок 21 памяти состояние регистра 20 не изменяется. С появлением следующего импульса на прямом выходе генератора 50 весь цикл перезаписи осуществляется в ячейку блока 21 памяти с (г-1)-м адресом. Аналогичным образом осуп(ествляет

ся коррекция управляющего воздейств

Uj(t) на интервале времени (Т, 2Т) в узле 6 итеративной коррекции управления, причем на его вход поступает из второй RC-сетки 2 сигнал V(L,t), а в блок 29 памяти производится перезапись Sjr на улучшенное управляющее воздействие iT,,r.

На интервале времени (Т, 2Т) клю 48 замыкается, в -ю узловую точку второй RC-сетки 2 вводится из уала выделения максимума штрафной ток, значение которого определяется величиной 2А (-6(ддг, -, 0 (см. фомулу (19.)). Это происходит следзпощи образом. Так как на входе разрешени считывания блока 44 памяти на интервале (Т, 2Т) имеется все время разрешающий сигнал с инверснох о выхода D-триггера 52, а на шине адреса с приодом ut уменьшаются коды адресов ячеек от N до О, то на шине данных блока 44 памяти формир ется последовательность кодов ) - Авп ОJj, которая после умножени в цифровом блоке 43 умножения на (И преобразование в ксдоуправ- ляемом источнике 47 тока в ток подается через ключ 48, а И-ю узловую точку второй RC-сетки 2. Положительная последовательность формируется в процессе решения задачи с помощью регистра 45 сдвига и дешифратора 46. До начала решения единичный сигнал с выхода ключа 49 устанавливает на выходе регистра сдвига код 00...01, таким образом при решении вспомогательной задачи на интервале (Т, 2Т) имеем 2А,2°. В момент окончания решения (19), т.е. t 2Т, На выходе дешифратора 46 появляется импульс, соответствующий коду 000...00 на его информационном входе. Этот импульс управляет сдвигом 1 в регистре 45. Таким об

7135

10

разом, при второй итерации на втором входе цифрового блока 43 имеется код 00...010 и соответственно 2. В регистре 45 сдвига перемещается 1 с младшего разряда до самого старшего разряда и состояние 10.. . остается неизменным независимо от последующих управляющих импульсов с дешифратора 46. Для регистров в ,1 итеральном исполнении это обеспечивается соединением выхода старшего разряда с входом блокировки, запрещающим изменение состояния регистра с приходом следующего управляющего

0

0

5

5

0

Введение штрафного тока при поиске очередных приближений управляющих воздействий позволяет учесть наложенные ограничения (7) на Е-ю координату состояния объекта.

В момент времени появляется следующий импульс на выходе делителя 51. Прекращается решение вспомогательной задачи, D-триггер 52 вновь возвращается в единичное состояние и на интервале времени (2Т, ЗТ) осуществляется решение исходной задачи (18) на первой RC-сетке 1.с новыми уточненными управляющими воздействиями U,(t) и u|(t), а затем на интервале времени (ЗТ, 4Т) решается вспомогательная краевая задача (19) и определяются очередные приближения управляющих воздействий б j и U М i и т.д.

Задача решается от итерации до итерации до тех пор, пока ошибки й

и 4. (fc+fjr

fг тч

d, J и -U jl dt, ,3,5,...

Г1+1

кт (км) т

2 5

кт-

оцениваемые блоком 7

и

,hi2

, К 1,3,5,..., останова решения будут меньше наперед заданной

25

45

величины Up определяющей желаемую

точность решения.

Ошибка d, определяется в процессе решения вспомогательной задачи с помощью cyMt-iaTopa 31, квадратора 33 и интегратора 35, а ошибка jjj- с помощью сумматора 32, квадратора 34 и интегратора 36. Интеграторы 35 и 36 устанавливаются в нуль каждый раз перед решением вспомогательной

задачи единичным выходным сигналом с злемента И 40. Проверка условия (4,iUn и dj-JU) в момент окончания решения вспомогательной задачи производится с приходом разрешающих

11

импульсов с делителя 51 частоты и D-триггера 52 на входы элемента И 39.

При выполнении условия (4, и 2 Un) на выходе блока 7 останова решения появляется импульс, замыкающий ключ 49. Оптимальные последовательности управляющих воздействий сформированы в блоках 21 и 29 памяти и доступны для передачи в канал внешних устройств.

Формула изобретения

1. Устройство для решения задач оптимального управления, содержащее две одномерные RC-сетки, блок формирования начальных условий, блок задания начальных условий, выходы которого соединены соответственно с узлами первой одномерной RC-сетки каждый узел которой подключен к группе входов блока формирования начальных условий, выходы которого соединены с соответствующими узлами второй одномерной RC-сетки, блок останова решения, первый узел итер,атив- ной коррекции управления, включающий блок умножения, блок опорного напряжения, сумматор, ограничитель, аналого-цифровой преобразователь, блок памяти, регистр, и цифроанало- говый преобразователь, причем в первом узле итеративной коррекции управления выход цифроаналогового преобразователя соединен с первым входом сумматора первого узла итеративной коррекции управления, второй вхо сумматора первого узла итеративной коррекции управления соединен с выходом блока умножения, первый вход которого подключен к выходу блока опорного напряжения, выход сумматора через ограничитель подключен к входу аналого-цифрового преобразователя, выход аналого-цифрового преобразователя соединен с информационным входом блока памяти и с информационным входом регистра, выход которого подключен к входу цифроаналогового преобразователя, выход которого соединен с первым граничным узлом первой одномерной RC-сетки, второй вход блока умножения первого узла итеративной коррекции управления подключен к первому граничному узлу второй одномерной RC-сетки, блок управления, включающий ключ, генератор импульсов, делитель частоты, D-триг- гер, первый, второй и третий элемен

Ш

15

20

25

327135. 12

ты И, первый и второй элементы ИЛИ, реверсивный счетчик, суммирующий вход которого соединен с выходом первого элемента И блока управления, а вычитающий вход - с выходом второго элемента И блока управления, первый вход первого элемента И блока управления и первый вход первого элемента ИЛИ блока управления соединены с . прямым выходом D-триггера, инверсный выход которого соединен с первыми входами второго и третьего элементов И блока управления и с первым входом второго элемента ИЛИ блока управления, второй вход третьего элемента И и вход делителя частоты соединены с первым выходом генератора импульсов, второй выход которого подключен к второму входу первого элемента ИЛИ и к вторым входам первого и второго элементов И блока управления, выход делителя частоты соединен со счетным входом D-триггера, вход установки в 1 D-триггера, второй вход второго элемента ИЛИ, вход обнуления делителя частоты, вход запуска генератора импульсов и вход установки нуля реверсивного счетчика Через ключ блока управления соединен с шиной логической единицы, первый управляющий вход ключа блока управления является входом пуска устройства, информационный выход реверсивного счетчика блока управления подключен к входу адреса блока памяти первого узла итеративной коррекции управления, вход разрешения записи блока памяти первого узла итеративной коррекции управления соединен с выходом третьего элемента И блока управления, вход разрешения считывания блока памяти и вход разрешения записи регистра первого узла итеративной коррекции управления подключены к выходу первого элемента ИЛИ блока управления, вькод второго элемента ИЛИ блока управления и прямой выход D-триггера блока управления соответственно соединены с управляю50 щими входами блока задания начальных условий и блока формирования начальных условий, блок останова решения включает первый сумматор, первый квадратор, первый интегратор, первый

55 компаратор, первый и второй элементы И, причем в блоке останова решения выход первого сумматора через первый квадратор соединен с входом первого интегратора, выход которого

30

35

40

45

подключен к первому входу первого компаратора, второй вход которого является входом задания порога первого компаратора, выход первого компаратора подключен к первому прямо- му входу первого элемента И, инверсный выход второго элемента И соединен с входом установки в О первого интегратора, инверсный выход D-триг- гера блока управления соединен с пер вым входом второго элемента И и с инверсным входом первого элемента И блока останова решения, выход делителя частоты блока управления подключе к второму входу второго элемента И и второму прямому входу первого элемента И блока останова решения, выход первого элемента И блока останова решения соединен с вторым управляющим входом ключа блока управления, первый и второй входы первого сумматора блока останова решения соединены соответственно с выходами ограничителя и цифроаналогового преобразователя первого узла итеративной коррекции управления, отличающееся тем, что, с целью расширения класса решаемых задач за счет решения задачи с двухсторонним, управлением от р,вух. независимых источников управляющего воздействия и повьш1ения точности, в него введены второй узел итеративной коррекции управления, аналогичный первому узлу итеративной коррекции, узел выделения максимума, а в блок останова решения дополнительно введены второй сумматор, второй квадратор, второй интегратор и второй компаратор, причем в блоке останова решения выход второго сумматора через второй квадратор подключен к входу второго интегратора, выход которого подключен к первому входу второго компаратора, второй вход которого является входом задания порога второго компаратора, выход второго компаратора подключен к третьему прямому входу первого элемента И, инверсный выход второго элемента И соединен с входом установки в О второго интегратора, первый и второй входы второго сумматора соединены соответственно с выходами ограничителя и цифроаналогового преобразователя второго узла итеративной коррекции управления, выход цифроаналогового преобразователя которого подключен к второму граничному узлу

первой одномерной RC-сетки, второй вход блока умножения второго узла итеративной коррекции управления подключен к второму граничному узлу второй одномерной RC-сетки, выход узла выделения максимума соединен с Р-м узлом второй одномерной RC-сетки, информационный выход реверсивного счетчика блока управления подключен к входу адреса блока памяти второго узла итеративной коррекции управления и к первому информационному входу узла вьщеления максимума, первый управляющий вход которого соединен с инверсным выходом триггера блока управления, прямой выход D-триггера блока управления подключен к второму управлякщему входу узла выделения максимума, третий и четвертый управляющие входы которого соединены соответственно с шиной логической единицы через ключ блока управления и вторым выходом генератора импульсов блока управления,второй информационный вход узла вьще-. ления максимума подключен к -му узлу первой одномерной RC-сетки, вход разрешения считывания блока памяти и вход разрешения записи регистра второго узла итеративной коррекции управления подключены к выходу первого элемента ИЛИ блока управления, вход разрешения записи блока памяти второго узла итеративной коррекции управления соединен с выходом третьего элемента И блока управления.

2. Устройство по п, 1, отличающееся тем, что узел выделения максимума содержит сумматор, аналого-цифровой преобразователь, блок памяти, цифровой блок умножения, кодоуправляемьй источник тока, ключ, дешифратор, регистр сдвига, причем вькод сумматора подключен к

входу аналого-цифрового преобразователя, выход которого соединен с первым информационным входом цифрового блока умножения и с информационным входом блока памяти, второй

информационньй вход цифрового блока умножения соединен с выходом регистра сдвига, управляющий вход которого соединен с выходом дешифратора, информационный выход цифрового блока

умножения соединен с входом кодоуп- равляемого и.сточника тока, выход которого соединен с информационным входом ключа, выход ключа является

15

выходом узла вьзделения максимума, вторым информационным входом которого является первый вход сумматора, второй вход которого является входом задания опорного напряжения информационный вход дешифратора и вход адреса блока памяти являются первым информационным входом узла выделения максимума, первым управ1327135. 16

ляющим входом которого является управляющий йход ключа и вход разрешения считывания блока памяти,вход разрешения записи блока памяти и ус- 5 тановочный вход регистра сдвига и управляющий вход цифровогЬ блока умножения является вторым, третьим, и четвертым управляющими входами узла выделения максимума.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения задач оптимального управления | 1985 |

|

SU1270779A1 |

| Устройство для моделирования оптимальной системы управления | 1984 |

|

SU1233188A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| Устройство для моделирования оптимальной системы управления | 1985 |

|

SU1288729A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для передачи информации со сжатием | 1983 |

|

SU1091206A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

Изобретение относится к гибридной вычислительной технике и предназначено для решения с помощью RC- сеток задач оптимального управления конечным состоянием теплофизических объектов при наличии ограничений на координаты состояния объекта. Цель изобретения - расширение класса решаемых задач за счет решения задачи с двусторонним управлением от двух независимых источников управляющего воздействия и повьш1ения точности. Это достигается введением в устройство второго узла итеративной коррекции, узла вьщеления максимума и дополнительным введением в блок останова решения сумматора, квадратора, интегратора и компаратора. Дополнительно введенные блоки позволяют учесть при решении наличие ограничений на фазовые координаты объекта управления, кроме того, обеспечивает получение более точного решения, поскольку при решении исключаются основные источники ошибок: неустойчивость процесса, интегрирования сопряженного уравнения в прямом времени и ошибка неточного задания начального условия для этого уравнения в нулевой момент времени. Устройство может быть использовано в контуре управления теплофизическим объектом. 1 з.п. ф-лы, 5 ил. с (Л

чялг

L.

| Устройство для решения задач оптимального управления | 1979 |

|

SU785877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1270779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1985-11-26—Подача