Изобретение относится к автоматике и вычислительной технике и может быть использо&ано при построении устройств и систем отображения информации.

Известны аналоговые устройства, позволяющие отображать на экране электроннолучевой трубки графическую информациюВ этом устройстве формирование сигналов, подаваемых на выхоонью каскацы и систему отклонения электроннолучевой JQ трубки, производится с помощью схем, состоящих из цнфференциальньрс усилителей, аналоговых интеграторов, аналоговых умножителей l.

Обшим недостатком этих устройств

является низкая точность формируемых сигналов отклонения, что приводит к искажениям информации, неприемлемым в большинстве современных рациотехничес- 20 ких информационных систем.

Наиболее близким по технической сущности к предлагаемому устройству явл5 ется цифровой генератор графической информации, содержащий по каждой из координат первый цифро-аналоговый преобразователь (ЦАП) и усилитель постоянного тока (УПТ), подключенный к отклоняющей системе электроннолучевой трубки (ЭЛТ),блок управления, первый вход которого соединен с кодовой шиной данных, являющейся первым входом устройства и подключенной к первому входу блока синхронизации, второй вход блока управления подключен к кодовой шине адресов, являющейся вторым входом устройства 2,

Существенным недостатком этого усг

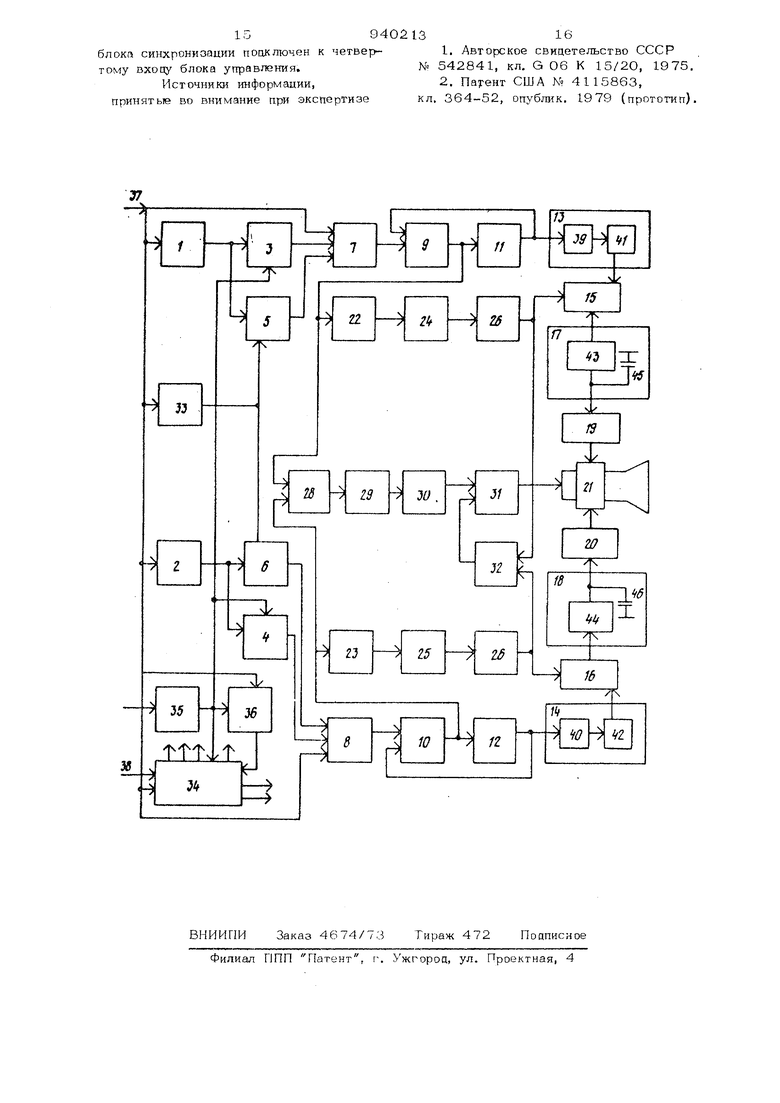

15 ройсгва является малая скорость отображения векторной графической информации, ограниченная быстродействием цифровых элементов, формирующих сигналы отклонения. При использовании для построения этого устройства, например, цифровых микросхем серии 155 и выборе частоты синхронизации, равной ВмГц, вектор максимальной длины на современной ЗЛТ, 394 имеющей элементов разрешения, отобргэжаегся за время -166 НС (Z°-l) --170 -340 МКС, . что снижает общий обьем отображаемой информации и не соответствует требовани ям, предьявляемым к современным рацио техническим информационным системам. Цель изобретеш1я - повышение быстро действия устройства. Поставленная цель достигается тем, что в устройство, содержащее по каждой из координат первые цифро-аналоговые преобразователи (ЦАП ) и усилитель постоянного тока (УПТ), подключенный к отклоняющей системе ЭЛТ, блок управления, первый вход которого соединен с кодовой шиной данных, являющейся первым входом устройства и подключенной к первому входу блока синхронизации, второй вход блока управления подключен к кодовой шине адресов, являющейся вторым входом устройства, введены по каждой из координат первые регистры, входы которы соединены с кодовой шиной данных, первые и вторые умножители, первые входы которых соединены с выходами первых регистров, вторые регистры, выходы которых подключены к входам первых ЦАП, коммутаторы по координатам X и У, первые входы которых соединены с кодовой шиной данных, вторые входы - с выходами первых умножителей, третьи входы -, с выходами вторых умтшжителей, вычислители, первые входы которых соединены с выходами Коммутаторов по кооршшатам X и У, вторые входы - с выходами вторых регистров, а выходы подключены к входам вторых регистров, последовательно соединенные между собой сумматор и блок памяти, выход которого подключен к входу УПТ, первые входы сумматоров со единены с вькодами первых ЦАП, а также последовательно соединенные интегратор, вторые ЦАП и третьи регистры, входы которых соединены с выходами вычислителей, выходы интеграторов - с вто рыми входами сумматоров, компаратор, выход которого подключен к модулятору ЭЛТ, первый коммутатор, входы которого соединены с соответствующими выходами вычислителей, четвертый регистр, вход которого соединен с выходом первого коммутатора, и третий ЦАП, вход которого соединен с выходом четвертого регистра, а выход соединен с первым входом компараторов, второй коммутатор, входы которого ггоцключены к соответствующим выходам интеграторов, а выход - к вто34рому входу компаратора, пятый регистр, вход которого соединен с кодовой шиной данных, Д выход - с вторым входом вторых умножителей, делитель частоты, вход которого является третьим входом устройства, а выход соеш-гнен с вторым входом блока синхронизации, с вторым входом первых умножителей и третьим входом блока управления, причем выход блока синхронизации подключен к четвертому входу блока управления. На чертеже представлэна структурная схема устройства отображения графической информации на экране электроннолучевой трубки. Устройство содержит по каждой из координат первые регистры 1,2, первые умножители 3, 4, вторые умножители 5, 6, коммутаторы 7, 8 по координатам X и У, вычислители 9, Ю, вторые регистры 11, 12, первые цифро-аналоговые преобразователи (ЦАП) 13, 14, сумматоры 15, 16, блоки 17, 18 памяти, усилители 19, 2О постоянного гока, ЭЛТ 21, третьи регистры 22, 23, вторые ЦАП 24, 25, интеграторы 26, 27, первый коммутатор 28, четвертый регистр 29, третий ЦАП 30, компаратор 3 1, второй коммутатор 32, пятый регистр 33, блок; 34 управления, делитель 35 частоты, блок 36 синхронизации, кодовую шину 37 данных и кодовую шину 38 адресов. Кодовая шина 37 данных предназначена для подачи информационных кодов, необходимых для отображения графической ш формации (командных слов, кодов Р Sivifb I наклона вектора, кода « длины вектора, кода К масштабного коэффициента для выбора необходимой скорости отображения первичной развертки, кодов начальной позиции X Q и УО ). Кодовая шина 38 адресов предназначена ДЛЯ подачи кодов адресов, определяющих конкретный приемник кодовой информации. Третий вход устройства предназначен для подачи синхросерии частот Го . При отображении векторов и линий развертки в каждый момент времени должно выполняться соотношение межс сигналами отклонения по ортогональным осям X и У -хо Y-YO Sihp COS 5 где X . Ур - координаты начальной точки вектора (линии развергки); 5f) X, У - кооршшагы текущей точки векгора (лишга развертки); р) - угол наклона относительно Учитыбая, что У ot-coS 3, где ftтекущая длина вектора (линия развертки) после дифференцирования получим . di at(2) Интегрируя его выражение, имеем Т iHp)J,-Hr-dt (3) Х-Хо Представляя полученный интеграл в виде суммы интегралов меньшей велич{ш получим выражение, математически опис вающее принцип используемого в устройстве цифро-аналогового отображения векторовХ- Хо - I (1И J К-о Аналогично ЪCK+1)AT-jL (COSP-J-Trdt)KM (5) .,-01У.ТOtКак видно из выражений (4) и (5), для отображения вектора (линий развертки) необходимо формировать по обеим осям цифровые ступенчатые функции (6) к-о Ьль X VotScosp-И.ЛТ ° ic-o (7) при ДоС , выбираемом равнык 2 элементов разрешения экрана, и сглалшвать их аналоговыми сигналами интеграторов . (и)лТ dl ,, t , --51ир,| КЛТ (8) (.К41)лТ, V-cosftJ -lkcit A L+ -г (э) дт Соответствующим выбором разрядностей цифровых функций и величин сглаживающих сигналов можно наилучшим об разом совместно реализовать противоречивые требования к быстродействию и точности формируемых сигналов отклонения по осям X и У. Для пратзвольной (с точки до элемен та разрешения экрана ЭЛТ) установки оливы вектора (линии развертки) его ра рядность должна быть равна N , так чтобы 2 У1 - числу элементов разрешения на экране. Эти N разрядов целят ся на В + А, пр{че т коц, заштсанный в 36 в старших разрядах, определяет число полных приращений цифровой ступенчягой функции (6), (7), а код, записанный в А младших разрядов, величину остаточного участка Л Р До: 2. Момент окончания написания вектора (линня развертки) определяется по мокюнту равенства, при отображении остаточного участка линии, сигналов интеграторов (8) , (9) с заоанее вычисленными уровнями АХп и дУд по каждой из координат В1И(Ъ(10) ДХ - Д(1 (11) где ДРо- число,- содержащее В А младших разрядов кода cL , Управление работой всего устройства осуществляется единым блоком 34 управления. Перед началом отображения очередного вектора (линии развертки) блок 3 управления производит дешифрацию кодов адресов, приходящих По LUIIHG 38, и в соответствии с этими кодами вьфобатывает импульсы записи, которыми записываются в соогветсгвутощие блоки устройства информационные коды, синхронно поступаквдке по шине 37 данных. Принимая с выхода делителя 35 частоты серию импульсов /( , блок 34 управления фop яIрует серию , задержанную относительно на полов шу периода. Эти серии хронизируют работу всех блоков устройства. Блок 34 управления фop пIpyeт сигналы, управляющие работой коммутаторов 7(8) по коорцинатам X и У, первого коммутатора 28, второго коммутатора 32, вычислителей 9( Ю), компаратора 31. По записанному в блок управления коду масштабного коэффициента К он производит выбор Постоянных времени интегрирования и форктруег сигнал, управляющий делитеJKM 35 частоты. Кроме того, блок 34 управления выполняет логическую операцию Исключающее ИЛИ для второ- го и третьего разрядов кода |5 , записываемых с кодовой шины 37. данных в его внутреннюю память. Эта операция позволяет определить ось, по которой сигнал отклонения для каждого угла J5 имеет большую величину, и выдать соответствующие управляющие сигналы на первый коммутатор 28 и второй коммутатор 32, Делитель 35 частоты произвоштт необходимое деление входной частоты f „ . При отображении векторов Koa}i({jimteHT деления равен едшпще. При огобрпжешти . 7,94 линий развертки частота f на выхоце делителя 35 частоты огтрецеляется управ- ляюишм сигналом, формируемым блоком 34 управления. Блок 36 синхронизации вычисляет в ре ме1шой интервал, в тече1ше которого фор мируются полные приращения цифровой ступенчатой функции. Блок36 синхронизации, по сути являющийся преобразователем код-время, может быть построен, например, на основе цифрового счетчика, в который через кодовую шину 37 данных заносится в обратном коде В старших разрядов кода длины вектора (линии развертки) об , дешифратора нулевого кода и триггера, запоминакадего выхош ой сигнал дешифратора. С.выхода делителя 35 частоты на второй вход блока 36 синхронизации подается пачка имтгульсов частоты . При этом блок 36 синхрониза ции выдает сигнал окончания временного интервала после прохождения числа импульсов , равного числу, записанному в В старших разрядах кода плюс 1. В первый регистр 1 по оси X и 2 по оси У записываются коды тригонометрических фун1щий 51 и 5 и cosp ,. которые хранятся там в течение всего времени отображения вектора или линии развертки. Первые умноисители 3 и 4 по калсдой из координат используется для вы шслени приращений л X и AY CC fbAci для цифровых ступенчатых функций {6} и (7). Вычисхение производится путем временного умножения пачки импульсов i, поступающей с делителя 35 частоты на вторые входы этих элементов, на коды и cosp I снимаемые с первых регистров 1 и 2 по каждой из координат. Умножители 3 и 4 могут быть реализова- ны, например, на основе интегратора с параллельным переносом. Вторые умно кители 5 и 6 по кансдой из координат являются умножителями типа код на Код. С их помощью вычисляются значеьшя ортогональных соптавляю- щих Л Xj и дУр остаточного участка линии, величина которого uR записана в А младших разрядах кода с{. . Коды sinp и Со5 Р подаются на первые входы вторых умножителей 5 и 6 по из координат, а А разрядов кода оС поступают на второй вход с выхода пятого регистра 33 который выполняет роль регистра памяти, получающего эту информацию с кодовой шины 37 данных. В соответствии с управляющими сигналами от блока 34 управления через коммутаторы 7 и 8 по координатам X и У по каждой из координат 38 производится пропускание либо кода Х и Ур начальной точки линии с кодовой шины 37 данньгх, либо кода ДХ и дУ с выхода первых ум1ожителей 3 и 4 по каждой из Координат, либо кода Хр и Л УК с выходов вторых умножителей 5 и 6 по каждой из коор.динат. Вычислители 9 и 1О (АЛУ) по каждой из Координат выполняют с/юдующие . арифметические и логические функции: 1)F 1) 2)F - С 3)F С +Б 4)F С -D 5)F О На первые входы вычислителей 9 и 10 поступают коды с выхода коммутаторсй 7 и 8. На вторые входы поступают коды с выхода вторых регистров II и 12. Выбор функции работы вычис/штелей 9 и 1О осуществляется блоком 34 управле-. Ыя. Вычислители 9 и 10 по каждой из координат, выполняюише перечиследа1ые функции, могут быть реализованы, например, на основе микросхем АЛУ типа 155ИПЗ, количество которых выбирается в соответствии с требуемой разрядностью, и схемами ускоренного переноса 155ИП4. Первью цифро-аналоговые преобразователи 13 и 15 на каждой из координат преобразуют цифровой код функций (6) и (7) в аналоговый сигнал соответствующей величины. Они содержат внутненние avreMeHTU памяти (дополнительные регистры) 39 и 4О и преобразователи 41 и 42 код-ток по каждой из кооршшат. Аналоговый сигнал, сглаживающий цифровую ступенчатую функцию, формируется в соответствии с выражениями (8) и (9) после довательно соединенной цепочкой э/юментов по каждой из координат: третьи регистры 22(23) - вторые ЦАП 24 (25) - штеграторы 26(27). Перец началом очередного периода к йТ сглажива шя цифрс&ой функции в третьи регистры 22 и 23 по каждой из координат загшсьтается код подынтегральной величшгы ЛХ и ЛУ Вторые ЦАП 24 и 25 преобразуют этот код в аналоговый сигнал нужной полярности, определяемый кодом знака соответствующей тригонометрической функшш (т.е. ориентацией линии), поступающий от блока 34 управления, куда он записан с кодовой шины 37 данных. Интеграторы 26 и 27 по каждой из коор994оинаг формируют сигна; описываемый выражениями (8) и (9). Сумматорами 15 и 16 т каждой из координат осуществляется суммирование сигналов с выходов первых ЦАП 13 и 14 и выходных сигналов интеграгорш 26 и 27. Сумматоры 15 и 16 могут быть реалнзсжаны, например, путем подключения токового выхода интеграторов 26 и 27 к точке суммирования (с малым входным сопротивлением) разрядных токов первых ЦАП 13 и 14. На выходе сумматоров 15 и 16 формируется пилообовзный сигнал, описываемый выражениями (4) и (5) : Для исключения влияния выгбросов в Пйлообракюм сигнале, возникающих по каждой из координат в моменты обнулени интеграторов 26 (27) и изменения кода в дополнительном регистре 39(4О) ЦАП 13(.14), в устройстве применяются блоки 17( 18) памяти. Они состоят из ключевого элемента 43(44) к аналогового запоминающего элемента 45(46), например конденсатора. На время выброса и следующего за. ним переходного процесса в первых ЦАП 13 и 14 и интеграторах 26 и 27 ключевые элементы 43 и 44 размыкаются сиг налом от блока 34 управления, при этом на аналоговых запоминатсщих элементах 45 и 46 запоминаются уровни напряжения до начала выброса. Усилители 19 и 20 постоянного тока усиливают сигнал с выхода блоков 17 и IS памяти до величины, достаточной для подачи в отклоняющую систему ЭЛТ 2 I, которая осуществляет отклонение луча в любую точку экрана. Первый ко ммутатор 28 предназначен для пропускания в цепь управления выключения подсвета, состоящую из четвертого регистра 29, третьего ЦАП 30 и компаратора 31, кода ортогональной составляЕЮщей остаточного участка uR кода длины линии ot, имеющего большую величину ( йХ или ЛУ ), Управление пропусканием зависит от угла наклона линии Ь и осуществляется блоком 34 управления описанным выше способом. Аналогичным образом управляется и второй коммутатор 32, который пропускает сигнал интегратора 26 гош 27 по одной из координат с большей величинойотклшения. Коды ДХд или бУр с первого коммутатора 26 записываются В четвертый регистр 29 ив TpeibRM ЦАП 30 преобразуются с учетом знака Bivi Р) ( СО5р ) в аналоговый сигнал соот ветствующей поляр{1ости. Компаратор 3 1 в нужный интервал времени производит Сравнение сигналов с выхода третьего ЦАП 30 и второго коммутатора 32. При равенстве уровней в этом интервале времени компаратором 3 1 выключается подсвет ЭЛТ. Устройство отображения графической информации работает следующим образом. Перед началом отображения вектора в устройство по кодовой щине 37 данных поступают коды, в соответствии с адресами, синхргашо приходящими по кодовой щине 38 адресов записываются в слеодтсяцие блоки и элементы: код начального положения Хд - во второй регистр 11 и в дшолнительный регистр 39первого ЦАП 13 по оси X; код начального положения YO - о второй регистр 12 и в дополнительный регистр 40первого ЦАП 14 по оси У{ код Sinp - в первый регистр 1 по оси X; код cos (Ъ - во второй регистр 2 по оси Ч ; код длины вектора Ы|- старшие В разрядов - в бтж 36 синхронизашга, младшие А разрядов - в пятый регистр 33;код масштабного коэффициента - в блок 34 управлеш155 второй и третий разряды кода угла р) - в блок 34 уп равления; коды знаков SlHP) и Cosp блок 34 управления. Прн записи когдов Хд, 3 блок 34 управления обеспечивает их протсснсдение путем подключения к выходу коммутатора 7 и 8 его первого входа и установки в вычислителях 9 и Ю 45Т1ИШИ F О. После момента i записи этих кодов к выходу коммутаторов 7 и 8 подключается его третий вход. При этом на вы ходе вычислителей Р и 10 по координатам X и У к моменту начала напи- сания вектора должны появиться вычисленные во вторых умножителях 5 я 6 код йХд и Л Уд . Больший из этих кодов через первый коммутатор 28 поступает на вход четвертого регистра 29.. Импульс начала линии (ИНЛ), который может вырабатываться как блоком 34 управ;юнкя, так и пргходить извне, записывает этот код в четвертый регистр 29 к включает делитель 35 частоты. В случае отображения векгора вторичной информации выходная частота делителя равна входной - fо Хронизация работы устройства произ«водится двумя сериями f j и равной частоты и сдвинутыми в блоке 34 управления друг относительно друга на половину периода ЛТ. Серия { определяет моменты вычисления первыми умножите1-19 3 и 4 и прир.1шений &Х иЛУ цифровой сгуттснчагой функции (в) и (7), загагси во вторых регистрах II и 1-2 значений этой функции, управляет блоком 36 синхронизации. Серия $2 управляет загшсью коца приращений лХ и Д У в тре тьи регистры 22 и 23, зпписью кодов щгфровой ступенчатой функции (6) и (7) во внутреннее дополни тельных регистрах 39 и 40 первых цифро-аналоговых прообразователей 13 и 14, работой интегI aTopoB 26 и 27 и блоков 17 и 18 памяти. После появления импульса начала линии блок 34 управления включает коммутаторы 7 и 8 в режим пропускания ко- дов с выхода первых умножителей 3 и 4 Им же прс 1звоаится перезапись во вторы регт{стры 11 и 12 кода Х и Уд при вы полнении вьгчислителями 9 и 10 функции , После эАЛУ 9 и 10 усганавливаетс . В момент -L первый импуль серии 2 ощшвреметш переписывает во внутренние дополнительные регистры 39 и 4О первых ЦАП 13 и 14 кодьт значения цифровой функции (б) и (7) и в третьи регистры 22 и 23 - коды оргогонаЛ1)Ных ДХ и Д У полных приражений Aoi Этим же импульсом размыкаются ключевые элементы 43 и 44 блоков 17 и 18 памяти. По заднему фронту ил нульса замыкаются ключевые эпвмег1ты 43 и 44, включаются интеграторы 26 и 27 и начинается формирование пилообразного сигнала (8) и (9) по каждой из координат с амплитудой, равной приращению miфровой ступенчатой функщш (6) и (7). Во время формирования пилообразного сигнала вычислители 9 и Ю вычисляют следутощий код цифровой ступенчатой функ ции (6) и (7) F С ± D , который ВТОрым импульсом серии f записывается во вторые регистры 11 и 12 и, вслед за этим, npotiycKaeT вычиспенныт первыми умножителями 3 и 4. при поступлении того, же импульса f код йХ и &У слеоующего приращения цифровой ступенчатой функции (6) и (7). Передним фронтом второго импульса серии обнуляются ингеграторы 26 и 27, размыкаются ключи 43 и 44 блоков 17 и 18 памяти в дополнительные регистры 39 и 40 первых ЦАП 13 и 14 заносигся новый код цифровой ступенчатой функции (6) и (7), а в третьи реггГстры 22 и 23 - коа нового прирашения &Х и ДУ. После окончании этого импульса начинается фop 4цpoвaниe нового пилообразного сигнала относительно jiOBoro уровня цифровой функции. Далее формирование rto1312лных .гфирашего5й цифровой ступенчатой функции и сглаживания ее сигналом интегратора происходит аналогично. Блок 36 синхронизации считает импульсы серии f и после прохождения их числа, равного (в + 1) (где в - число, aam-rcafmoe в В старших разрядах кода oL), выдает на блок управления соответствующий логический сигнал (момент -i ). При нулевом числе, содержащемся в В старших разрядах кода, режим воспроизведения остаточного участка устанавливается сразу же. В интервал времени 5- t, при формировании последнего из полных пилообразных сигналов через вычислители 9 и 10 (режим F О) на входы третьих регистров 22 и 23 поступает код слео ющего полного приращения по каждой из координат. После записи этого коца и начала формироваштя пилообразного сигнала по Каждой из координат (момент t) блок 34 управления включает компаратор 31, который определяет момент павенствн большего пилообразного сигнала, проходящего через третий коммутатор 32, и уровня, равного ЛХ, и,ли . В момент равенства этих сигналов ( - ) компаратором 3 1 выключается подсвет электроннолучевой трубки. В интервале времени -L g вычис.пители 9 и 1О выполняют функции; F С. Таким образом, следующий импульс серии €( момент tg ) перезаписьюает во вторые регистры 11 и 12 ранее находившийся там код. В интервале времени ig-Ь вычислители 9 и Ю выполняют функцию F О, гак что импульс серии f(момент feg ) записывает в третьи регистры 22 и 23 по каждой из координат нулевой код. Однов земенно этим же импульсом, как и ранее, обнуляются интеграторы 26 и 27 и размыкаются на время переходных процессов ключевые элементы 43 и 44 блоков 17 и 18 памяти по каждой из координат, После момента времени t вычислители 9 и 10 выполняют функцию F ,С +1), причем на первый вход через коммутаторы 7 и 8по каждой из координат подается код йХр) и ДУя с выхода вторых умножителей 5 и 6, На выходе вычисл1ттелей 9и Ю формируется код, соответствующий конечной точке отображения вектора, который импульсом в момент 4;-,, записывается во вторые рептстры 11 и 12, а в момент b-t- - в дополнительные регистры 39 и 4О первых ЦАП 13 и 14. При этом луч ЭЛТ кодом устанавливается в конечную точку отображенниго 136 вектора и блоком 34 управления включается подсвет трубки. Пос;кЦНИИ импульс серии f выцеляегся блоком 34 управления как импульс конца линии и может быть использован для установки в исходное состояние всех элементов устройства и выдачи на любые внешние вычислительные и управляющие блоки. Работа устройства при отображении линий развертки аналогична работе при отображении векторов вторично: информации с тем лишь отличием, что в соответствии с масштабирующим коэффициентом К изменяется частота импульсов на выходе делителя 35 частоты и устана вливаются другие постоянные времени ин теграторов 26 и 27 по каждой из коор танат. Таким образом, использование прецлагаемого устройства позволит отображать на экране ЭЛТ векторы вторичной инфор мадии с большей скоростью,что в сочетании с сохранением возможности воспро изведения линий первичной развертки в этой же структуре удовлетворяет требова ниям, предъявляемым к устройствам отображения информации радиотехнических информационных систем. , при условии, что современные ЭЛТ обеспечивают элементов разрешения на диаметр трубки, код длины вектора должен выражаться 11-разрядным Кодом. Если из них, например, разрядов испотьзовать как старшие и по ним формировать цифровую ступенчатую фушщию (6) и (7), а 4 разряда использовать как младшие и по ним формировать пилообраз ные сглаживающие сигналы (максимальной величины 2 16 элементам разрешения экрана ЭЛТ), то время отображени вектора максимальной длины (cL .lllllllllll) составит при f l,5 мГц т« - пе gOfAKt -f,5 -10 « Формула изобретения Устройство для отображения графической информации на экране электроннолучевой трубки, содержащее по каждой из координат первые цифро-аналоговью прео разователи и усилиг1&ль ПОСТОЯННОГО) тока подключенный к отклоняющей системе : 314 электроннолучевой трубки, блок управления, первый вход которого соединен с кодовой шиной данных, являющейся первым входом устройства и подключенной к первому входу блока синхронизации, второй вход блока управления подключен к кодовой шине адресов, явл5пощейся вторым входом устройства, отличаю- щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены по каждой из координат первые реги:;тры, входы которых соединены с кодовой шиной данных, первые и вторые умножители, первые входы которых соединены с выходами nepBbtx регистров, вторые регистры, выходы которых подключены к входам первых цифр.о-аналоговых преобразователей, коммутаторы по коорцинатам X и У, первые вход1 1 которых с кодошой шиной данных, вторые входы - с выходами первых умножителе, третьи входы - с выходом вторых умножите юй, вычислители, первые входы которых соединены с выходами коммутаторов по координатам X и У, вторые входы - с выходами вторых реп стров, а выходы подключены к входам вторых регистров, послецовательно.сое- днне1шые сзгмматор к блок памяти, выход которого подключен к вховдг усилитеЛя ПОСТОЯННОГО тока, первые вхоцы сумматоров соединены с выходами первых цнфро-аналоговых преобразователей, а также последовательно соединенные интегратор, вторые цифро-аналоговые преобразователи и третьи регистры, входы которых соешгаены с выходами вычислителей, выходы интеграторов соединены с вторыми входами сумматоров, компаратор, выход которого подключен к модулятору электрсжнолучевой трубки, первый коммутатор, вхоцы которого соединены с соответствующими выхоцамн вычислителей, чегвергый регистр, вход которого соецннен с выходом первого коммутатора, и третий цифро-аналоговый преобразователь, вход которого соединен с выходом четвертого регистра, а выход соединен с первым компаратора, второй коммутатор, входы которого поцключены к соогветствутошим выходам интеграторов, а выход - к второму входу компаратора, пятый регистр, вход которого соеоинен с кодовой шиной данных, а выход - с вторым входом вторых умножителей, делитель частоты, вход которого является третьим входом устройства, а выкод соединен с вторым входом блока синхронизации, с вторым входом первых умножителей и третьим входом блока управления, причем выход

1594021316

бпокл синхронизации пооключен к четвер-1. Авторское свицетельсгво СССР

тому входу блока управления.N 542841, кл, G Об К 15/20, 1975,

Источники информации,2. Пауент США К 4115863,

принятые во внимание при экспертизекл. 364-52, опублик, 1979 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графи-чЕСКОй иНфОРМАции HA эКРАНЕ элЕКТРО-HHO-лучЕВОй ТРубКи | 1979 |

|

SU834739A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1985 |

|

SU1316027A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300542A1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| Устройство для формирования векторов на экране электронно-лучевой трубки | 1985 |

|

SU1251161A1 |

| Устройство для формирования векторов на экране электронно-лучевой трубки | 1984 |

|

SU1173436A1 |

| Устройство для отображения информации | 1984 |

|

SU1495731A1 |

| ИМИТАТОР ПАССИВНОГО РАДИОЛОКАТОРА | 1988 |

|

SU1841093A2 |

| Устройство для формирования вектора на экране электронно-лучевой трубки | 1982 |

|

SU1016816A2 |

| Устройство для отображения графической информации на экране цветного телевизионного индикатора | 1990 |

|

SU1836719A3 |

Авторы

Даты

1982-06-30—Публикация

1980-12-30—Подача