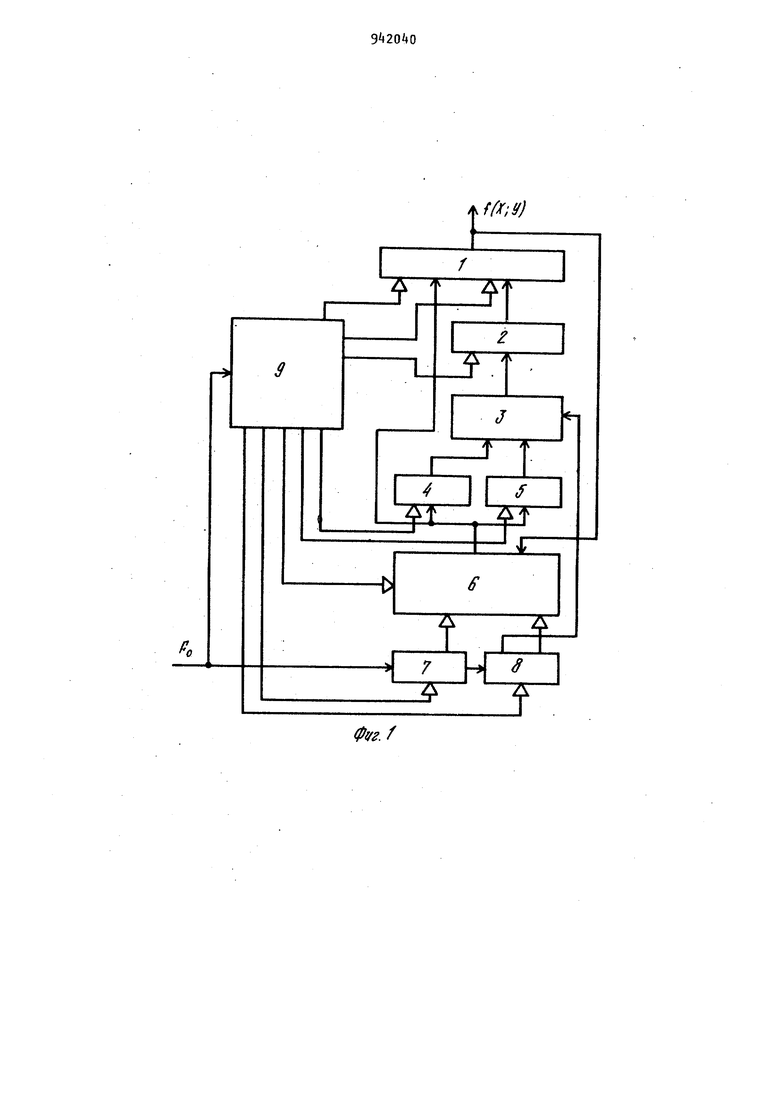

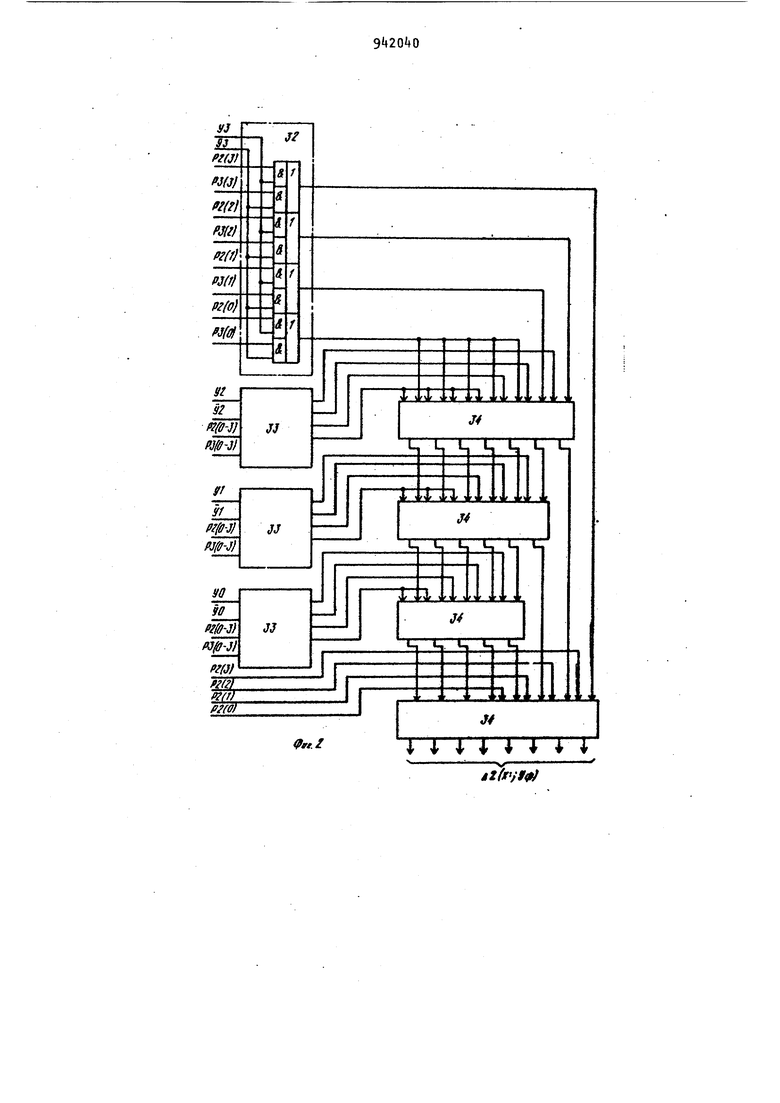

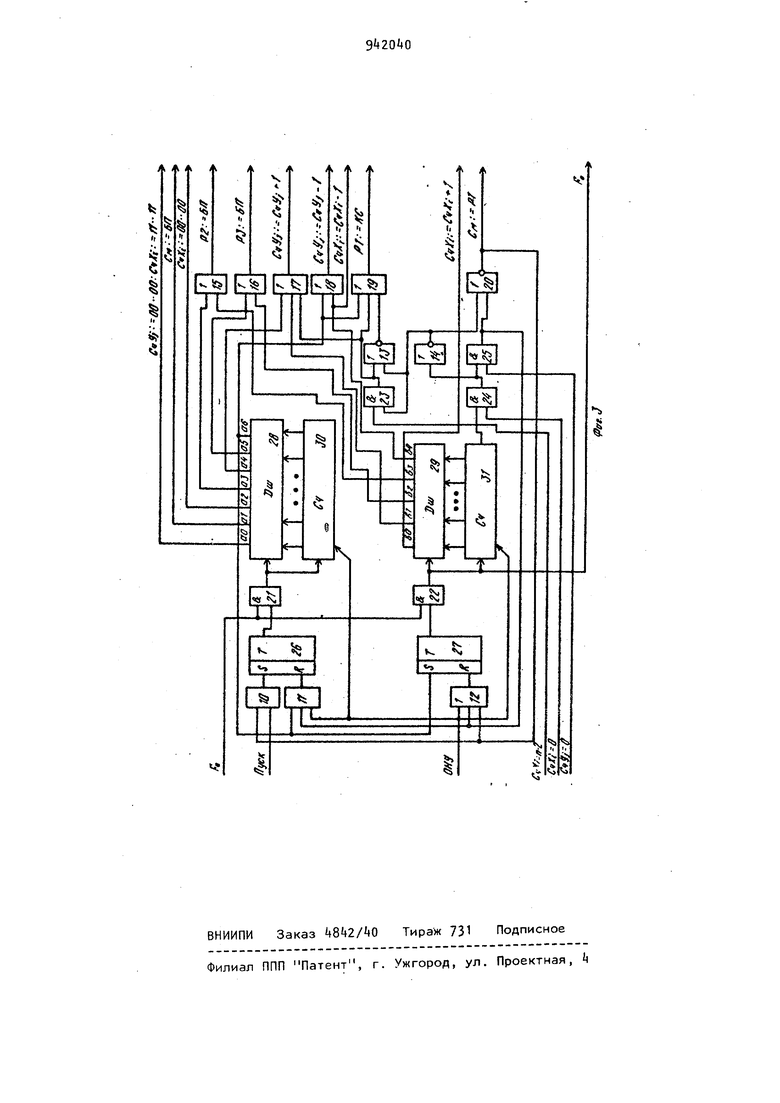

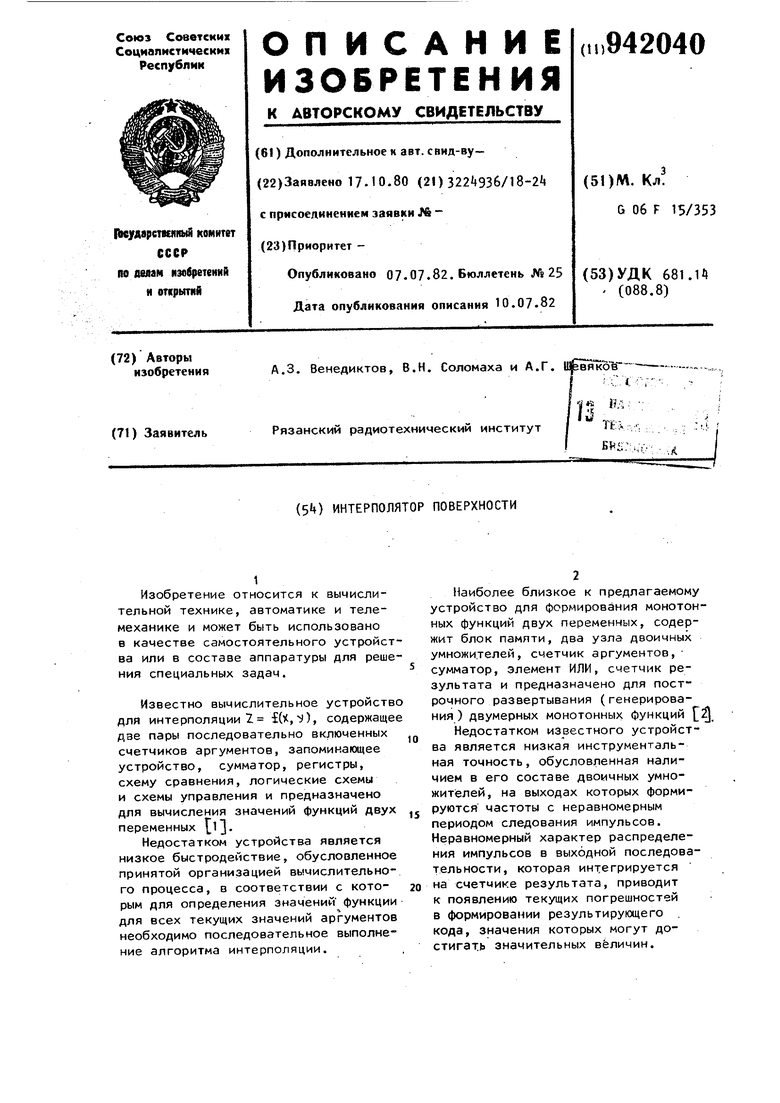

Изобретение относится к вычислительной технике, автоматике и телемеханике и может быть использовано в качестве самостоятельного устройст ва или в составе аппаратуры для реше ния специальных задач. Известно вычислительное устройств для интерполяции 1 Ш,:)), содержаще две пары последовательно включенных счетчиков аргументов, запоминающее устройство, сумматор, регистры, схему сравнения, логические схемы и схемы управления и предназначено для вычисления значений функций двух переменных 0Недостатком устройства является низкое быстродействие, обусловленное принятой организацией вычислительного процесса, в соответствии с которым для определения значений функции для всех текущих значений аргументов необходимо последовательное выполнение алгоритма интерполяции. Наиболее близкое к предлагаемому устройство для формирования монотонных функций двух переменных, содержит блок памлти, два узла двоичных умножителей, счетчик аргументов,сумматор, элемент ИЛИ, счетчик результата и предназначено для построчного развертывания (генерирования ) двумерных монотонных функций f Недостатком известного устройства является низкая инструментальная точность, обусловленная наличием в его составе двоичных умножителей, на выходах которых формируются частоты с неравномерным периодом следования импульсов. Неравномерный характер распределения импульсов в выходной последовательности, которая интегрируется на счетчике результата, приводит к появлению текущих погрешностей в формировании результирующего кода, значения которых могут достигать значительных величин. Цель изобретения - увеличение томности. Указанная цель достигается тем, что в интерполятор поверхности, содержащий блок памяти, адресные входы которого соединены с первыми выходами первого и второго счетчиков, сумматор, введены первый, второй и третий регистры, блок суммирования и блок управления, причем второй выход первого счетчика подклю чен к входу второго счетчика, второй выход которого соединен с первым входом блока суммирования, второй и третий входы которого подключены соответственно к выходам первого и второго регистров, входы которых соединены с информационным выходом блока памяти и с первым входом сумматора , второй вход которого подключен к выходу третьего регистра, вход которого соединен с выходом блока суммирования, выход сумматора соединен с информационным входом блока памяти и является выходом интерполятора,а вход интерполятора соединен с первым входом первого сметчика и с входом блока управления, первый и второй выходы которого подключены соответственно к управляющим входам первого и второго счетчиков, Огретийк управлякхцему входу блока памяти, четвертый, пятый и шестой - к управляющим входам первого, второго и тре тьего регистров, а седьмой и восьмой выходы блока управления подключены к управляющим входам сумматора. Блок управления содержит первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы ИЛИ, первый и второй триггеры, первый и второй, третий, четвертый и пятый элементы И,, первый и второй дешифрат ры, первый и второй счетчики, причем первые входы первого, второго и третьего элементов ИЛИ и первого, второ го, третьего, четвертого и пятого элементов И соединены с установочными входами первого и второго счетчиков и являются входом блока, вторые входы первого и третьего элементов ИЛИ подключены к выходу четвертого элемента ИЛИ и к седьмому выходу бло ка, выход пятого элемента И соединен с вторым входом второго элемента ИЛИ с третьим входом третьего элемента ИЛИ и с первым входом четвертого эле мента ИЛИ, второй вход которого подключен к выходу пятого элемента ИЛИ; к второму входу третьего элемента И и к первому входу шестого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и с первыми входами седьмого и восьмого элементов ИЛИ, второй вход последнего подключен к выходу шестого элемента ИЛИ, третий вход восьмого элемента ИЛИ подключен к первому выходу первого дешифратора, к первому входу девятого элемента ИЛИ, к третьему входу второго элемента ИЛИ и к первому установочному входу первого три1- гера, второй установочный вход которого подключен к выходу третьего элемента ИЛИ, а выход - к второму входу второго элемента И, выход которого соединен с управляющими входами второго дешифратора и второго счет-i чика и подключен к восьмому выходу блока, выход восьмого элемента ИЛИ подключен к шестому выходу блока, выход первого элемента ИЛИ соединен с первым установочным выходом первого триггера, второй установочный вход которого подключен к выходу второго элемента ИЛИ, а выход - к второму входу первого элемента И, выход которого соединен с управляющими входами первого дешифратора и первого счетчика, выходы которого подключены к входам первого дешифратора , второй выход которого подключен к третьему выходу блока, третий выход первого дешифратора соединен с первым входом десятого элемента ИЛИ, второй вход которого соединен с первым выходом второго дешифратора, а выход подключен к четвертому выходу блока, четвертый выход первого дешифратора подключен к второму входу седьмого элемента ИЛИ, третий вход которого соединен с вторым выходом второго дешифратора, а выход седьмого элемента ИЛИ подключен к второму выходу блока, пятый выход первого дешифратора подключен к первому входу одиннадцатого элемента ИЛИ, второй вход которого соединен с третьим выходом второго дешифратора, а выход подключен к пятому выходу блока, шестой выход первого дешифратора подключен к второму выходу блока, седьмой выход первого дешифратора подключен к первому выходу блока, четвертый выход второго дешифратора подключен к первому выходу блока, а пятый к первому выходу блока и к второму входу девятого элемента ИЛИ, выход которого подключен к второму выходу блока, входы второго дешифратора соединены с информационными выходами второго счетчика, выход перено са которого соединен с вторым входом четвертого элемента И, выход которого подключен к второму входу пятого элемента И и к входу пято го элемента ИЛИ. На фиг.1 представлена схема интерполятора поверхности; на фиг.2схема блока суммирования, вариант; на фиг.З - схема блока управления устройства. Интерполятор поверхности содержит сумматор 1, регистр 2, блок 3 суммирования, регистры t и 5,блок 6 памяти (БП), счетчики 7 и 8 аргументов, блок 9 управления Блок 9 состоит из элементов ИЛИ 10-20, элементов И 21-25, триггеров 26 и 27 дешифраторов 28 и 29, счет чиков 30 и 31. Блок 3 включает группы 32 и 33, элементов И-ИЛИ, представляющие соб коммутаторы (Kl-K), комбинационные сумматоры З (.КСМХ Интерполятор осуществляет кусочно-линейную интерполяцию поверхнос ти {(Х,)в соответствии с выражениями U,)) V7,-.j ;i-PU),4,.). z,, i:A-PU)-z, PW; f (V-i,Vjh ординаты функции лах интерполяции N -N iM 1 Задача построчного развертыван поверхности сводится к формиро нию одномерных функций путем инте ВаНИЯ их первых ПрОИЗВОДНЫХ ТаК, любой фиксированной строки имеем €(x,y)--fUo.VQ.),)d 6 где {(Хо, Уф)- значение функции в начале строки. В свою очередь, {(Хо,ф; может быть найдено также путем интегрирования в дискретном времени -Ьф вдоль границы функции по оси У при Uo,0)--(Xo.Vo),v)dv (3 где f(Vo,o) значение i(X,V в начале координат (. При КЛА значение производной в течение времени развертывания функции внутри ij -го интервала разбиения остается постоянным. Это обстоятельство учитывается при реализации (2 на цифровом функциональном генераторе (ЦФГ , который на каждом С-1-1 ом интервале аппроксимации по X обеспечивает интегрирование приращения линейную развертку и вычисление приращения для следующего интервала в соответствии с выражением, полученным из (.1) с учетом (2) )--д1 -|:-1-РС 1..,), .) Чоигг, . -7 . ri-b-IJ-H 0-Vij ,)По аналогии с () может быть получено выражение для вычисления значения {CX,V и начале К-ой строки, принадлек ащей j -ому интервалу разбиения по У. Управление работой ЦФГ осуществ-ляется блоком 9 управления. Предварительно в сумматор 1 интерполятора блока 6 передается начальное значение {(Хо,%). Для этого блок 9 выставляет на СЧХ7 и СЧХ8 адрес ячейки памяти, в которой хранится значение i(yo,Vo)- Перед началом развертывания СЧХ7 и СЧХВ обнуляются. П процессе построчного развер ывания{{х,) 5П 6 в соответствии с пара.,. v. %,-.о., аилиоыыа Л7- j выдает значения Д ми Х4н, и uZ,.. -i)+-i которые фиксируются в регистрах ч и 5. Блок 3 предназначен для вычисления приращения .Уф). .

Если выражение ( 4) записать в виД1и.1ф)(иф)д. ,.,,ДP(V&лI tPCVф)oк

l 1;jvДPWф)., (Г)

где ОК - обратный код;

ДК - дополнительный код ПК - п рямой код,

то блок 3 может быть организован на основе лестничной структуры из комбинационных сумматоров кем, на входы которых в соответствии со значениями разрядов Р { У) и УО-УЗ с помощью коммутаторов.К1-КА (элементы И-ИЛН ) подаются либо коды (р2). либо )(P)-TaK как значения хранятся в БПб в дополнительных кодах, то в соответствии с алгоритмом умножения в ДК введены дополнительные разряды. КСМЗ обеспечивают суммирование с величиной Д2-jj- 2.Результат ( приращение ) также формируется в ДК, что обеспечивает возможность генерирования любых функций.

В момент начала f -го интервала аппроксимации uZ.(,V0) пере/ ется в регистр 2 интерполятора. Интерполятор на этом интервале аппроксимации, обеспечивает линейную развертку функции (X,v) с наклоном путем интегрирования приращения на сумматоре 1 с опорной частотой.

Вычисление начальных значений (XO.VK) осуществляется в процессе перехода к началу развертки следующей строки. Для этого содержимое ячейки блока 6 с текущим значением {(Xo,V)(.) передается в СМ1 , далее из блока 6 считывается значение fik 2. -И суммируется с содержимым сумматора. В результате в СМ1 формируется величина f{Yo,(.), которая затем записывается в ячейку блока Ь с текущим значением

iCXo.V-i)В предлагаемом устройстве по сранению с известными за счет перехода к интегрированию приращений на накапливающем сумматоре и оперирования с параметрами функции, представленными в дополнительном коде, в два-три раза уменьшена инструментальная погрешность и существенно

расширен класс воспроизводимых зависимостей. Единственным ограниченим которое к тому же может быть учтено при масштабировании, является

генерирование функций с первыми производными по X и У, не превышающими 1 .

Изобретение может найти применение при построении различного рода автоматизированных систем, управления и контроля для формирования управляющих и корректирующих функций, в частности для коррекции телевизионного растра оптико-телевизионных датчиков, а также в составе спецвычислителей для вычисления нелинейных функций.

Формула изобретения

1. Интерполятор поверхности, содержащий блок памяти, адресные входы которого соединены с первыми

вых.одами первого и второго счетчиков, сумматор, отличающийс я тем, что, с целью увеличения точности, в него введены первый, второй и третий регистры, блок суммирования и блок управления, причем второй выход первого счетчика подключен к входу второго счетчика, второй выход которого соединен с первым входом блока суммирования, вто.рой и третий входы которого подключены соответственно к выходам первого и второго регистров, входы которых соединены с информационным выходом блока памяти и с первым входом сумматора, второй вход которого подключен к выходу третьего регистра, вход которого соединен с выходом блока суммирования, выход сумматора соединен с информационным входом блока памяти и является выходом интерполятора, а вход интерполятора соединен с первым входом первого счетчика и с входом блока управления, первый и второй выходы которого подключены соответственно к управляющим входам первого и второго счетчиков, третий - к управляющему входу блока памяти, четвертый, пятый и шестой - к управляющим входам первого, второго И третьего регистров, а седьмой и восьмой выходы блока управления подключены к управляющим входам сумматора. 2. Интерполятор по пЛ , от-, личающийся тем, что блок управления содержит первый, второГ1 третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы ИЛИ, первый и второй триггеры, первый, второй, третий, четвертый и пятый элементы И, первый и второй дешифр торы, первый и второй счетчики, причем первые входы первого, второ го и третьего элементов ИЛИ и перв го, второго, третьего, четвертого и пятого элементов И соединены с установочными входами первого и второго счетчиков и являются входо блока, вторые входы первого и .третьего элементов ИЛИ подключены к выходу четвертого элемента ИЛИ и к седьмому выходу блока} выход пятого элемента И соединен с вторым входом второго элемента ИЛИ, с третьим входом третьего элемента ИЛИ и с первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу пятого элемента ИЛИ, к второму входу третьего элемента И и к первому входу шестого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и с первыми входами седьмого и восьмого элементов ИЛИ, второй вход последнего подключен к выходу шестого элемента ИЛИ, третий вход восьмого элемента ИЛИ подключен к первому выходу первого дешифратора, к первому входу девятого элемента ИЛИ, к третьему входу второго элемента ИЛИ и к первому установочному входу первого триггера, второй установочный вход которого подключен к выходу третьего элемента ИЛИ, а выход - к второму входу вто рого элемента И, выход которого соединен с управляющими входами вт рого дешифратора и второго счетчика и подключен к восьмому выходу блока, выход восьмого элемента ИЛИ подключен к шестому выходу блока, выход первого элемента ИЛИ соединен с первым установочным выходом первого триггера, второй уст O10 новочный вход которого подключен выходу второго элемента ИЛИ, а вы- . ход - к второму входу первого элемента И, выход которого соединен с управляющими входами первого дешифратора и первого счетчика, выходы котос управляющими входами первого дешифратора и первого счетчика, выходы которого подключены к входам перпервого дешифратора, второй выход которого подключен к третьему выходу блока, третий выход первого дешифратора соединен с первым входом десятого элемента ИЛИ, второй вход которого соединен с первым выходом второго дешифратора, а выход подключен к четвертому выходу блока, четвертый выход первого дешифратора подключен к второму входу седьмого элемента ИЛИ, третий вход которого соединен с вторым выходом второго дешифратора, а выход седьмого элемента ИЛИ подключен к второму выходу блока, пятый выход первого дешифратора подключен к первому входу одиннадцатого элемента ИЛИ, второй вход которого соединен с третьим выходом второго дешифратора, а выход подключен к пятому выходу блока, шестой выход первого дешифратора подключен к второму выходублока, седьмой выход первого дешифратора подключен к первому выходу блока, четвертый выход второго дешифратора подключен к первому выходу блока, а пятый выход подключен к первому выходу блока и к второму входу девятого элемента ИЛИ, выход которого подключен к второму выходу блока, входы второго дешифратора соединены с информационными выходами второго счетчика, выход переноса которого соедин1ен с вторым входом четвертого элемента И, выход которого подключен к второму входу пятого элемента И и к входу пятого элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № , кл. G А, 1975, 2.Авторское свидетельство СССР по заявке К 2560381/18-2«, кл.й 06 F 1/02, 1977.

ffx-.y)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения полиномов | 1980 |

|

SU930321A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2173877C2 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2165099C2 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

0lf.f

Фм.1

Ф Ф Ф 4 Ф

Тй-у W

Авторы

Даты

1982-07-07—Публикация

1980-10-17—Подача