Изобретение относится к автоматике и вычислительной технике и может быть использовано либо в качестве автономного устройства для развертывания цифровых функций времени, либо в составе специализированных автоматических управляющих и вычислительных систем. Известно устройство для вычисления в цифровой форме значений поли-номиальных функций fl. Характерным для него является циклический процесс вычисления результата, основанный на использовании арифметического устройства последовательно выполняющего необходимые операции Это приводит к тому, что значение полинома определяется через достаточно большой промежуток времени. Отмеченное обстоятельство затрудняет использование такого устройства для воспроизведения цифровых полиномиальных функций времени, где их значение необходимо вычислять с приходом каждого -импульса число-импульсного аргумента Таким образом, недостатком является низкое быстродействие при воспроизведении функций времени . Наиболее близким к предлагаемому является устройство для вычисления полиномов, содержащее регистр, накапливающие сумматоры, схему сравнения. Устройство позволяет воспроизводить полиномиальнь1е функции числоимпульсного аргумента 2. Однако его недостатком является низкое быстродействие,обусловленное получением результата за два такта и сложность за счет большого количества накапливающих сумматоров, которая возрастает с увеличением cteneни полинома. Цель изобретения - упрощение устройства и повышение его быстродейст-Указанная цель достигается тем, что в устройство для воспроизведения полиномов, содержащее регистр, первый и второй накапливающие сумматоры, схему сравнения, введены два блоКЗ памяти, блок управления, суммирующий и вычитающий счетчики, причем, входы начальных значений накапливающих сумматоров соединены с выходом первого блока памяти, первый вход ко- to торого является входом полиномиальных коэффициентов устройства, второй вход - входом записи устройства, адресный вход блока памяти подключен к выходу суммирующего счетчика и перво- ,5

му входу схемы сравнения, второй вход которой соединен с выходом вычитающего счетчика и адресным входом второго блока памяти, выход которого подключен к входу перврго накапливающего сумматора, а вход - к выходу первого накапливающего сумматора и входу регистра, выход которого соединен с входом вгторого накапливающего сумматора, а первый вход бло ка управления подключен к выходу переполнения суммирующего счетчика, второй - к выходу схемы сравнения, третий - к входу опорной частоты уст ройства, четвертый - к входу запуска устройства, пятый - к входу крда сте пени п полинома устройства, а первый выход блока управления соединен с вхо дом установки в О регистра, входом установки начального значения п вычитающего счетчика, счетным входом суммирующего счетчика, второй выход - с входом чтения первого и второго блоков памяти, третий - с входом установки начального значения первого накапливающего сумматора, четвертый - с импульсным входом первого накапливающего сумматора, пятый - с вхо дом записи второго блока памяти, шестой - с счетным входом вычитающего счетчика, седьмой - с входом записи регистра, восьмой - с импульсным входом второго накапливающего сумматора, выход которого является выходом устройства, а также тем, что блок управления содержит пять триггеров, дешифратор, делите/ть частоты, схему сравнения, элемент задержки, три счетчика, шесть элементов И и три элемента ИЛИ, причем, счетный вход первого триггера подключен к счетному входу второго триггера и к выходу первого элемента ИЛИ, первый вход которого соединен с первым входом второго эле93

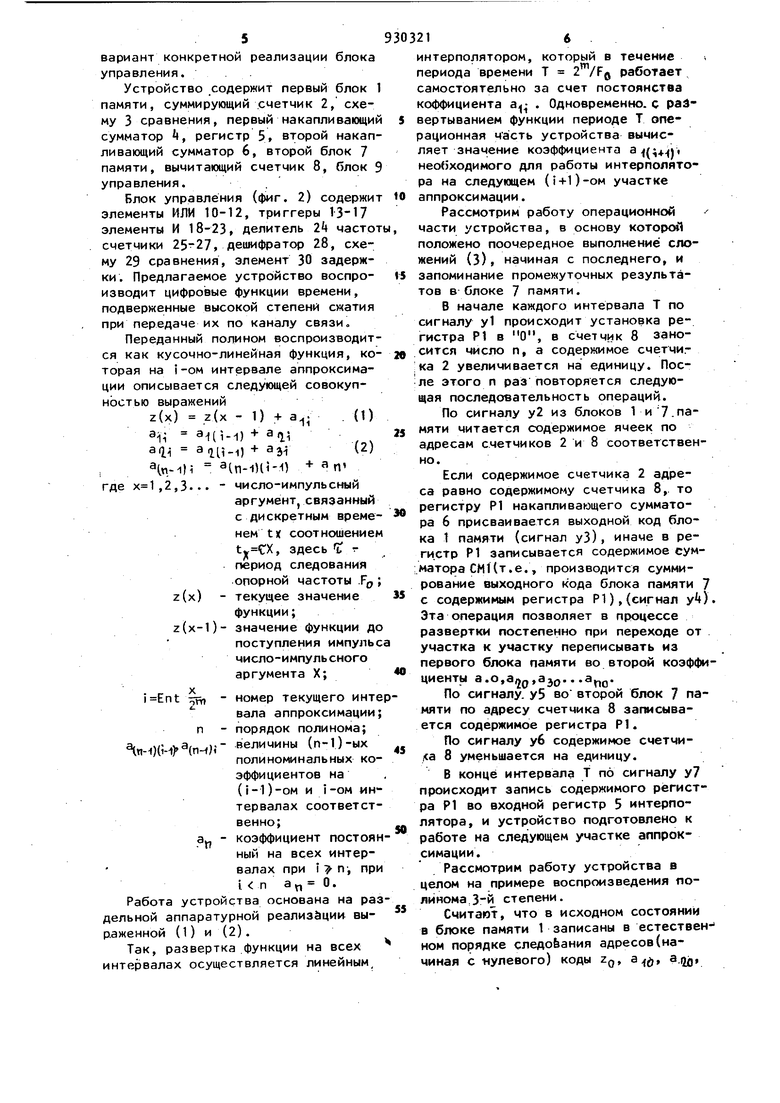

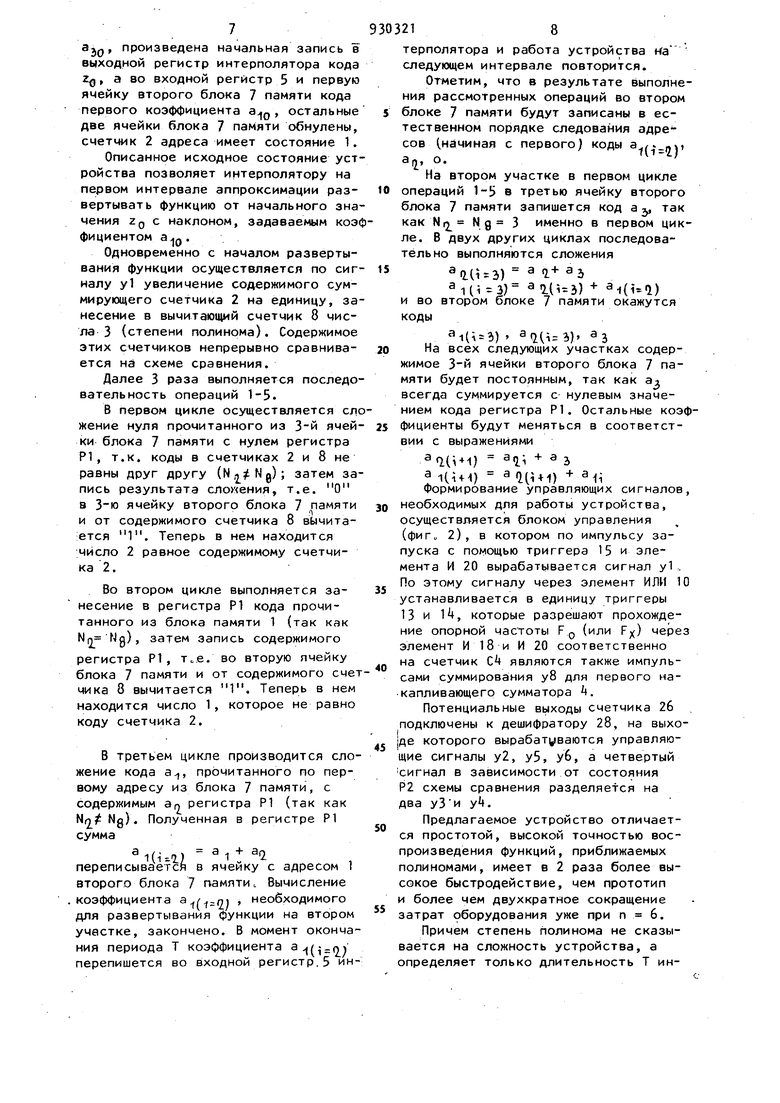

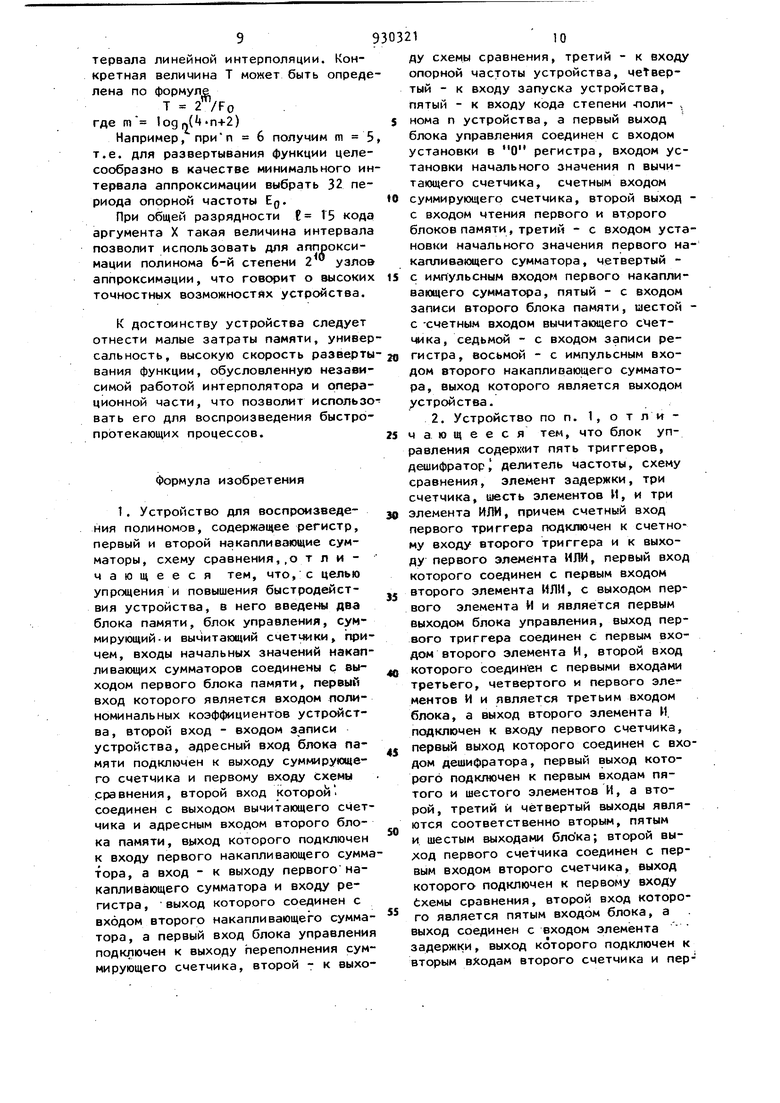

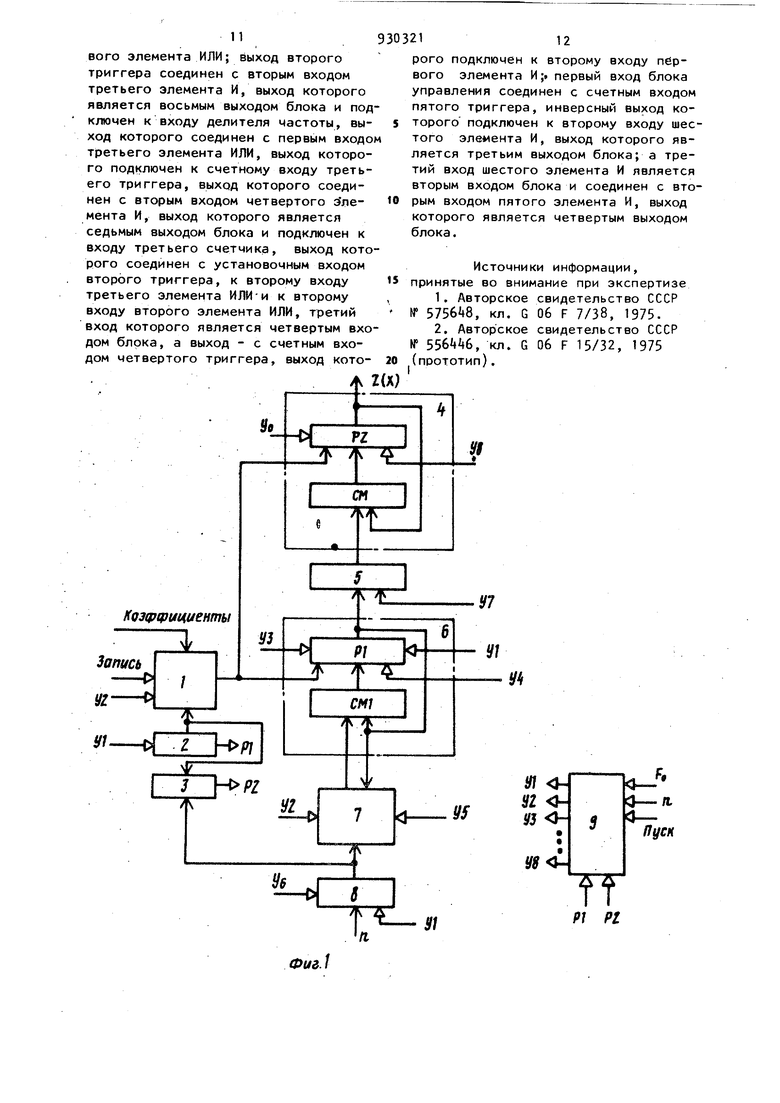

но вторым, пятым и шестым выходами блока, второй выход первого счетчика соединен с первым входом второго счетчика, выход которого подключен к первому входу схемы сравнения, второй вход которой является пятым входом блока, а выход соединен с входом элемента задержки, выход которого подключен к вторым входам второго 14 мента ИЛИ, с выходом первого элемента И и является первым выходом блока управления, выход первого триггера соединен с первым входом второго элемента И, второй вход которого соединен с первыми входами третьего, четвертого и первого элемента И и является третьим входом блока, а выход второго элемента И подключен к выходу первого счетчика, первый выход которого соединен с входом дешифратора, первый выход которого подключен к первым входам пятого и шестого элементов И, а второй, третий и четвертый выходы являются соответственсчетчика и первого элемента ИЛИ, выход второго триггера соединен с вто рым входом третьего элемента И; выход которого является восьмым выходом блока и подключен к входу делителя частоты, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к счетному входу третьего триггера, выход которого соединен с вторым входом четвертого элемента И, выход которого является седьмым выходом блока и подключен к входу третьего счетчика, выход которого соединен с установочным входом второго триггера, к второму входу третьего элемента ИЛИ и к второму входу второго элемента ИЛИ, третий вход которого является четвертым входом блока, в выход - с счетным входом четвертого триггера, выход которого подключен к второму входу первого элемента И; первый вход блока управления соединен с счетным входом пятого триггера, инверсный -выход которого подключен к второму входу шестого элемента И, выход которого является третьим выходом блока, а третий вход шестого элемента И является вторым входом блока и соединен с вторым входом пятого элемента И, выход которого является четвертым выходом блока. На фиг. 1 представлена схема предагаемого устройства; на фиг. 2 вариант конкретной реализации блока управления. . Устройство содержит первый блок памяти, суммирующий .счетчик 2, схему 3 сравнения, первый накапливающи сумматор , регистр 5, второй накап ливающий сумматор 6, второй блок 7 памяти, вычитающий счетчик 8, блок управления. Блок управления {фиг. 2) содержи элементы ИЛИ 10-12, триггеры 13-17 элементы И 18-23, делитель 2k часто счетчики 25-27, дешифратор 28, схему 29 сравнения, элемент 30 задержки. Предлагаемое устройство воспроизводит цифровые функции времени, подверженные высокой степени сжатия при передаче их по каналу связи. Переданный полином воспроизводит ся как кусочно-линейная функция, ко торая на i-ом интервале аппроксимации описывается следующей совокупностью выражений z(x) z(x - 1) + а. . (1) ( + ч 31i l( + 331 (2) )i )) + an где ,2,3... - число-импульсный аргумент, связанный с дискретным временем tx соотношением t.CX, здесь ь период следования опорной частоты .Fp z(x) - текущее значение функции; z(x-l)- значение функции до поступления импульс число-импульсного аргумента X; - номер текущего инте вала аппроксимации п - порядок полинома; V)(;-)( величины (п-1)-ых полиноминальных коэффициентов на (i-1)-OM и i-OM интервалах соответственно;а - коэффициент постоян ный на всех интервалах при i П-, при 1 п а„ 0. Работа устройства основана на раз дельной аппаратурной реализации выраженной (О и (2). Так, развертка функции на всех интервалах осуществляется линейным. интерполятором, который в течение периода времени Т работает самостоятельно за счет постоянства коффициента а . Одновременно, с радвертыванием функции периоде Т операционная часть устройства вычисляет значение коэффициента нео()ходимого для работы интерполятора на следующем (+1)-ом участке аппроксимации. Рассмотрим работу операционной части устройства, в основу которой положено поочередное выполнение сложений (З), начиная с последнего, и запоминание промежуточных результатов в блоке 7 памяти. В начале каждого интервала Т по сигналу у1 происходит установка регистра Р1 в О, в счетчик 8 заносится число п, а содержимое счетчи.ка 2 увеличивается на единицу. После этого п раз повторяется следующая последовательность операций. По сигналу у2 из блоков 1 и7.памяти читается содержимое ячеек по адресам счетчиков 2 и 8 соответственно. Если содержимое счетчика 2 адреса равно содержимому счетчика 8,. то регистру Р1 накапливающего сумматора 6 присваивается выходной код блока t памяти (сигнал уЗ), иначе в реги.стр Р1 записывается содержимое сумматора СМИт.е., производится суммирование выходного кода блока памяти 7 с содержимым регистра Р1),(сигнал у). Эта операция позволяет в процессе развертки постепенно при переходе от участка к участку переписывать из первого блока памяти во второй коэффициенты а.о,а,2р,азо.... По сигналу. у5 во второй блок 7 памяти по адресу счетчика 8 записывается содержимое регистра Р1. По сигналу у6 содержимое счетчи)са 8 уменьшается на единицу. В конце интервала Т по сигналу у7 происходит запись содержимого регистра Р1 во входной регистр 5 интерполятора, и устройство подготовлено к работе на следующем участке аппроксимации. Рассмотрим работу устройства в целом на примере воспроизведения полинома, 3-й степени. Считают, что в исходном состоянии в блоке памяти 1 записаны в естественном порядке следоЬания адресов(начиная с нулевого) коды ZQ, а, а.(. , произведена начальная запись в выходной регистр интерполятора кода 20, а во входной регистр 5 и первую ячейку второго блока 7 памяти кода первого коэффициента а, остальные две ячейки блока 7 памяти обнулены, счетчик 2 адреса имеет состояние 1. Описанное исходное состояние уст ройства позволяет интерполятору на первом интервале аппроксимации развертывать функцию от начального зна чения ZQ с наклоном, задаваемым коэ фициентом . Одновременно с началом развертывания функции осуществляется по сиг налу у1 увеличение содержимого суммирующего счетчика 2 на единицу, за несение в вычитающий счетчик 8 числа 3 (степени полинома). Содержимое этих счетчиков непрерывно сравнивается ни схеме сравнения. Далее 3 раза выполняется последо вательность операций 1-5. В первом цикле осуществляется ел жение нуля прочитанного из 3-й ячей ки блока 7 памяти с нулем регистра Р1, т.к. коды в счетчиках 2 и 8 не равны друг другу (N,); затем за пись результата , т.е. О в ячейку второго блока 7 памяти и от содержимого счетчика 8 вЫчита ется 1. Теперь в нем находится число 2 равное содержимому счетчика 2. Во втором цикле выполняется занесение в регистра Р1 кода прочитанного из блока памяти 1 (так как ), затем запись содержимого регистра Р1, т.е. во вторую ячейку блока 7 памяти и от содержимого счет чика 8 вычитается 1. Теперь в нем находится число 1, которое не равно коду счетчика 2. В третьем цикле производится сложение кода а.,, прочитанного по первому адресу из блока 7 памяти, с содержимым Эп регистра Р1 (так как Nn# Ng). Полученная в регистре Р1 сумма 1(1-1) i а переписывается в ячейку с адресом 1 второго блока 7 памяти Вычисление коэффициента ,п , необходимого для развертывания функции на втором участке, закончено. В момент окончания периода Т коэффициента . перепишется во входной регистр.5 ин218терполятора и работа устройства на следующем интервале повторится. Отметим, что в результате выполнения рассмотренных операций во втором блоке 7 памяти будут записаны в естественном порядке следования адресов (начиная с первого) коды a./.-v 3,31, о. На втором участке в первом цикле операций 1-5 в третью ячейку второго блока 7 памяти запишется код а j, так как Nr2 Ng 3 именно в первом цикле. В двух других циклах последовательно выполняются сложения 1(1 3) 3 1+ aj 31(1 3) 1( + «(ьа) и во втором блоке 7 памяти окажутся коды 1( 3) 31() aj На всех следующих участках содержимое ячейки второго блока 7 памяти будет постоянным, так как а всегда суммируется с нулевым значением кода регистра Р1. Остальные коэффициенты будут меняться в соответствии с выражениями aQ + а j 1(i+1) . . a(Ul) + iCiM) Формирование управляющих сигналов, необходимых для работы устройства, осуществляется блоком управления (фиг„ 2), в котором по импульсу запуска с помощью триггера 15 и элемента И 20 вырабатывается сигнал у1 ,. По этому сигналу через элемент ИЛИ 10 устанавливается в единицу триггеры 13 и 14, которые разрешают прохождение опорной частоты FQ (или через элемент И 18 и И 20 соответственно на счетчик С4 являются также импульсами суммирования у8 для первого иакапливающего сумматора . Потенциальные выходы счетчика 26 подключены к дешифратору 28, на выходе которого вырабатываются управляющие сигналы у2, у5, у6, а четвертый Сигнал в зависимости от состояния Р2 схемы сравнения paздeляetcя на два уЗи yk. Предлагаемое устройство отличается простотой, высокой точностью воспроизведения функций, приближаемых полиномами, имеет в 2 раза более высокое быстродействие, чем прототип и более чем двухкратное сокращение затрат оборудования уже при п 6. Причем степень полинома не сказывается на сложность устройства, а определяет только длительность Т интервала линейной интерполяции. Конкретная величина Т может быть опред лена по формуле Т где т ) Например, прип 6 получим m т.е. для развертывания функции целе сообразно в качестве минимального и тервала аппроксимации выбрать 32 пе риода опорной частоты EQ. При общей разрядности t 15 код аргумента X такая величина интервал позволит использовать для аппроксимации полинома 6-й степени 2 узло аппроксимации, что говорит о высоки точностных возможностях устройства, К достоинству устройства следует отнести малые затраты памяти, универ сальность, высокую скорость разверты вания функции, обусловленную независимой работой интерполятора и операционной части, что позволит использо вать его для воспроизведения быстропротекающих процессов. Формула изобретения 1. Устройство для воспроизведения полиномов, содержащее регистр, первый и второй накапливающие сумматоры, схему сравнения,,о т л и чающееся тем, что, с целью упрощения и повышения быстродействия устройства, в него введены два блока памяти, блок управления, суммирующий -и вычитающий счетчики, причем, входы начальных значений накапливающих сумматоров соединены с вь ходом первого блока памяти, первый вход которого является входом полиноминальных коэффициентов устройства , второй вход - входом записи устройства, адресный вход блока памяти подключен к выходу суммирующего счетчика и первому входу схемы .ера внения, второй вход которой соединен с выходом вычитающего счетчика и адресным входом второго блока памяти, выход которого подключен к входу первого накапливающего сумма тора, а вход - к выходу первого накапливающего сумматора и входу регистра, выход которого соединен с входом второго накапливающего сумматора, а первый вход блока управления подключен к выходу переполнения суммирующего счетчика, второй - к выходу схемы сравнения, третий - к входу опорной частоты устройства, чеТвертый - к входу запуска устройства, пятый - к входу кода степени -поли- , нома п устройства, а первый выход блока управления соединен с входом установки в О регистра, входом установки начального значения п вычитающего счетчика, счетным входом суммирующего счетчика, второй выход с входом чтения первого и второго блоков памяти, третий - с входом установки начального значения первого накапливающего сумматора, четвертый с импульсным входом первого накапливающего сумматора, пятый - с входом записи второго блока памяти, шестой с -счетным входом вычитающего счетчика, седьмой - с входом записи регистра, восьмой - с импульсным входом второго накапливающего сумматора, выход которого является выходом устройства. 2. Устройство по п. 1, о т ли чающееся тем, что блок управления содерк ит пять триггеров, дешифратору делитель частоты, схему сравнения, элемент задержки, три счетчика, шесть элементов И, и три элемента ИЛИ, причем счетный вход первого триггера подключен к счетному входу второго триггера и к выходу первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ, с выходом первого элемента И и является первым выходом блока управления, выход первого триггера соединен с первым входом второго элемента И, второй вход которого соединен с первыми входами третьего, четвертого и первого злегментов И и является третьим входом блока, а выход второго элемента И. подключен к входу первого счетчика, первый выход которого соединен с входом дешифратора, первый выход которого подключен к первым входам пятого и шестого элементов И, а второй, третий и четвертый выходы являются соответственно вторым, пятым и шестым выходами блока; второй выход первого счетчика соединен с первым входом второго счетчика, выход которого подключен к первому входу Схемы сравнения, второй вход которого является пятым входом блока, а выход соединен с входом элемента задержки, выход которого подключен к вторым входам второго счетчика и первого элемента ИЛИ; выход второго триггера соединен с вторым входом третьего элемента И, выход которого является восьмым выходом блока и под ключен к входу делителя частоты, выход которого соединен с первым входо третьего элемента ИЛИ, выход которого подключен к счетному входу третьего триггера, выход которого соединен с вторым входом четвертого элемента И, выход которого является седьмым выходом блока и подключен к входу третьего счетчика, выход кото рого соединен с установочным входом второго триггера, к второму входу третьего элемента ИЛИи к второму входу второго элемента ИЛИ, третий вход которого является четвертым вхо дом блока, а выход - с счетным входом четвертого триггера, выход кото--Чрого подключен к второму входу первого элемента И; первый вход блока управления соединен с счетным входом пятого триггера, инверсный выход которого подключен к второму входу шестого элемента И, выход которого является третьим выходом блока; а третий вход шестого элемента И является вторым входом блока и соединен с вторым входом пятого элемента И, выход которого является четвертым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 5756i 8, кл. G 06 F 7/38, 1975. 2.Авторское свидетельство СССР № , кл. G Об F 15/32, 1975 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа распределений случайных процессов | 1985 |

|

SU1247896A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для синтеза регрессионных моделей многомерной статистики | 1980 |

|

SU942031A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1361577A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для ввода информации | 1984 |

|

SU1251089A1 |

| Анализатор случайных процессов | 1987 |

|

SU1474678A1 |

Авторы

Даты

1982-05-23—Публикация

1980-06-25—Подача