Изобретение относится к автоматике и вычислительной технике, в частности к полиномиальным и сплайн-интерполяторам, и может быть использовано в автоматических системах управления для воспроизведения нелинейных зависимостей одной переменной.

Известные устройства (АС СССР N 1405074, G 06 F 15/353 от 27.10.1986, АС СССР N 1686461, G 06 F 15/353 от 13.02.1989, Патент РФ N 2127901, G 06 F 17/17 от 20.03.99 г., Бюл. N 8) позволяют воспроизводить широкий класс функциональных зависимостей, но обладают низкой помехоустойчивостью.

Наиболее близким к заявляемому устройству по своей технической сущности является "Сплайн-интерполятор" (Патент РФ N 2127901, G 06 F 17/17 от 20.03.99 г.), выбранный в качестве устройства-прототипа.

Устройство-прототип содержит первый и второй блоки памяти, счетчик, блок управления, первый, второй, третий, четвертый, пятый и шестой умножители, сумматор, регистр, блок формирования коэффициентов сплайна и блок формирования параметров сплайна, причем информационные входы счетчика и адресные входы первого блока памяти объединены и соединены с первой установочной шиной сплайн-интерполятора, а выходы счетчика соединены с третьей группой входов блока управления, первый вход которого является тактовой шиной сплайн-интерполятора, второй вход - шиной запуска сплайн-интерполятора, десятый выход соединен с управляющим входом регистра и вычитающим входом счетчика, а восьмой выход блока управления соединен со входом управления второго блока памяти, первая, вторая, третья и четвертая группы выходов которого соединены соответственно с первыми входами первого, второго, третьего и четвертого умножителей, выходы которых соединены соответственно с первой второй, третьей и четвертой группами информационных входов сумматора, выходы которого соединены с информационными входами регистра, выходы которого являются выходами сплайн-интерполятора, первый вход блока формирования коэффициентов сплайна соединен с девятым выходом блока управления, четвертая, пятая, шестая и седьмая группы входов блока управления соответственно являются второй, третьей, четвертой и пятой установочными шинами сплайн-интерполятора, одиннадцатый выход блока управления соединен с шестым входом блока формирования параметров сплайна и входом управления сумматора, пятая и шестая группы информационных входов сумматора соединены соответственно с выходами пятого и шестого умножителей, первые группы входов пятого и шестого умножителей соединены соответственно с пятой и шестой группами выходов второго блока памяти, информационные входы второго блока памяти соединены с девятой группой выходов блока формирования коэффициентов сплайна, вторая, третья, четвертая, шестая, седьмая и восьмая группы входов блока формирования коэффициентов сплайна соответственно являются шестой, седьмой, восьмой, девятой, десятой и одиннадцатой установочными шинами сплайн-интерполятора, пятая группа входов блока формирования коэффициентов сплайна представляет собой информационную шину сплайн-интерполятора, двенадцатая установочная шина сплайн-интерполятора соединена с первой группой входов блока формирования параметров сплайна, вторая и третья группы входов блока формирования параметров сплайна соответственно являются тринадцатой и четырнадцатой установочными шинами сплайн-интерполятора, четвертая группа входов блока формирования параметров сплайна соединена с выходами первого блока памяти, а пятая группа входов - с выходами счетчика, управляющий вход счетчика объединен со вторым входом блока управления и одновременно является шиной запуска сплайн-интерполятора, седьмая восьмая, девятая, десятая, одиннадцатая и двенадцатая группы выходов блока формирования параметров сплайна соединены со вторыми группами входов соответственно шестого, пятого, четвертого, третьего, второго и первого умножителей.

Известное техническое решение обладает недостатком. Так, при интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈C7), информация о которых имеется в виде дискретных данных с погрешностями, в данном устройстве не полностью учитывается информация о функции, вследствие чего прототип не обеспечивает необходимой помехоустойчивости.

Целью изобретения является разработка устройства, обеспечивающего более высокую помехоустойчивость при интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈C7).

Поставленная цель достигается тем, что в известном сплайн-интерполяторе, содержащем первый и второй блоки памяти, блок управления, первый, второй, третий, четвертый, пятый и шестой умножители, блок формирования параметров сплайна, блок формирования коэффициентов сплайна, сумматор и регистр, причем информационные входы счетчика и адресные входы первого блока памяти объединены и соединены с первой установочной шиной сплайн-интерполятора, а выходы счетчика соединены с пятой группой входов блока формирования параметров сплайна и третьей группой входов блока управления, первый вход которого является тактовой шиной сплайн-интерполятора, второй вход является шиной запуска сплайн-интерполятора и одновременно соединен с вычитающим входом счетчика, четвертая группа входов блока управления является второй установочной шиной сплайн-интерполятора, пятая группа входов - третьей установочной шиной сплайн-интерполятора, шестая группа входов - четвертой установочной шиной сплайн-интерполятора, седьмая группа входов блока управления является пятой установочной шиной сплайн-интерполятора, а девятый выход соединен с первым входом блока формирования коэффициентов сплайна, вторая, третья, четвертая, шестая, седьмая и восьмая группы входов которого являются соответственно шестой, седьмой, восьмой, девятой, десятой и одиннадцатой установочными шинами сплайн-интерполятора, пятая группа входов блока формирования коэффициентов сплайна является информационной шиной сплайн-интерполятора, а девятая группа выходов соединена с адресными входами второго блока памяти, первая, вторая, третья, четвертая, пятая и шестая группы выходов которого соединены со вторыми группами входов соответственно первого, второго, третьего, четвертого, пятого и шестого умножителей, а вход управления второго блока памяти соединен с восьмым выходом блока управления, десятый выход которого соединен со входами управления счетчика и регистра, а одиннадцатый выход блока управления соединен со входом управления сумматора и шестым входом блока формирования параметров сплайна, первая, вторая и третья группы входов которого являются соответственно двенадцатой, тринадцатой и четырнадцатой установочными шинами сплайн-интерполятора, четвертая группа входов блока формирования параметров сплайна соединена с выходами первого блока памяти, а седьмая, восьмая, девятая, десятая, одиннадцатая и двенадцатая группы выходов соединены с перовыми группами входов соответственно первого, второго, третьего, четвертого, пятого и шестого умножителей, выходы которых соединены соответственно с первой, второй, третьей, четвертой, пятой и шестой группами информационных входов сумматора, выходы которого соединены с информационными входами регистра, выходы которого являются выходной шиной сплайн-интерполятора, причем блок формирования коэффициентов сплайна выполнен содержащим первый, второй, третий, четвертый, десятый, одиннадцатый и тринадцатый умножители, первый, второй, третий, четвертый, пятый, шестой, двенадцатый и тринадцатый элементы задержки, первый, второй и четвертый сумматоры, причем первая группа входов первого умножителя объединена с первыми группами входов второго, третьего и четвертого умножителей, группами информационных входов первого, третьего, шестого и тринадцатого элементов задержки, первой группой информационных входов второго сумматора и одновременно соединена с пятой информационной шиной сплайн-интерполятора, вторая группа входов первого умножителя соединена со второй группой входов блока формирования коэффициентов сплайна и шестой установочной шиной сплайн-интерполятора, а выходы первого умножителя соединены с группой информационных входов второго элемента задержки, выходы которого соединены со второй группой информационных входов первого сумматора, первая группа информационных входов которого соединена с выходами первого элемента задержки, третья группа информационных входов первого сумматора соединена с выходом третьего элемента задержки, а выходы соединены с первой группой входов десятого умножителя, вторая группа входов которого соединена с третьей группой входов блока формирования коэффициентов сплайна и седьмой установочной шиной сплайн-интерполятора, а выходы десятого умножителя соединены с группой информационных входов двенадцатого элемента задержки, выходы которого соединены с первой группой информационных входов четвертого сумматора, вторая группа информационных входов которого соединена с выходами тринадцатого элемента задержки, вторая группа входов одиннадцатого умножителя соединена с седьмой группой входов блока формирования коэффициентов сплайна и десятой установочной шиной сплайн-интерполятора, а первая группа входов одиннадцатого умножителя соединена с выходами второго сумматора, вторая группа информационных входов которого соединена с выходами второго умножителя, третья группа информационных входов соединена с выходами четвертого элемента задержки, третий умножитель, соединенный с четвертым элементом задержки, предназначен для формирования слагаемого для второго сумматора, вторая группа входов третьего умножителя соединена с четвертой группой входов блока формирования коэффициентов сплайна и восьмой установочной шиной сплайн-интерполятора, четвертая группа информационных входов второго сумматора соединена с выходами пятого элемента задержки, группа информационных входов которого соединена с выходами четвертого умножителя, вторая группа входов которого объединена со второй группой входов второго умножителя и шестой группой входов блока сплайн-интерполятора, а пятая группа информационных входов второго сумматора соединена с выходами шестого элемента задержки, вход управления которого объединен со входами управления первого, второго, третьего, четвертого, пятого, двенадцатого и тринадцатого элементов задержки, входами управления первого, второго и четвертого сумматоров и одновременно соединен с первым входом блока формирования коэффициентов сплайна, первая группа входов тринадцатого умножителя соединена с выходами четвертого сумматора, вторая группа входов тринадцатого умножителя соединена с восьмой группой входов блока формирования коэффициентов сплайна и одновременно одиннадцатой установочной шиной сплайн-интерполятора, а выходы тринадцатого умножителя соединены с девятой группой выходов блока формирования коэффициентов сплайна, в блок формирования коэффициентов сплайна дополнительно введены пятый, шестой, седьмой, восьмой, девятый и двенадцатый умножители, седьмой, восьмой, девятый, десятый, одиннадцатый и четырнадцатый элементы задержки и третий сумматор. Вторая группа входов пятого умножителя объединена со второй группой входов девятого умножителя и десятой группой входов блока формирования коэффициентов сплайна и одновременно пятнадцатой установочной шиной сплайн-интерполятора, выходы пятого умножителя соединены со второй группой информационных входов третьего сумматора, третья группа информационных входов которого соединена с выходами седьмого элемента задержки. Группа информационных входов седьмого элемента задержки соединена с выходами шестого умножителя, вторая группа входов которого объединена со второй группой входов восьмого умножителя и одиннадцатой группой входов блока формирования коэффициентов сплайна и одновременно шестнадцатой установочной шиной сплайн-интерполятора. Четвертая группа информационных входов третьего сумматора соединена с выходами восьмого элемента задержки, группа информационных входов которого соединена с выходами седьмого умножителя. Вторая группа входов седьмого умножителя соединена с двенадцатой группой входов блока формирования коэффициентов сплайна и семнадцатой установочной шиной сплайн-интерполятора. Пятая группа информационных входов третьего сумматора соединена с выходами девятого элемента задержки, группа информационных входов которого соединена с выходами восьмого умножителя. Шестая группа информационных входов третьего сумматора соединена с выходами десятого элемента задержки, группа информационных входов которого соединена с выходами девятого умножителя.

Седьмая группа информационных входов третьего сумматора соединена с выходами одиннадцатого элемента задержки. Первая группа информационных входов третьего сумматора объединена с первыми группами входов пятого, шестого, седьмого, восьмого и девятого умножителей, информационными входами одиннадцатого элемента задержки и соединена с первой группой входов четвертого умножителя. Выходы третьего сумматора соединены с первой группой входов двенадцатого умножителя, вторая группа входов которого соединена с тринадцатой группой входов блока формирования коэффициентов сплайна и восемнадцатой установочной шиной сплайн-интерполятора. Выходы двенадцатого умножителя соединены с четвертой группой информационных входов четвертого сумматора. Третья группа информационных входов четвертого сумматора соединена с выходами четырнадцатого элемента задержки, группа информационных входов которого соединена с выходами одиннадцатого умножителя. Вход управления четвертого сумматора объединен со входами управления седьмого, восьмого, девятого, десятого, одиннадцатого и четырнадцатого элементов задержки и входом управления третьего сумматора.

Перечисленная новая совокупность существенных признаков заявленного устройства обеспечивает более высокую помехоустойчивость интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈C7). При этом точность интерполяции, аналогичная прототипу, достигается путем увеличения шаблона сплайна на два дискретных отсчета, а более высокая помехоустойчивость достигается таким построением импульсной характеристики фильтра (сглаживающий сплайн - это фактически фильтр // Известия ВВУЗов... Радиоэлектроника, 1995. - Т. 38. - N 4. - С. 12), чтобы минимизировать дисперсию погрешностей интерполируемой функции.

Заявленное устройство поясняется чертежами, на которых:

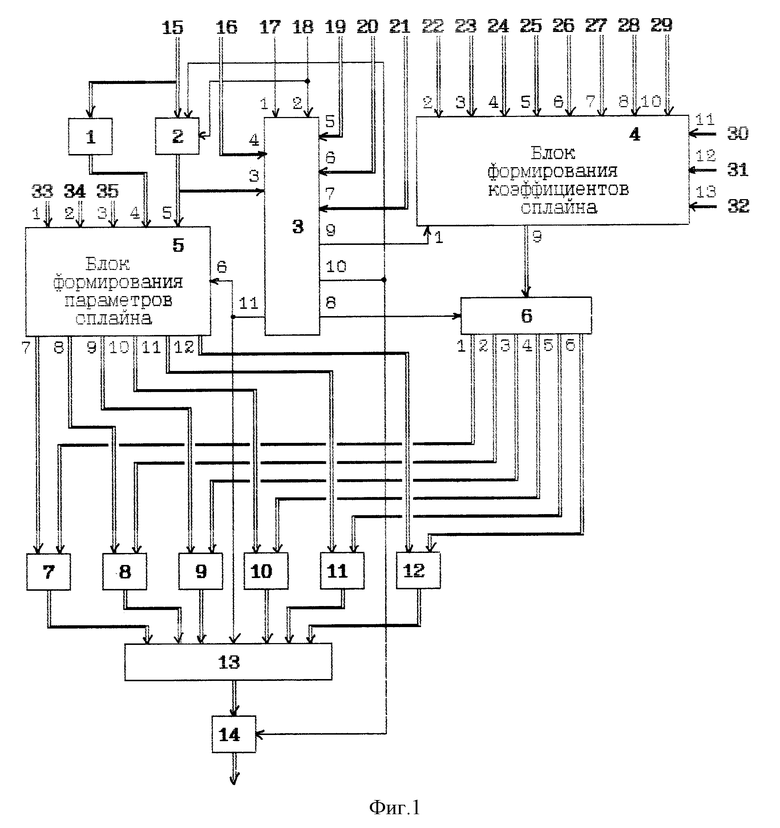

на фиг. 1 приведена структурная схема заявленного устройства;

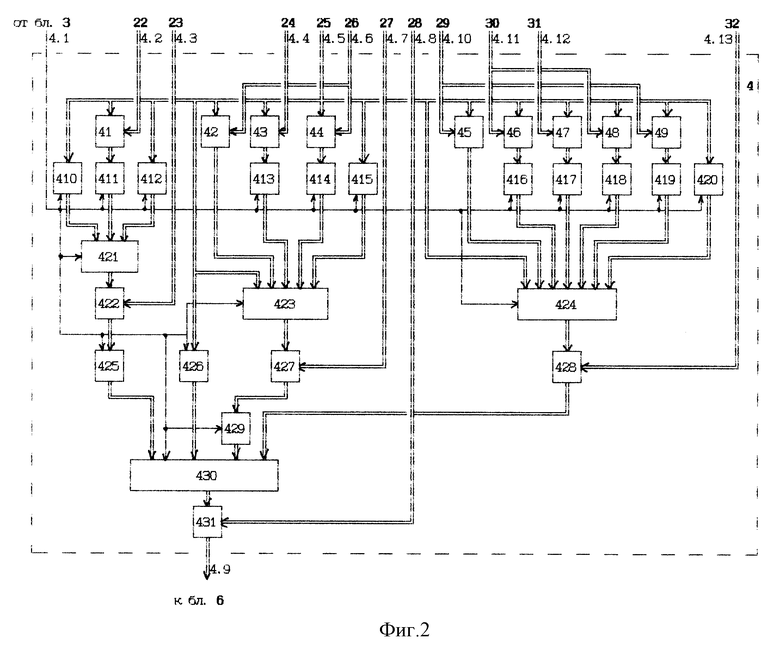

на фиг. 2 представлена структурная схема блока формирования коэффициентов сплайна.

Сплайн-интерполятор, показанный на фиг. 1, состоит из первого 1 и второго 6 блоков памяти, счетчика 2, блока управления 3, блока формирования коэффициентов сплайна 4, блока формирования параметров сплайна 5, первого 7, второго 8, третьего 9, четвертого 10, пятого 11 и шестого 12 умножителей, сумматора 13 и регистра 14. Информационные входы счетчика 2 и адресные входы первого блока памяти 1 объединены и соединены с первой установочной шиной 15 сплайн-интерполятора. Выходы счетчика 2 соединены с пятой группой входов блока формирования параметров сплайна 5 и третьей группой входов блока управления 3. Первый вход блока управления 3 является тактовой шиной 17 сплайн-интерполятора. Второй вход блока управления 3 является шиной запуска 18 сплайн-интерполятора и одновременно соединен с вычитающим входом счетчика 2. Четвертая группа входов блока управления 3 является второй установочной шиной 16 сплайн-интерполятора. Пятая группа входов блока управления 3 является третьей установочной шиной 19 сплайн-интерполятора. Шестая группа входов блока управления 3 является четвертой установочной шиной 20 сплайн-интерполятора. Седьмая группа входов блока управления 3 является пятой установочной шиной 21 сплайн-интерполятора. Девятый выход блока управления 3 соединен с первым входом блока формирования коэффициентов сплайна 4. Вторая, третья, четвертая, шестая, седьмая и восьмая группы входов блока формирования коэффициентов сплайна 4 являются соответственно шестой 22, седьмой 23, восьмой 24, девятой 26, десятой 27 и одиннадцатой 28 информационными шинами сплайн-интерполятора. Пятая группа входов блока формирования коэффициентов сплайна 4 является информационной шиной 25 сплайн-интерполятора. Девятая группа выходов блока формирования коэффициентов сплайна 4 соединена с адресными входами второго блока памяти 6. Первая, вторая, третья, четвертая, пятая и шестая группы выходов второго блока памяти 6 соединены со вторыми группами входов соответственно первого 7, второго 8, третьего 9, четвертого 10, пятого 11 и шестого 12 умножителей. Вход управления второго блока памяти 6 соединен с восьмым выходом блока управления 3. Десятый выход блока управления 3 соединен со входами управления счетчика 2 и регистра 14. Одиннадцатый выход блока управления 3 соединен со входом управления сумматора 13 и шестым входом блока формирования параметров сплайна 5. Первая, вторая и третья группы входов блока формирования параметров сплайна 5 являются соответственно двенадцатой 33, тринадцатой 34 и четырнадцатой 35 информационными шинами сплайн-интерполятора. Четвертая группа входов блока формирования параметров сплайна 5 соединена с выходами первого блока памяти 1. Седьмая, восьмая, девятая, десятая, одиннадцатая и двенадцатая группы выходов блока формирования параметров сплайна 5 соединены с первыми группами входов соответственно первого 7, второго 8, третьего 9, четвертого 10, пятого 11 и шестого 12 умножителей, выходы которых соединены соответственно с первой, второй, третьей, четвертой, пятой и шестой группами информационных входов сумматора 13. Выходы сумматора 13 соединены с информационными входами регистра 14. Выходы регистра 14 являются выходной шиной сплайн-интерполятора.

Блок формирования коэффициентов сплайна 4, показанный на фиг. 2, состоит из первого 41, второго 42, третьего 43, четвертого 44, пятого 45, шестого 46, седьмого 47, восьмого 48, девятого 49, десятого 422, одиннадцатого 427, двенадцатого 428 и тринадцатого 431 умножителей, первого 410, второго 411, третьего 412, четвертого 413, пятого 414, шестого 415, седьмого 416, восьмого 417, девятого 418, десятого 419, одиннадцатого 420, двенадцатого 425, тринадцатого 426 и четырнадцатого 429 элементов задержки, первого 421, второго 423, третьего 424 и четвертого 430 сумматоров. Первая группа входов первого умножителя 41 объединена с первыми группами входов второго 42, третьего 43, четвертого 44, пятого 45, шестого 46, седьмого 47, восьмого 48 и девятого 49 умножителей, группами информационных входов первого 410, третьего 412, шестого 415, одиннадцатого 420 и тринадцатого 426 элементов задержки, первыми группами информационных входов второго 423 и третьего 424 сумматора и одновременно соединена с шестой группой входов 4.6 блока формирования коэффициентов сплайна 4 и девятой установочной шиной 26 сплайн-интерполятора. Вторая группа входов первого умножителей 41 соединена со второй группой входов 4.2 блока формирования коэффициентов сплайна 4 и шестой установочной шиной 22 сплайн-интерполятора, а выходы соединены с группой информационных входов второго элемента задержки 411. Выходы второго элемента задержки 411 соединены со второй группой информационных входов первого сумматора 421. Первая группа информационных входов первого сумматора 421 соединена с выходами первого элемента задержки 410. Третья группа информационных входов первого сумматора 421 соединена с выходами третьего элемента задержки 412. Выходы первого сумматора 421 соединены с первой группой входов десятого умножителя 422. Вторая группа входов десятого умножителя 422 соединена с третьей группой входов 4.3 блока формирования коэффициентов сплайна 4 и седьмой установочной шиной 23 сплайн-интерполятора. Выходы десятого умножителя 422 соединены с группой информационных входов двенадцатого элемента задержки 425. Выходы двенадцатого элемента задержки 425 соединены с первой группой информационных входов четвертого сумматора 430. Вторая группа информационных входов четвертого сумматора 430 соединена с выходами тринадцатого элемента задержки 426. Третья группа информационных входов четвертого сумматора 430 соединена с выходами четырнадцатого элемента задержки 429. Группа информационных входов четырнадцатого элемента задержки 429 соединена с выходами одиннадцатого умножителя 427. Вторая группа входов одиннадцатого умножителя 427 соединена с седьмой группой входов 4.7 блока формирования коэффициентов сплайна 4 и десятой установочной шиной 27 сплайн-интерполятора. Первая группа входов одиннадцатого умножителя 427 соединена с выходами второго сумматора 423. Вторая группа информационных входов второго сумматора 423 соединена с выходами второго умножителя 42. Третья группа информационных входов второго сумматора 423 соединена с выходами четвертого элемента задержки 413. Группа информационных выходов четвертого элемента задержки 413 соединена с выходами третьего умножителя 43. Вторая группа входов третьего умножителя 43 соединена с четвертой группой входов 4.4 блока формирования коэффициентов сплайна 4 и восьмой установочной шиной 24 сплайн-интерполятора. Четвертая группа информационных входов второго сумматора 423 соединена с выходами пятого элемента задержки 414. Группа информационных входов пятого элемента задержки 414 соединена с выходами четвертого умножителя 44. Вторая группа входов четвертого умножителя 44 объединена со второй группой входов второго умножителя 42 и шестой группой входов 4.6 блока формирования коэффициентов сплайна 4 и девятой установочной шиной 26 сплайн-интерполятора. Пятая группа информационных входов второго сумматора 423 соединена с выходами шестого элемента задержки 415. Вторая группа входов пятого умножителя 45 объединена со второй группой входов девятого умножителя 49 и десятой группой входов 4.10 блока формирования коэффициентов сплайна 4 и одновременно с пятнадцатой установочной шиной 29 сплайн-интерполятора. Выходы пятого умножителя 45 соединены со второй группой информационных входов третьего сумматора 424. Третья группа информационных входов третьего сумматора 424 соединена с выходами седьмого элемента задержки 416. Группа информационных входов седьмого элемента 416 задержки соединена с выходами шестого умножителя 46. Вторая группа входов шестого умножителя 46 объединена со второй группой входов восьмого умножителя 48 и одиннадцатой группой входов 4.11 блока формирования коэффициентов сплайна 4 и одновременно шестнадцатой установочной шиной 30 сплайн-интерполятора. Четвертая группа информационных входов третьего сумматора 424 соединена с выходами восьмого элемента задержки 417. Группа информационных входов восьмого элемента задержки 417 соединена с выходами седьмого умножителя 47. Вторая группа входов седьмого умножителя 47 соединена с двенадцатой группой входов 4.12 блока формирования коэффициентов сплайна 4 и одновременно является семнадцатой установочной шиной 31 сплайн-интерполятора. Пятая группа информационных входов третьего сумматора 424 соединена с выходами девятого элемента задержки 418. Группа информационных входов девятого элемента задержки 418 соединена с выходами восьмого умножителя 48. Шестая группа информационных входов третьего сумматора 424 соединена с выходами десятого элемента задержки 419. Группа информационных входов десятого элемента задержки 419 соединена с выходами девятого умножителя 49. Седьмая группа информационных входов третьего сумматора 424 соединена с выходами одиннадцатого элемента задержки 420. Выходы третьего сумматора 424 соединены с первой группой входов двенадцатого умножителя 428. Вторая группа входов двенадцатого умножителя 428 соединена с тринадцатой группой входов 4.13 блока формирования коэффициентов сплайна 4 и одновременно восемнадцатой установочной шиной 32 сплайн-интерполятора. Выходы двенадцатого умножителя 428 соединены с четвертой группой информационных входов четвертого сумматора 430. Выходы четвертого сумматора 40 соединены с первой группой входов тринадцатого умножителя 431. Вторая группа входов тринадцатого умножителя 431 соединена с восьмой группой входов 4.8 блока формирования коэффициентов сплайна 4 и одновременно одиннадцатой установочной шиной 28 сплайн-интерполятора. Выходы тринадцатого умножителя 431 соединены с девятой группой выходов 4.9 блока формирования коэффициентов сплайна 4. Первый вход 4.1 блока формирования коэффициентов сплайна 4 соединен со входами управления первого 410, второго 411, третьего 412, четвертого 413, пятого 414, шестого 415, седьмого 416, восьмого 417, девятого 418, десятого 419, одиннадцатого 420, двенадцатого 425, тринадцатого 426 и четырнадцатого 429 элементов задержки, первого 421, второго 423, третьего 424 и четвертого 430 сумматоров.

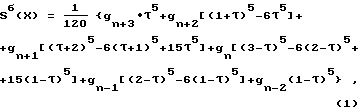

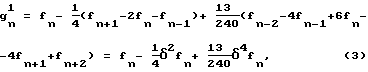

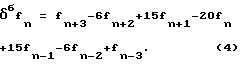

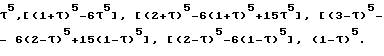

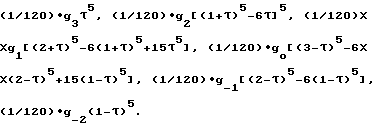

Реализация заявляемого устройства объясняется следующим образом. Из статей: Желудевы В.А. Локальная сплайн-аппроксимация на равномерной сетке // Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 9. - С. 1296-1310, Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов // Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 1. - С. 22-34 и Желудев В.А. Локальные сглаживающие сплайны с регулирующим параметром // Журнал вычислительной математики и математической физики. - 1991. - Том 31. - N 2. - С. 193-211 (формулы (1, 2) на с. 194 и (2.1-2.3) на с. 196; табл. 1 на с. 201 для m = 6, s = 0, ρ = 0,078), известно, что выражение для интерполяции функции локальным сглаживающим сплайном (сплайном максимального сглаживания) пятой степени выглядит следующим образом:

где gn - определяется по формуле

gn = g

Реализация (1) - (4) в виде устройства позволяет вычислять функции f(X)∈C7 с более высокой помехоустойчивостью, обеспечивая точность как у устройства-прототипа (см. Желудев В. А. Локальные сглаживающие сплайны с регулирующим параметром // Журнал вычислительной математики и математической физики. - 1987. - Том 31. - N 2. - С. 197-202).

Работа сплайн-интерполятора на основе фиг. 1 и выражения (1) осуществляется следующим образом.

В исходном состоянии на установочную шину 15 подается код числа М. На тактовую шину 17 поступают тактовые импульсы типа меандр. На установочной шине 16 присутствует код числа 0, на установочной шине 19 - код числа 10, на установочной шине 20 - код числа 16, на установочной шине 21 - код числа 7, на установочной шине 22 - код числа - 2, на установочной шине 23 - код числа - 1/4, на установочной шине 24 - код числа 6, на установочной шине 26 - код числа - 4, на установочной шине 27 - код числа 13/240, на установочной шине 28 - код числа 1/120, на установочной шине 29 - код числа - 6, на установочной шине 30 - код числа 15, на установочной шине 31 - код числа - 20, на установочной шине 31 - код числа 0,078, на установочной шине 33 - код числа 15, на установочной шине 34 - код числа - 6, на установочной шине 35 - код числа 1. В блоке памяти 1 записаны значения τo таким образом, что в ячейке с адресом М хранится значение τo, равное 1/(1+М).

С подачей на шину запуска 18 импульса положительной полярности в счетчик 2 записывается код числа М. На информационную шину 25 подаются отсчеты функции f(x): f-5, ...f-1,...f6, которые поступают в блок формирования коэффициентов сплайна 4. Под воздействием управляющих сигналов, подаваемых на установочные шины 22 - 32, а также сигналов, поступающих с выхода блока управления 3, в блоке формирования коэффициентов сплайна 4 происходит вычисление коэффициента (1/120)•g-2. Указанное значение переписывается в блок памяти 6 под воздействием импульса, поступающего на его управляющий вход с выхода блока управления 3.

Далее аналогичным образом в блоке формирования коэффициентов сплайна 4 вычисляются значения (1/120)•g-1, (1/120)•g0, (1/120)•g1, (1/120)•g2, (1/120)•g3, которые записываются в блок памяти 6.

После этого под воздействием информационных сигналов (поступающих с выходов блоков 1 и 2), а также подаваемых на установочные шины 33 - 35, и управляющих сигналов (с выхода блока управления 3), в блоке формирования параметров сплайна 5 происходит вычисление значений:  Полученные величины поступают на первые входы умножителей 7, 8, 9, 10, 11 и 12. На вторые входы последних поступают соответствующие значения (1/120)•g-2, (1/120)•g-1, (1/120)•g0, (1/120)•g1, (1/120)•g2, (1/120)•g3.

Полученные величины поступают на первые входы умножителей 7, 8, 9, 10, 11 и 12. На вторые входы последних поступают соответствующие значения (1/120)•g-2, (1/120)•g-1, (1/120)•g0, (1/120)•g1, (1/120)•g2, (1/120)•g3.

В результате выполнения операций умножения на выходах умножителей 7, 8, 9, 10, 11 и 12 формируются произведения  Полученные величины поступают на соответствующие группы входов сумматора 13.

Полученные величины поступают на соответствующие группы входов сумматора 13.

В блоке 13 производится суммирование указанных произведений под воздействием сигналов, поступающих на его управляющий вход (с выхода управления 3). В результате на выходе сумматора 13 формируется значение функции f(x) в первой точке интерполяции.

Полученное значение функции f(x) записывается в регистр 14 при помощи единичного импульса, поступающего с выхода блока управления 3 на вход записи регистра 14. Кроме того, этот же единичный импульс с выхода блока управления 3 поступает на вычитающий вход счетчика 2, уменьшая его содержимое на единицу.

Далее алгоритм работы устройства аналогичен. В блоке 5 формируются значения параметров сплайна, а в блоках 7 - 13 вычисляются значения функции f(x), которые записываются в регистр 14. Данная операция повторяется для значений τ, равных τo•(M-1) , затем τo•(M-2) и т.д. до тех пор, пока содержимое счетчика 2 не станет равным нулю. При этом код числа 0 с выхода счетчика 2 поступает на вход блока управления 3, который останавливает работу устройства. На этом работа устройства по вычислению значений функции f(x) завершается. Устройство готово к новому циклу работы.

Входящие в структурную схему заявляемого устройства элементы известны и описаны, например, в [1] . Так, в указанном источнике описаны принципы построения и примеры реализации:

счетчика 2 на с. 85-86 (можно реализовать на микросхеме К155ИЕ5);

блока памяти 1 на с. 171-174 (можно реализовать на микросхеме К155ПР6);

регистра 14 на с. 104-105 (можно реализовать на микросхеме К155ИР13 - с. 111 рис. 1.78).

Принцип работы умножителей 7, 8, 9, 10, 11 и 12 известен и описан в [2] на с. 163 - 221. Могут быть реализованы на микросхемах SN54284 и SN54285, с. 305, рис. 6.3.12 или на микросхеме ADSP1016 (см. [3] с. 502, табл. 7.4).

Принцип работы сумматора 13 известен и описан в [4] на с. 184-198. Полный сумматор описан в [5] на с. 152, рис. 1.112, с. 153, рис. 1.113. Можно реализовать на элементах ИСКЛ. ИЛИ - К155ЛП5, И - К155ЛИ1, ИЛИ - из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1.

Принцип работы блока управления 3 известен и описан в устройстве-прототипе [6]. В указанном источнике реализация блока управления 3 показана на фиг. 4.

Принцип работы блока формирования параметров сплайна 5 известен и описан в устройстве-прототипе [6]. В указанном источнике реализация блока управления 5 показана на фиг. 3.

Принцип построения блока памяти 6 известен и описан в устройстве-прототипе [6] . Может быть реализован, как показано на фиг. 5 указанного источника.

Работа блока формирования коэффициентов сплайн 4 на основе выражений (2)-(4) и фиг. 2 осуществляется следующим образом.

В исходном состоянии на вход 4.2 подается код числа -2 с установочной шины 22 устройства. На вход 4.3 подается код числа -1/4 с установочной шины 23 устройства. На вход 4.4 поступает код числа 6 с установочной шины 24 устройства. На входе 4.6 присутствует код числа -4 с установочной шины 26 устройства. На вход 4.7 подается код числа 13/240 с установочной шины 27 устройства. На входе 4.8 присутствует код числа 1/120 с установочной шины 28 устройства. На вход 4.9 подается код числа -6 с установочной шины 29 устройства. На вход 4.10 поступает код числа 15 с установочной шины 30 устройства. На входе 4.11 присутствует код числа -20 с установочной шины 31 устройства. На вход 4.12 подается код числа 0,078 с установочной шины 32.

При подаче на вход 4.1 блока 4 управляющих импульсов (с выхода 3.9 блока управления 3) на вход 4.5 поступают значения функции f(x): f-5, f-2,...,f6. Последние поочередно в пятнадцати направлениях: на первые входы умножителей 41 - 49, входы элементов задержки 410, 412, 415 и 420, первые входы сумматоров 423 и 424. Блоки 41, 410 - 412 формируют три слагаемых: fn+1, 2fn, fn-1, которые поступают на вход сумматора 421 одновременно. Результаты вычисления в сумматоре 411 являются значения δ2fn (см. выражения (3)). Блоки 42 - 44, 413 - 415 формируют четыре слагаемых для сумматора 423: fn-2, 4fn-1, 6fn, 4fn+1. Пятое слагаемое - fn+2 - поступает со входа 4.5 на сумматор 423 непосредственно. Все пять слагаемых подаются на входы сумматора 423 одновременно. В результате выполнения операции сложения на выходе сумматора 423 формируются значения δ4fn (см. выражение (3)). Блоки 45 - 49, 416 - 420 формируют шесть слагаемых сумматора 424: 6fn+2, 15fn+1, 20fn, 15fn-1, 6fn-2, fn-3. Седьмое слагаемое - fn+3 - поступает на первый вход сумматора 424 со входа 4.5 непосредственно. Результат вычисления в сумматоре 424 - значения δбfn (см. выражение (4)). Величина δ2fn, умноженная на -1/4 в блоке 422 и задержанная в блоке 425, является первым слагаемым для сумматора 430. Вторым слагаемым является значение fn функции f(x), задержанное в блоке 426. Третьим слагаемым является величина δ4fn, умноженная в блоке 427 на число 13/240 и задержанное в блоке 429. Четвертое слагаемое - величина δбfn, умноженная в блоке 428 на число 0,078. Все четыре слагаемых поступают на входы сумматора 430 одновременно. Результат выполнения в блоке 430 операции суммирования умножается в блоке 431 на число 1/120. В результате на выходе блока формирования коэффициентов сплайна 4 формируется значение коэффициента (1/120)gn.

Умножители 41, 42, 43, 44, 45, 46, 47, 48, 422, 427, 428 и 431 известны и описаны в [2] на с. 163 - 221. Могут быть реализованы на микросхемах SN54284 и SN54285, с. 305, рис. 6.3.12 или на микросхеме ADSP1016 (см. [3] с. 502, табл. 7.4).

Принцип работы элементов задержки 410, 411, 412, 413, 414, 415, 416, 417, 418, 419, 420, 425, 426 и 429 известен и описан в устройстве-прототипе [6]. В указанном источнике реализация элементов задержки показана на фиг. 6.

Сумматоры 421, 423, 424 и 430 можно реализовать на К155ЛП5, К155ЛИ1, К155ЛЕ4 и НЕ К155ЛН1.

Литература

1. В.Л. Шило. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1988.

2. М. А. Карцев, В.А. Брик. Вычислительные системы и синхронная арифметика. - М.: Радио и связь, 1981.

3. С. Кун. Матричные процессоры на СБИС: Пер. с англ. - М.: Мир, 1991.

4. Д. Гивоне, Р. Россе. Микропроцессоры и микрокомпьютеры: Вводный курс: Пер. с англ. - М.: Мир, 1983.

5. В. Л. Шило. Популярные цифровые микросхемы. Справочник. 2-е изд., испр., - Челябинск: Металлургия, 1989.

6. Патент N 2127901 RU, МПК6 G 06 F 17/17. Сплайн-интерполятор/ Агиевич С. Н. , Смирнов П.Л., Подымов В.А., Малышев С.Р. (РФ) N 97115388/09; Заяв. 28.08.97; Опубл. 20.03.99, Бюл. N 8, - 36 с., ил. 7.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2165099C2 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматических системах управления. Техническим результатом является повышение помехоустойчивости. Устройство содержит блоки памяти, блок управления, умножители, блок формирования параметров сплайна, блок формирования коэффициентов сплайна, сумматор, элементы задержки, счетчик и регистр. 2 ил.

Сплайн-интерполятор, содержащий первый и второй блоки памяти, блок управления, первый, второй, третий, четвертый, пятый и шестой умножители, блок формирования параметров сплайна, блок формирования коэффициентов сплайна, сумматор и регистр, причем информационные входы счетчика и адресные входы первого блока памяти объединены и соединены с первой установочной шиной сплайн-интерполятора, а выходы счетчика соединены с пятой группой входов блока формирования параметров сплайна и третьей группой входов блока управления, первый вход которого является тактовой шиной сплайн-интерполятора, второй вход является шиной запуска сплайн-интерполятора и одновременно соединен с вычитающим входом счетчика, четвертая группа входов блока управления является второй установочной шиной сплайн-интерполятора, пятая группа входов - третьей установочной шиной сплайн-интерполятора, шестая группа входов - четвертой установочной шиной сплайн-интерполятора, седьмая группа входов блока управления является пятой установочной шиной сплайн-интерполятора, а девятый выход соединен с первым входом блока формирования коэффициентов сплайна, вторая, третья, четвертая, шестая, седьмая и восьмая группы входов которого являются соответственно шестой, седьмой, восьмой, девятой, десятой и одиннадцатой установочными шинами сплайн-интерполятора, пятая группа входов блока формирования коэффициентов сплайна является информационной шиной сплайн-интерполятора, а девятая группа выходов соединена с адресными входами второго блока памяти, первая, вторая, третья, четвертая, пятая и шестая группы выходов которого соединены со вторыми группами входов соответственно первого, второго, третьего, четвертого, пятого и шестого умножителей, а вход управления второго блока памяти соединен с восьмым выходом блока управления, десятый выход которого соединен со входами управления счетчика и регистра, а одиннадцатый выход блока управления соединен со входом управления сумматора и шестым входом блока формирования параметров сплайна, первая, вторая и третья группы входов которого являются соответственно двенадцатой, тринадцатой и четырнадцатой установочными шинами сплайн-интерполятора, четвертая группа входов блока формирования параметров сплайна соединена с выходами первого блока памяти, а седьмая, восьмая, девятая, десятая, одиннадцатая и двенадцатая группы выходов соединены с первыми группами входов соответственно первого, второго, третьего, четвертого, пятого и шестого умножителей, выходы которых соединены соответственно с первой, второй, третьей, четвертой, пятой и шестой группами информационных входов сумматора, выходы которого соединены с информационными входами регистра, выходы которого являются выходной шиной сплайн-интерполятора, причем блок формирования коэффициентов сплайна выполнен содержащим первый, второй, третий, четвертый, десятый, одиннадцатый и тринадцатый умножители, первый, второй, третий, четвертый, пятый, шестой, двенадцатый и тринадцатый элементы задержки, первый, второй и четвертый сумматоры, причем первая группа входов первого умножителя объединена с первыми группами входов второго, третьего и четвертого умножителей, группами информационных входов первого, третьего, шестого и тринадцатого элементов задержки, первой группой информационных входов второго сумматора и одновременно соединена с пятой группой входов блока формирования коэффициентов сплайна и информационной шиной сплайн-интерполятора, вторая группа входов первого умножителя соединена со второй группой входов блока формирования коэффициентов сплайна и шестой установочной шиной сплайн-интерполятора, а выходы первого умножителя соединены с группой информационных входов второго элемента задержки, выходы которого соединены со второй группой информационных входов первого сумматора, первая группа информационных входов которого соединена с выходами первого элемента задержки, третья группа информационных входов первого сумматора соединена с выходами третьего элемента задержки, а выходы соединены с первой группой входов десятого умножителя, вторая группа входов которого соединена с третьей группой входов блока формирования коэффициентов сплайна и седьмой установочной шиной сплайн-интерполятора, а выходы десятого умножителя соединены с группой информационных входов двенадцатого элемента задержки, выходы которого соединены с первой группой информационных входов четвертого сумматора, вторая группа информационных входов которого соединена с выходами тринадцатого элемента задержки, вторая группа входов одиннадцатого умножителя соединена с седьмой группой входов блока формирования коэффициентов сплайна и десятой установочной шиной сплайн-интерполятора, а первая группа входов одиннадцатого умножителя соединена с выходами второго сумматора, вторая группа информационных входов которого соединена с выходами второго умножителя, третья группа информационных входов соединена с выходами четвертого элемента задержки, третий умножитель, соединенный с четвертым элементом задержки, предназначен для формирования слагаемого для второго сумматора, вторая группа входов третьего умножителя соединена с четвертой группой входов блока формирования коэффициентов сплайна и восьмой установочной шиной сплайн-интерполятора, четвертая группа информационных входов второго сумматора соединена с выходами пятого элемента задержки, группа информационных входов которого соединена с выходами четвертого умножителя, вторая группа входов которого объединена со второй группой входов второго умножителя и шестой группой входов блока формирования коэффициентов сплайна и девятой установочной шиной сплайн-интерполятора, а пятая группа информационных входов второго сумматора соединена с выходами шестого элемента задержки, вход управления которого объединен со входами управления первого, второго, третьего, четвертого, пятого, двенадцатого и тринадцатого элементов задержки, входами управления первого, второго и четвертого сумматоров и одновременно соединен с первым входом блока формирования коэффициентов сплайна, первая группа входов тринадцатого умножителя соединена с выходами четвертого сумматора, вторая группа входов тринадцатого умножителя соединена с восьмой группой входов блока формирования коэффициентов сплайна и одновременно одиннадцатой установочной шиной сплайн-интерполятора, а выходы тринадцатого умножителя соединены с девятой группой выходов блока формирования коэффициентов сплайна, отличающийся тем, что в блок формирования коэффициентов сплайна дополнительно введены пятый, шестой, седьмой, восьмой, девятый и двенадцатый умножители, седьмой, восьмой, девятый, десятый, одиннадцатый и четырнадцатый элементы задержки и третий сумматор, причем вторая группа входов пятого умножителя объединена со второй группой входов девятого умножителя и десятой группой входов блока формирования коэффициентов сплайна и одновременно пятнадцатой установочной шиной сплайн-интерполятора, а выходы пятого умножителя соединены со второй группой информационных входов третьего сумматора, третья группа информационных входов которого соединена с выходами седьмого элемента задержки, группа информационных входов которого соединена с выходами шестого умножителя, вторая группа входов которого объединена со второй группой входов восьмого умножителя и одиннадцатой группой входов блока формирования коэффициентов сплайна и одновременно шестнадцатой установочной шиной сплайн-интерполятора, четвертая группа информационных входов третьего сумматора соединена с выходами восьмого элемента задержки, группа информационных входов которого соединена с выходами седьмого умножителя, вторая группа входов которого соединена с двенадцатой группой входов блока формирования коэффициентов сплайна и семнадцатой установочной шиной сплайн-интерполятора, пятая группа информационных входов третьего сумматора соединена с выходами девятого элемента задержки, группа информационных входов которого соединена с выходами восьмого умножителя, шестая группа информационных входов третьего сумматора соединена с выходами десятого элемента задержки, группа информационных входов которого соединена с выходами девятого умножителя, седьмая группа информационных входов третьего сумматора соединена с выходами одиннадцатого элемента задержки, первая группа информационных входов третьего сумматора объединена с первыми группами входов пятого, шестого, седьмого, восьмого и девятого умножителей, информационными входами одиннадцатого элемента задержки и соединена с первой группой входов четвертого умножителя, выходы третьего сумматора соединены с первой группой входов двенадцатого умножителя, вторая группа входов которого соединена с тринадцатой группой входов блока формирования коэффициентов сплайна и восемнадцатой установочной шиной сплайн-интерполятора, а выходы двенадцатого умножителя соединены с четвертой группой информационных входов четвертого сумматора, третья группа информационных входов которого соединена с выходами четырнадцатого элемента задержки, группа информационных входов которого соединена с выходами одиннадцатого умножителя, а вход управления четвертого сумматора объединен со входами управления седьмого, восьмого, девятого, десятого, одиннадцатого и четырнадцатого элементов задержки и входом управления третьего сумматора.

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| Интерполятор | 1986 |

|

SU1405074A1 |

| Сплайн-интерполятор | 1989 |

|

SU1686461A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

| US 5666437 A, 09.09.1997. | |||

Авторы

Даты

2001-09-20—Публикация

1999-06-15—Подача