(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ТИРИСТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования тиристора | 1983 |

|

SU1091190A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU936352A1 |

| Способ управления стабилизированным выпрямителем с емкостным фильтром на выходе | 1986 |

|

SU1376196A1 |

| Стабилизированный источник питания | 1983 |

|

SU1096627A1 |

| Устройство для моделирования вентильных преобразователей | 1983 |

|

SU1137491A1 |

| Устройство для моделирования @ -фазного управляемого выпрямителя | 1980 |

|

SU959105A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство для моделирования импульсного датчика частоты вращения | 1985 |

|

SU1251118A2 |

| Устройство для моделирования механической передачи | 1982 |

|

SU1091192A2 |

| Устройство управления приводом балансировочного стенда | 1982 |

|

SU1118962A2 |

1

Изобретение относится к вычислительной технике и предназначено для моделирования тиристора - основного элемента многофазного вентильного преобразователя.

Известны устройства для моделирования вентильного преобразователя,содержащее сумматор-интегратсф с двумя диодами и резистором в цепи обратной связи 1.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее суммирующий интегратср, компаратор, интегратор с включенными контактами реле во входной цепи и цепи обратной связи, суммирующий усилитель и два реле 2}

Недостатками указанного устройства являются значнтельнбя ин ционность, невозможность получения одинакового времени включения, сложность и ненадежность в работе. . ,

Цель изобретения - повышение быстродействия устройства и егр надежности в работе.

Для достижения поставленной цели в устройство для моделирования тиристора, содержащее суммирующий интегратор, первый и Второй входы которого соответственно являются первым и вторым входами устройства, компаратор, первый вход которого является третьим входом устройства, и ограничительные диоды, дополнительно введены три масщтабирующнх

Q резистора, одни выводы которых соответственно являются четвертым, пятым и щестым входами устройства, а другие выводы масщтабирующих резисторов соединены с катодом первого ограничитель15 ного диода, анод которого соединен со вторым входом компаратора, выход кото. . рого соединен с третьим входом суммирующего интегратора, выход которого соединен с третьим входом компаратора,

20 причем эыход суммирующего интегратора через второй ограничительный диод сое-даней со своим четвертым входом.

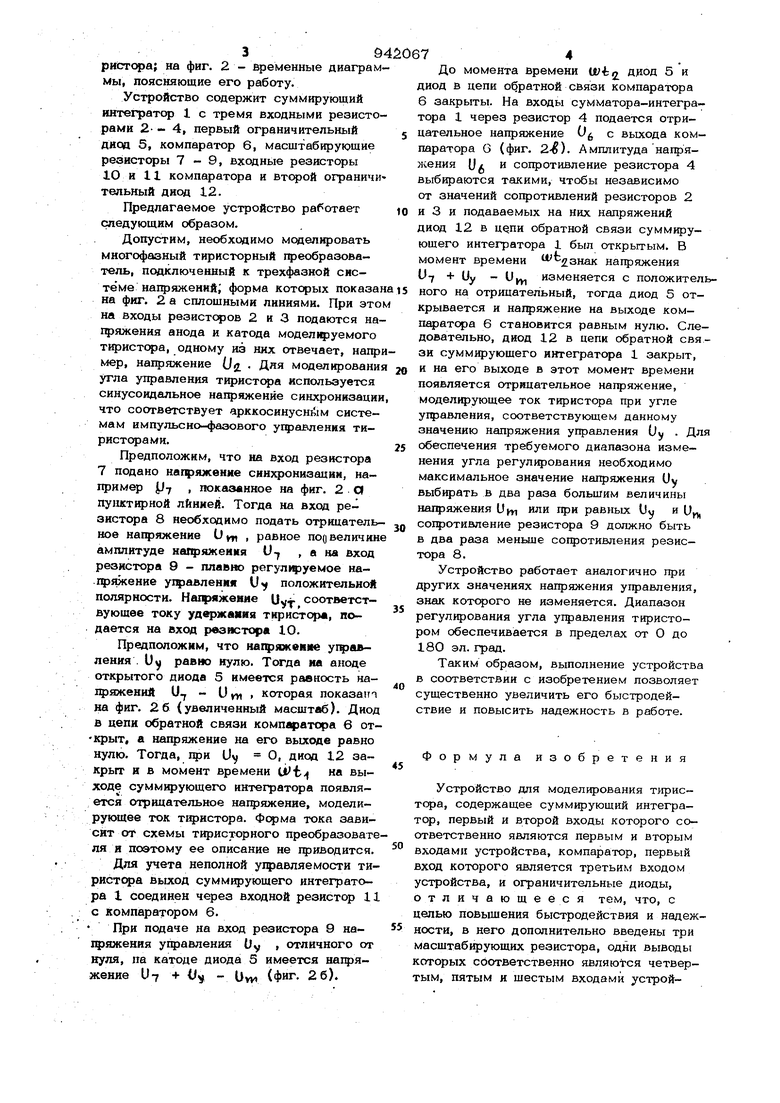

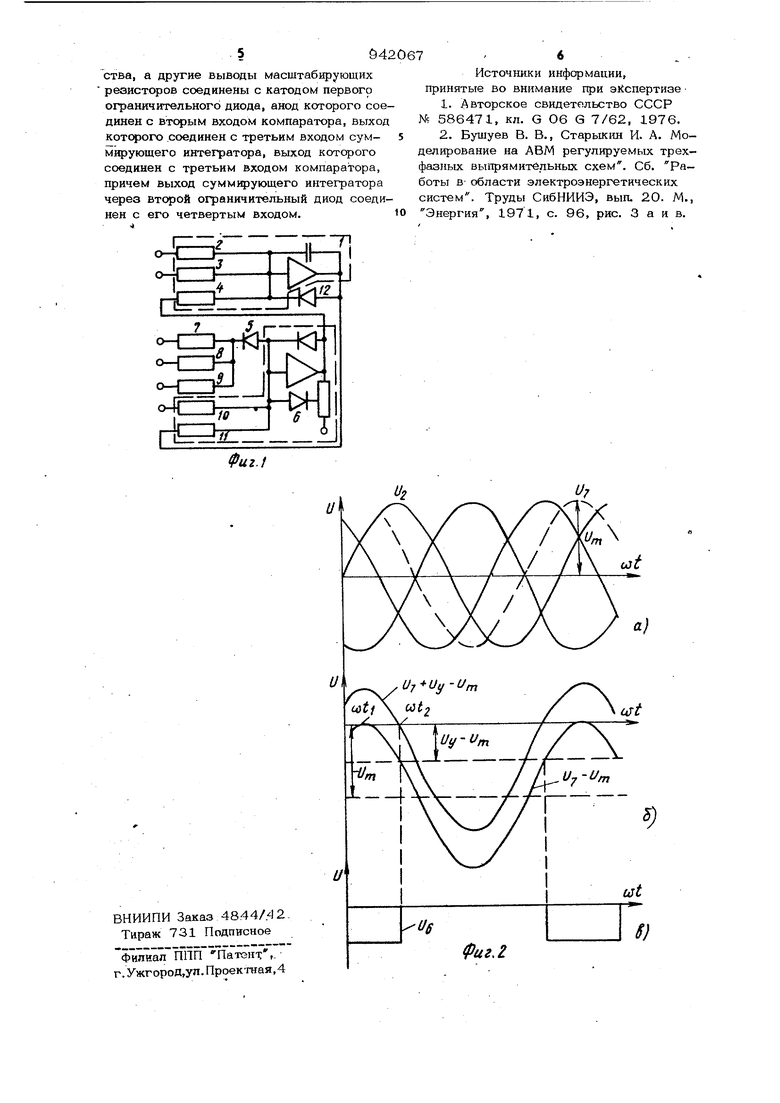

На фиг. 1 приведена фугжционяльная схема ус1ройства для моделирования тиристс а; на фиг. 2 - временные диаграм мы, поясняющие его работу. Устройство содержит суммирующий интегратор 1 с тремя входными резисторами 2- - 4, первый ограничительный диоа 5, компаратор 6, масштабирующие резисторы 7-9, входные резисторы 10 и И компаратора и второй ограничи тельный диод 12. Предлагаемое устройство работает следующим образом. Допустим, необходимо моделировать многофазный тиристорный преобразователь, подключенный к трехфазной системе напряжений; форма которых показа на фиг. 2 а сплошными линиями. При это на входы резисторов 2 и 3 подаются на1фяжения анода и катода модел эуемого тиристора, одному из них отвечает, нагф мер, напряжение (Jji Для моделировани угла управления тиристсра используется синусоидальное напряжение синхронизации что соответствует арккосинуснйм системам импульсно-фазового угравления тиристорами. Предположим, что на вход резистора 7 подано нагфяжение синхронизации, например Jf , гюказанное на фиг. 2 О ПУ1ЦСТ1ФНОЙ линией. Тогда на вход резистора 8 необходимо подать отрицательнов на1фяжение 0, , равное под величин амплитуде на|фяжеи|1я а на вход резистора 9 - плавно регул чзуемое напряжение управления U положительной полярности. Напряжение Uy-r соответствующее току удержания тиристора, подается на вход рванстора 10. Предположим, что нагфяжемие управления . и у равно нулю. Тотцй иа аноде открытого диода 5 имеется равность напряжений 0 - и , которая показа гт на фиг. 26 (увеличенный масштаб). Диод в цепи обратной связи компл атора 6 открыт, а напряжение на его выходе равно нулю. Тогда, 1ФИ О, диод 12 закрыт и в момент времени U-fc-f на выходе сумм|фующего интегратора появляется отрицательное напряжение, моделирующее ток Т1фистора. Форма тока зависит от схемы тиристорного преобразовате ля и поэтому ее описание не 1чэиводится. Для учета неполной ухфавляемости тиристора выход суммирующего интегратора 1 соединен через входной резистор 11 с компаратором 6. При подаче на вход резистора 9 наЩ)яжения управления Uy , отличного от нуля, па катоде диода 5 имеется напряжение U7 + - фиг. 26). До момента времени (jyi диод 5 и иод в цепи обратной связи компаратора 6 закрыты. На входы сумматора-интегратора 1 через резистор 4 подается отрицательное напряжение 0 с выхода компаратора О (фиг. 2-S). Амплитуда нагряжения и 1 и сопротивление резистора 4 выбираются такими, чтобы независимо от значений согфотивлений резисторов 2 и 3 и подаваемых на них напряжений диод 12 в цепи обратной связи суммируюшего интегратора 1 был открытым. В момент времени напряжения U7 + Uy - Uj изменяется с положительного на отрицательный, тогда диод 5 открывается и нагфяжение на выходе компаратора 6 становится равным нулю. Следовательно, диод 12 в цепи обратной связи суммирующего интегратора 1 закрыт, и на его выходе в этот момент времени появляется отрицательное напряжение, моделирующее ток тиристора при угле угравления, соответствующем данному значению напряжения управления Оу . Для обеспечения требуемого диапазона изменения угла регулирования необходимо максимальное значение напряжения (Jy выбирать в два раза большим величины налряжения Ujti или при равных Uy и Оу сопротивление резистора 9 должно быть в два раза меньше сопротивления резистора 8. Устройство работает аналогично при других значениях напряжения управления, знак которого не изменяется. Диапазон регул{фования угла управления тиристором обеспечивается в пределах от О до 180 эл. град. Таким образом, выполнение устройства в соответствии с изобретением позволяет существенно увеличить его быстродействие и повысить надежность в работе. Формула изобретения Устройство для моделирования тиристора, содержащее суммирующий интегратор, первый и второй входы которого соответственно являются первым и вторым входами устройства, компаратор, первый вход которого является третьим входом устройства, и ограничительные диоды, отличающееся тем, что, с целью повышения быстродействия и надежности, в него дополнительно введены три масщтабирующих резистора, одни выводы которых соответственно являются четвертым, пятым и шестым входами устрой

Авторы

Даты

1982-07-07—Публикация

1980-09-03—Подача