(Б ) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Система бесперебойного питания | 1990 |

|

SU1807546A1 |

| Устройство для определения одномерных начальных моментов К-го порядка случайного сигнала | 1983 |

|

SU1108464A1 |

| Цифровой фазометр | 1985 |

|

SU1308935A1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| Агрегат гарантированного питания | 1990 |

|

SU1742942A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Электромагнитный расходомер | 1987 |

|

SU1578481A1 |

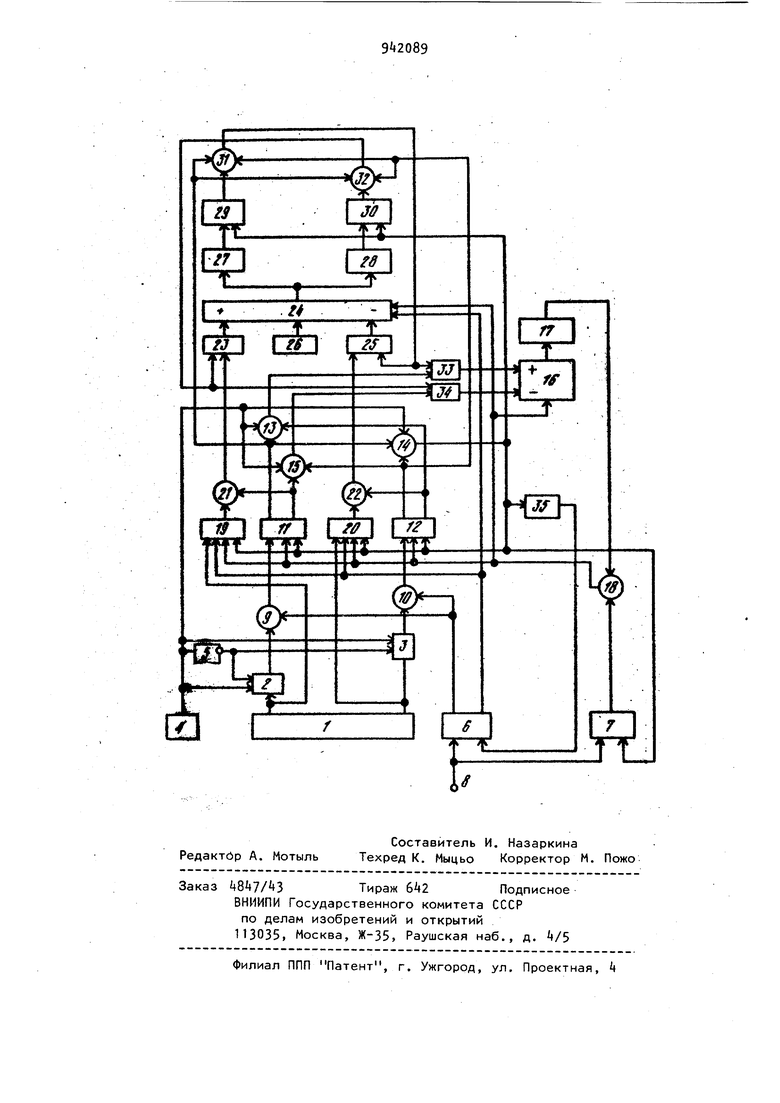

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с циф ровым вычислительным устройством. Известны преобразователи угла поворота вала в код, содержащие многотактный генератор импульсов, первый выход которого через последовательно соединенные делитель частоты, бло питания, фазовращатель и компаратор подключен к блоку элементов И, другие входы которого соединены с выходами разрядов делителя частоты, другие выходы генератора импульсов подключены к триггерам, выходы которых подключены к дешифратору, соединенному с выходом компаратора, а выходы дешифратора подключены к шифратору 1 J. Недостатком известного преобразователя является значительная noi- решность формирования выходных импульсов компаратора и погрешность дискретности. Известны также преобразователи, которые содержат фазовращатель, подключенный к двум компараторам, генератор импульсов, выход которого через счетчик подключен к генератору пилообразного напряжения, выход которого подключен к другим входам компараторов, выходы компараторов подключены к измерителю временных интервалов интегрирующего типа . Недостаток известного преобразователя - погрешность смещения границ временных интервалов относительно импульсов высокой частоты. Наиболее близким к предлагаемому по технической сущности является преобразователь угла поворота вала в код, содержащий блок преобразования угла поворота в последовательность временных интервалов, первый и второй триггеры, единичные входы которых соединены с источником команды Пуск, единичный выход первого триггера подключен к одним вхо дам первого и второго элементов И, выходы которых подключены к единичным входам третьего и четвертого триггеров соответственно, единичный выход третьего триггера подключен к первым вводам третьего и четвертого элементов И, единичный выход четвер того триггера подключен к второму входу четвертого и к первому входу пятого элементов И нулевые выходы третьего и четвертого триггеров под ключены к вторым входам третьего и пятого элементов И, третьи входы которых подключены к выходу генератора импульсов, выход четвертого эл мента И подключен к нулевым входам второго, третьего и четвертого три|- геров и через счетчик к нулевому вх ду первого триггера, выходы разрядо реверсивного счетчика через дешиф.ратор подключены к одному входу шес того элемента И, другой вход которого соединен с единичным выходом второго триггера, а выход подключен к нулевым входам третьего и четвертого триггеров и реверсивного счетчика. Выходы блока преобразования .у угла поворота в последовательность временных интервалов подключены к другим входам первого и второго эле ментов И соответственно, а выходы третьего и пятого элементов И подключены соответственно к входам сложения и вычитания реверсивного счетчика ГЗ 1. Недостатком известного преобразователя является погрешность, вызванная дискретным измерением каждог из временных интервалов как при случайном, так и регулярном расположении границ временных интервалов относительно импульсов генератора. Цель изобретения - повышение точ ности преобразователя. Поставленная цель достигается тем, что в преобразователь угла поворота вала в код, содержащий блок преобразования угла поворота в последовательность временных интервалов, первый и второй триггеры, единичные входы которых соединены с ис точником команды Пуск, J единичный выход первого триггера подключен к одним входам первого и второг элементов И, выходы которых подключены к единичным входам третьего и Э4 четвертого триггеров соответственно, единичный выход третьего тригге-i ра подключен к первым входам третьего и четвертого элементов,И, единичный выход четвертого триггера подключен к второму входу четвертого и первому входу пятого элементов И, нулевые выходы третьего и четвертого триггеров подключены к вторым входам третьего и пятого элементов И, третьи входы которых подключены к выходу генератора импульсов, выход четвертого элемента И подключен к нулевым входам второго, третьего и четвертого триггеров и через счетчик к нулевому входу первого триггера, выходы разрядов реверсивного счетчика через дешифратор подключены к одному входу шестого элемента И, другой вход которого соединен с единичным выходом второго триггера, а выход подключен к нулевым входам третьего и четвертого триггеров и реверсивного счетчика, введены два блока синхронизации, пятый, шестой, седь-. мой и восьмой триггеры, седьмой, восьмой, девятый и десятый элементы И, четыре элемента ИЛИ, инвертор, источник эталонного напряжения, интегратор и два компаратора, выходы блока преобразования угла поворота в последовательность временных интервалов подключены к единичным входам пятого и шестого тригге-ров и к первым входам одного и другого блоков синхронизации соответственно, вторые и третьи входы блоков синхронизации соединены непосредственно и через инвертор с выходом генератора импульсов, а выходы блоков синхронизации подключены к другим входам первого и второго элементов И соответственно, единичный выход пятого триггера подключен к седьмому элементу И, другой вход которого соединен с нулевым выходом третьего триггера, а виход через первый элемент ИЛИ подключен к прямому входу интегратора, единичный выход шестого триггера подключен к восьмому элементу И, другой вход которого соединен с нулевым выходом четвертого триггера, а выход через второй элемент ИЛИ подключен к инверсному входу интегратора, опорный вход которого соединен с источником эталонного напряжения, а выход подключен к входам коммпараторов, выходы компараторов подключены к единичным входам седьмого и восьмого три геров, единичные выходы которых под ключены к Одним входам соответстве но девятого и десятого элементов И выход девятого э яемента И через второй элемент ИЛИ подключен к инверсному входу интегратора, а выход десятого элемента И через первый элемент ИЛИ подключен к прямому вхо ду интегратора, выходы третьего и девятого элеме 1тов И через третий элемент ИЛИ подключены к входу сложения реверсивного счетчика, выходы пятого и десятого элементов И ч рез четвертый элемент ИЛИ подключе ны к входу вычитания реверсивного счетчика, выход генератора импульсов подключен к третьему входу чет вертого элемента И, выход четверто го элемента И подключён к нулевым входам пятого, шестого, седьмого и восьмого триггеров, выход шестого элемента И подключен к нулевым входам пятого и шестого три|- герое и к нулевому входу интегратора, нулевой выход первого тригге ра подключен к нулевым входам пято го и шестого триггеров и к нулевому входу интегратора, а единичные выходы третьего и четвертого триггеров подключены к другим входам девятого и десятого элементов И. На чертеже представлена блок-схе ма преобразователя. Преобразователь содержит блок 1 преобразования угла поворота в последовательность временных интервалов, выходы которого подключены к блокам 2 и 3 синхронизации, генератор k импульсов, выход которого непосредственно и через инверТор 5 подключен к другим входам блоков 2 и 3. Единичные входы первого и второго триггеров 6 и 7 соединены с источником 8 команды Пуск. Единичный выход триггера 6 подключен к одним входам первого и второго элементов И 9 и 10, другие входы которых соединены с выходами блоков 2 и 3 а выходы подключены к единичным входам третьего и четвертого триггеров 11 и 12. Единичный выход триггера 11 подключен к первым входам третьего и четвертого элементов И 13 и 1, единичный выход триггера 12 подключен к второму входу эле мента И 1 и к первому входу пятого 96 элемента И 15. Выходы разрядов реверсивного счетчика 16 через дешифратор 17 подключены к одному входу шестого элемента И 18, другой вход которого соединен с единичным выходом триггера 7. Выходы блока 1 подключены к единичным входам пятого и шестого триггеров 19 и 20, единичные выходы которых подключены к одним входам седьмого и восьмого элементов И 21 и 22. Нулевой выход тригге ра 11 подключен к второму входу элемента И 15 и к другому входу элемента И 21, выход которого через первый элемент ИЛИ 23 подключен к прямому входу интегратора 2, Нулевой выход триггера 12 подключен к второму входу элемента И 13 и к другому входу элемента И 22, выход которого через второй элемент ИЛИ 25 подключен к инверсному входу ратора 2. Опорный вход интегратора 24 соединен с источником 2б эталонного напряжения, а выход интегратора 2 подключен к компараторам 27 и 28, выходы которых подключены к единичным входам седьмого и восьмого три1- геров 29 и 30. Единичные выходы триггеров 29 и 30 подключены к одним входам девятого и десятого элементов И 31 и 32. Выход элемента И 31 через элемент ИЛИ 25 подключен к инверсному входу интегратора 24, а выход элемента И 32 через элемент ИЛИ 23 подключен к прямому входу интегратора 24. Вы- ход генератора 4 подключен к третьим входам элементов И 13, 14 и 15Выходы элементов И 13 и 3 через третий элемент ИЛИ 33 подключены к входу сложения реверсивного счетчика 1б, а выходы элементов И 15 и 32 через четвертый элемент ИЛИ 34 подключены к входу вычитания реверсивного счетчика 16. Выход элемента И 14 подключен к нулевым входам триггеров 7,11,12,19,20,29 и 30, а через счетчик 35 к нулевому входу триггера 6. Выход элемента 18 подключен к нулевому входу интегратора 24 и к нулевым входам триггеров 11, 12, 19, 20 и реверсивного счетчика 16. Нулевой выход триггера 6 подключен к нулевым входам триггеров 19 и 20 и к нулевому входу интегратора 24, а единичные выходы триггеров 11 и 12 подключены к другим входам элементов 31 и 32. Преобразователь работает следующим образом. На выходах блока 1 формируется периодическая последовательность временных интервалов, пропорциональ ных измеряемому углу поворота и oi- раниченная старт- и стоп- импульсами. На выходе генератора k формируется последовательность тактовых импульсов высокой частоты со скважностью 2. С выходов генератора k и инвертора 5 на синхронизирующие вхо ды блоков 2 и 3 поступают две последовательности тактовых импульсов. На выходе блока 2 формируются старт импульсы синхронно с тактовыми импу сами инвертора 5 а на выходе блока 3 - стоп-импульсы, синхронно с тактоцыми импульсами этого же инвертора 5. По сигналу Пуск с источника 8 снимается сигнал установки О с триггеров 19 и 20 и интегратора 2k и производится установка триггеров 6 и 7 в состояние 1 открываются элементы 9 и 10, пропуская синхронизированные старт- и стоп- импульсы на единичные входы тригегров 11 и 12 соответственно. Если первым по ле сигнала Пуск приходит стартимпульс, то открывается элемент 13 пропуская импульсы генератора 4 на вход сложения реверсивного счетчика 16 до момента поступления стопимпульса, который, производя устано ку триггера 12 в состояние 1, закрывает элемент 13 и открывает элемент 1. Задний фронт выходного сигнала элемента 14, отстоящий от переднего фронта стоп-импульса на один период сигнала генератора ус танавливает триггеры 11 и 12 в состояние О. При этом содержимое счетчика 35 числа измерений в цикле увеличивается на 1. На выходе элемента 21 формируется временной интервал между передним фронтом старт-импульса с блока 1 и передним фронтом засинхронизированного старт-импульса с выхода элемента 9. В течение этого временного интервала интегратор производит интегрирование опорного напряжения источника 26 с положительным знаком. На выходе элемента 22 формируется временной интервал между передним фронтом стоп-импульса с | блока 1 и передним фронтом засинхронизированного стоп-импульса с выхода элемента 10. В течение этого временного интервала интегратор 24 производит интегрирование опорного напряжения с отрицательным знаком. Если первым приходит стоп-импульс то открывается элемент 15 и импульсы генератора 6 поступают на вход вычитания реверсивного счетчика 16 до момента поступления старт-импульса. При этом содержимое счетчика 35 также увеличивается на 1. Интегратор 24 производит, также как и в предыдущем случае, интегрирование опорного напряжения между передними фронтами стоп-импульсов с выходов блока 1 и элемента 10с отрицательным знаком, а между передними фронтами старт-импульсов с выхода блрка 1 и элемента 9 с положительным знаком. С приходом следующих старт- и стоп-импульсов к содержимому реверсивного счетчика 16 добавляется очередная пачка импульсов с выходов элементов 13 или 15, к содержимому счетчика 35 добавляется единица, а на выходе интегратора 24 изменяется напряжение с учетом суммарной погрешности измерения концов временных интервалов. Как только выходное напряжение интегратора 24 превысит эталонный уровень (например, равный кванту;, то срабатывает один из компараторов 27 или 28 в зависимости от знака выходного напряжения. Соответствующий триггер 29 или 30 устанавливается в состояние 1 и открывает элемент 31 или. 32. I Триггеры 11 и 12 одновременно находятся в состоянии 1 в течение периода следования импульсов генератора 4. Если выходное напряжение интегратора 24 превышает положительный эталонный уровень, то импульс с элемента 31, равный по длительности периоду следования импульсов генератора 4, поступает на инверсный вход интегратора 24 и на вход сложения реверсивного счетчика 1б. Интегратор 24 производит интегрирование опорного напряжения с отрицательным знаком в течение периода следования импульсов генератора 4. Аналогичным образом работает преобразователь при превышении выходным напряжением интегратора 24 эталонного отрицательного уровня. При этом импульс коррекции поступает на вход вычитания реверсивного счет чика 16. Задним фронтом выходного сигнала элемента 14 триггеры 29 и 30 устанавливаются в О, Так продолжается до переполнения счетчи ка 35, после чего триггеры.6, 19, 20 и интегратор 2 устанавливаются в О, элементы 9 и 10 закрываются, цикл измерения заканчивается. Выходы разрядов реверсивного сче чика 16 подключены к дешифратору 17 на выходе которого формируется сигнал, когда содержй1 1ое реверсивного счетчика 16 превышает половину полного значения фазы одного измерения в цикле. Этот сигнал необходим для анализа длительности временного интервала в начале цикла-измерений. Если первый временной интервал превышает половину полного значения фазы, то выходной сигнал элемента 18 производит установку триггеров 11, 12, 19 и 20 и интегратора 2k в состояние О, а содержимое счетчика 35 не изменяется. При этом сле дующий временной интервал меньше половины полного значения фазы и преобразователь начинает цикл измерения. Первый входной импульс счетчика 35 производит установку три|- гера 7 в состояние О, закрывая эл мент 18. Предлагаемый преобразователь ав томатически исключает погрешность перехода через полное значение фазы в процессе цикла измерения. Путем точного измерения концов временных интервалов в предлагаемом преобразователе практически исключается погрешность дискретности. Формула изобретения Преобразователь угла поворота вала в код, содержащий блок преобр зования угла поворота в последовательность временных интервалов, пе вый и второй триггеры, единичные входы которых соединены с источник команды Пуск, единичный выход пе вого триггера подключен к одним вх дам первого и второго элементов И, выходы которых подключены к единич ным входам третьего и четвертого 910 триггеров соответственно, единичный выход третьего триггера подключен к первым входам третьего и четвертого элементов И, единичный выход четвертого триггера подключен к второму входу четвертого и первому входу пятого элементов И, нулевые выходы третьего и четвертого триггеров подключены к вторым входам третьего и пятого элементов И, третьи входы которых подключены к выходу генератора импульсов, выход четвертого элемента. И подключен к нулевым входам второго, третьего и четвертого триггеров и через счетчик - к нулевому входу первого триггера, выходы разрядов реверсивного счетчика через дешифратор подключены к одному входу шестого элемента И, другой вход которого соединен с единичным выходом второго триггера, а выход подключен к нулевым входам третьего и четвертого триггеров и реверсивного счетчика, отличающийся тем, что, с целью повышения точности преобразователя, в него введены два блока синхронизации, пятый, шестой, седьмой и восьмой триггеры, седьмой, восьмой, девятый и десятый элементы И, четыре элемента ИЛИ, инвертор, источник эталонного напряжения, интегратор, и два компаратора, выходы блока преобразования угла поворота в последовательность временных интервалов подключены к единичным входам пятого и шестого триггеров и к первым входам одного и другого блоков син- хронизации соответственно, вторые и третьи входы блоков синхронизации соединены непосредственно I и через инвертор с выходом генератора импульсов, а выходы блоков синхронизации подключены к другим входам первого и второго элементов И соответственно, единичный выход пятого триггера подключен к седьмому элементу И, другой вход которого соединен с нулевым выходом третьего триггера, а выход через первый элемент ИЛИ подключен к прямому входу интегратора, единичный выход шестого триггера подключен к восьмому элементу И, другой вход которого соединен с нулевым выходом четвертого триггера, а выход через второй элемент ИЛИ подключен к инверсному входу интегратора, опорный вход коToporo соединен с источником эталонного напряжения, а выход подключен к входам компараторов, выходы компараторов подключены к единичным входам седьмого и восьмого триггеров, единичные выходы которых подключены к одним входам соответственно девятого и десятого элементов И, выход девятого элемента И через второй элемент ИЛИ подключен к инверсному входу интеграторе, а выход десятого элемента И через первый элемент ИЛИ подключен к прямому входу интегратора, выходы третьего и девятого элементов через третий элемент ИЛИ подключены к входу сложения реверсивного счетчика, выходы пятого и десятого элементов И через четвертый элемент ИЛИ.подключены к входу вычитания реверсивного счетчика, выход генератора импульсов подключен к третьему входу четвертого элемента И, выход которого

подключен к нулевым входам пятого, шестого, седьмого и восьмого триггеров, выход шестого элемента И подключен к нулевым входам пятого и шестого триггеров и к нулевому входу интегратора, нулевой выход первого триггера подключен к нулевым входам пятого и шестого триггеров и к нулевому входу интегратора, а единичные выходы третьего и четвертого триггеров подключены к другим входам девятого и десятого элементов И.

Источники 1«1нформации, принятые во внимание при экспертизе

Н., Энергия, 1978. с. 181, рис.6.

Авторы

Даты

1982-07-07—Публикация

1980-09-15—Подача