Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛА | 2012 |

|

RU2498343C1 |

| Устройство для контроля качества канала связи с шумоподобными сигналами | 1989 |

|

SU1628210A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Устройство для контроля надежности изделий | 1983 |

|

SU1164737A2 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1990 |

|

SU1781642A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1107315A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

Изобретение относится к технике связи Цель изобретения - повышение точности синхронизации. Устройство содержит два перемножителя, четыре переключателя, восемь интеграторов, пять блоков памяти, двенадцать квадраторов, десять сумматоров, r-р гармонических колебаний, г-р такто- вых импульсов, блок добавления и вычитания, делитель частоты, два дешифр- тора, шесть накопителей, вычислитель тактового сдвига, два блока формирования сигналов готовности и инвертор. Цель достигается за счет осуществления коррекции тактовых меток приемника и передатчика путем вычитания или добавления импульсов в гребенке импульсов г-ра тактовых импульсов. 4 ил

Изобретение относится к технике связи и может быть использовано в аппаратуре передачи данных

Цель изобретения - повышение точности синхронизации.

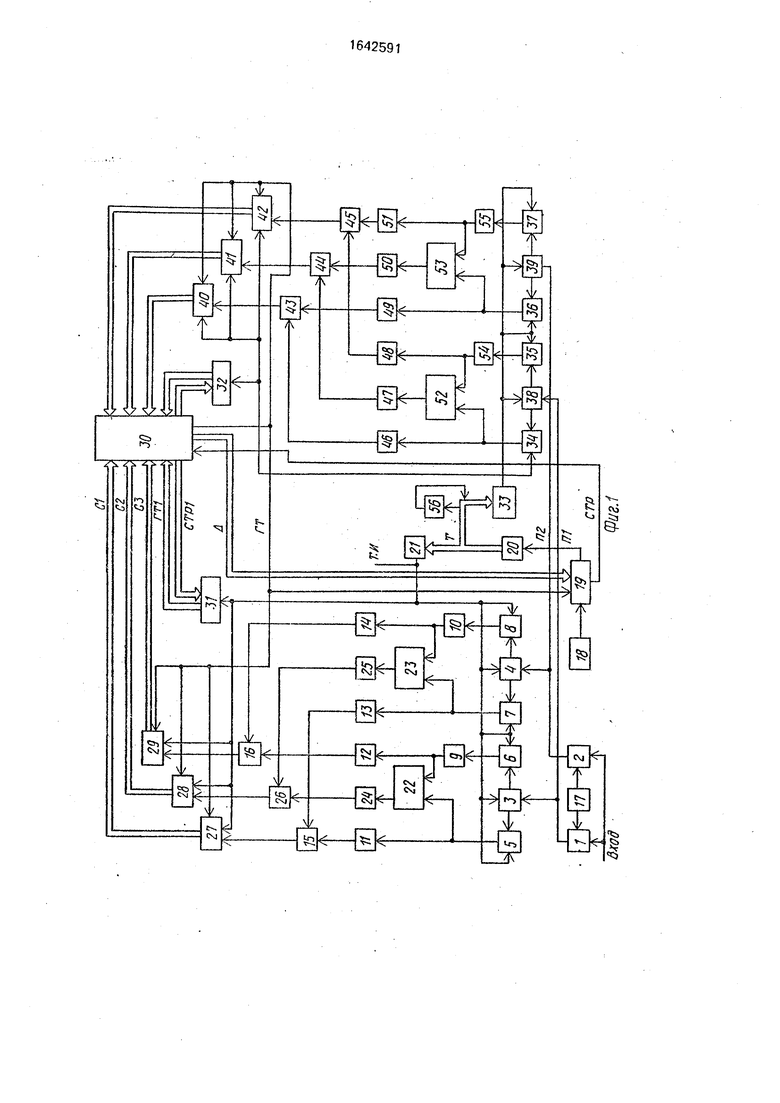

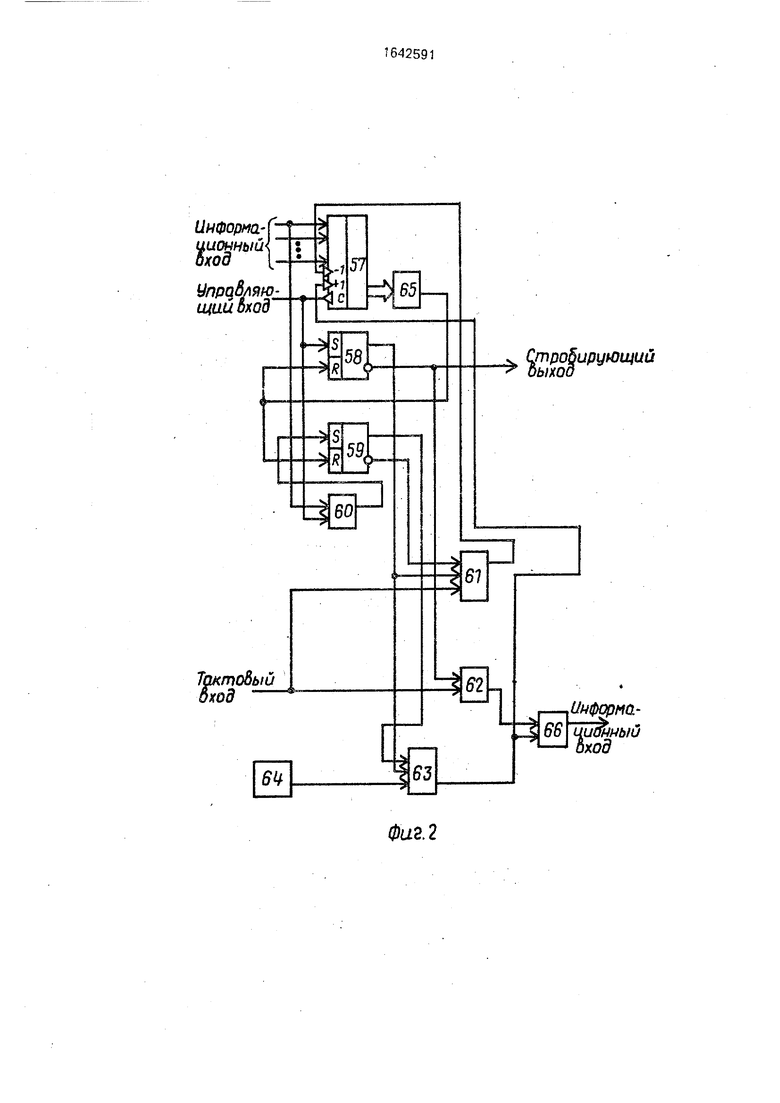

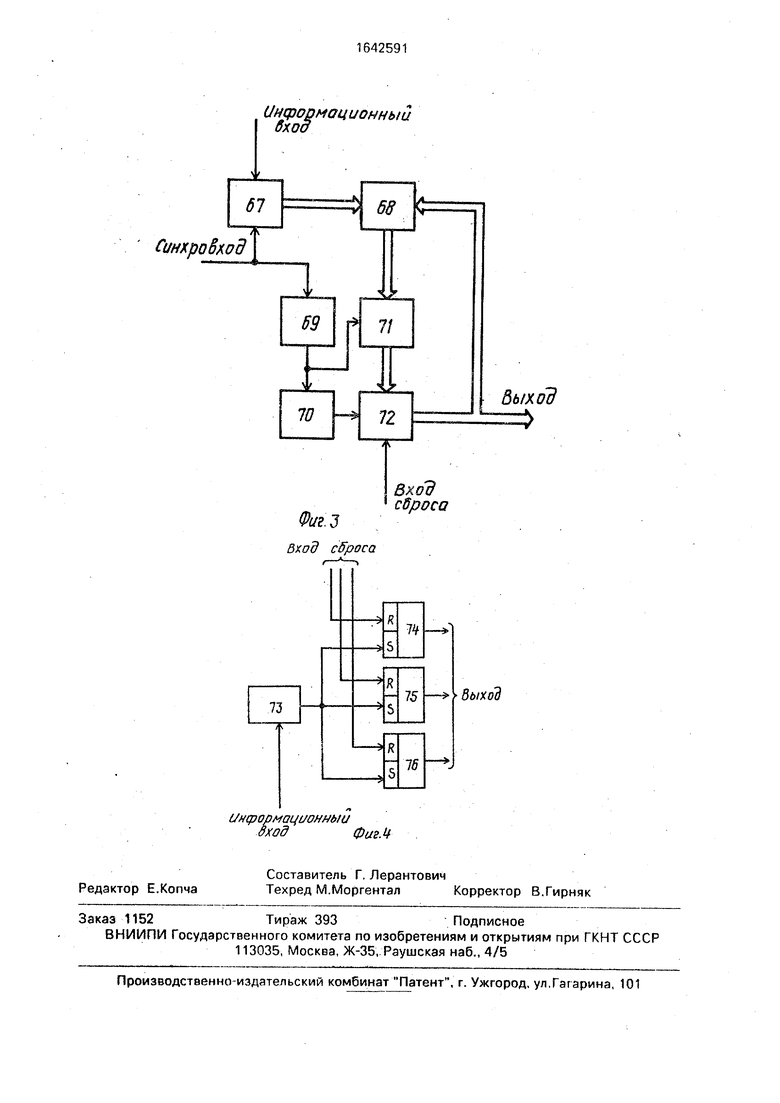

На фиг.1 представлена структурная электрическая схема устройства для тактовой синхронизации; на фиг.2 - схема блока добавления и вычитания; на фиг.З - схема накопителя; на фиг.4 - схема блока формирования сигналов готовности.

Устройство для тактовой синхронизации содержит первый 1 и второй 2 перемножители, первый 3 и второй 4 переключатели, первый 5, второй 6, третий 7 и четвертый 8 интеграторы, первый 9 и второй 10 блоки памяти, первый 11. второй 12, третий 13 и четвертый 14 квадраторы, первый 15 и второй 16 сумматоры, генератор 17 гармонических колебаний, генератор 18 тактовых импульсов, блок 19 добавления и вычитания, делитель 20 частоты, первый дешифратор 21, третий 22 и четвертый 23 сумматоры, пятый 24 и шестой 25 квадраторы, пятый сумматор 26, первый 27, второй 28 и третий 29 накопители, вычислитель 30 тактового сдвига, первый 31 и второй 32 блоки формирования сигналов готовности, второй дешифратор 33, пятый 34, шестой 35, седьмой 36 и восьмой 37 интеграторы, третий 38 и четвертый 39 переключатели, четвертый 40. пятый 41 и шестой 42 накопители, шестой 43, седьмой 44 и восьмой 45 сумматоры, седьмой 46, восьмой 47, девятый 48, десятый 49, одиннадцатый 50 и двенадцатый 51 квадраторы, девятый 52 и десятый 53 сумматоры, третий 54 и четвертый 55 блоки памяти, инвертор 56.

Блок 19 добавления и вычитания содержит реверсивный счетчик 57, первый 58 и второй 59 триггеры, первый 60, второй 61, третий 62 и четвертый 63 элементы И, генератор 64 импульсов, дешифратор 65 нулевой комбинации, элемент ИЛИ 66,

сь

4 Ю СП

чэ

Накопитель 27 (28, 29, 40-42) содержит аналого-цифровой преобразователь (АЦП).67, сумматор 68, первый 69 и второй 70 элементы задержки, первый 71 и второй 72 регистры. Блок 31 (32) формирования сигналов готовности содержит счетчик 73; первый 74, агорой 75 и третий 76 триггеры.

Устройство для тактовой синхронизации работает следующим образом.

Сигнал подается на первые (информационные) входы первого 1 и второго 2 пере- миожителей, на вторые входы которых поступают соответственно синфазный и квадратурный гармонические сигналы с выходов генератора 17 гармонических колебаний, Полученные таким образом на выходах первого 1 и второго 2 перемножителей сигналы поступают на информационные входы первого 3 и второго4 переключателей, которые по тактовым сигналам с первого дешифратора 21 коммутируют их на первый 5 и третий 7 или на второй 6 и четвертый 8 интеграторы соответственно. Пря этом коммутация на второй 6 и четвертый 8 интеграторы осуществляется во время первой

половины каждого j-ro тактового интервала,

ч т.е. от (I - 1) Т до 0 - -тр) Т а нз первый 5 и

третий 7 интеграторы - во время второГ. псловины каждого j-ro тактового интервала,

т.е. от (j -кг) Т до j Т. Сброс напряжения,

накопленного интеграторами, осуществляется также тактовыми сигналами с первого дешифратора 21. При этом накопленные значения напряжения перед моментом сброса на выходах второго 6 и четвертого 8 интеграторов имеют вид

) т

U 2j -1 /S (t) А sin (о t dt;

(-1)Т

0-т)

U2|-r1 /

(J-1)T

где S(t) - входной сигнал;

А - амплитуда сигнала.

На выходах первого 5 и третьего 7 интеграторов, напряжения имеют вид |.т .

U 2) JS (t) А sin ut dt;

т

S (t ) А cos (О t dt

О Т

u2j -

04)

S (t ) A cos CD t dt.

Сигналы с выходов второго 6 и четвертого 8 интеграторов задерживаются на время Т/2 в первом 9 и втором 10 блоках памяти и в момент т j Т одновременно с

сигналами с выходов первого 5 и третьего 7 интеграторов поступают на входы квадраторов 12, 14, 11 и 13 соответственно. После возведения этих сигналов в квадрат первым

15 и вторым 16 сумматорами з конце каждого j-ro тактового интервала формируются сигналы соответственно:

Cij U2j2 + V2J2; C3j U2J-12 + V2j-i2.

Сигналы с выходов первого интегратора 5 и первого блока 9 памяти складываются третьим сумматором 22, после чего возводятся в квадрат пятым квадратором 24. Сигналы с выходов третьего интегратора 7 и

второго блока 10 памяти аналогично складываются четвертым сумматором 23 и возводятся в квадрат шестым квадратором 25. Таким образом, на выходе пятого сумматора 26 имеет место сигнал

C2j-(U2j- + U2j}2 + (V2j-l + V2j)2.

Сигналы Cij, C2, Caj поступают на информационные входы соответствующих на-.

копителей 28, 27 и 29, т.е. на аналоговые входы АЦП 67. По тактовым импульсам с выхода первого дешифратора 21 эти сигналы преобразуются в параллельный код, который поступает на первый вход сумматора

68 накопителя, а на второй его вход поступает параллельный код с выхода второго регистра 72. При этом второй регистр 72 в начальный момент времени обнулен импульсом, поступившим на его вход сброса с

выхода готовности вычислителя 30 тактового сдвига. Импульсом, задержанным первым элементом 69 задержки, параллельный код с выхода сумматора 68 накопителя записывается в первый регистр 71, з импульсом с выхода второго элемента задержки - во второй регистр 72. Время задержки первого элемента задержки 69 чуть больше времени срабатывания сумматора 68 накопителя. Время задержки второго злементо 70 задержки чуть больше времени срабатывания первого регистра 71, Таким образом, через N тактов на выходах первого 27, второго 28 и третьего 29 накопителей будут присутствовать сигналы вида

JJ

Си :

C2J ;

1 1 5J

Сз

1 1

соответственно, которые поступят на соответствующие информационные входы вычислителя 30,тактового сдвига. Число N длительность накопления статистик для коррекции тактового сдвига, выбирается исходя из требований к точности синхронизации. Импульсы с выхода первого дешифратора 21 поступают на счетный вход счетчика 73 первого блока31 формирования сигналов готовности. По достижении зтим счетчиком числа N он обнуляется и на его выходе переполнения формируется импульс, которым первый 74, второй 75 и третий 76 триггеры первого блока 31 формирования сигналов готовности устанавливаются в единичное состояние Высокий потенциальный уровень, поступая на соотвесттвующий разряд первой группы входов готовности вычислителя 30 тактового сдвига (шина Требование А соответствующего входного интерфейса микроЭВМ), инициализирует ввод соответствующей величины (Ci, €2 или Сз). Цикл ввода заканчивается выдачей вычислителем 30 тактового сдвига на соответствующем разряде первой группы стробирующих выходов (шина Ввод данных соответствующего входного интерфейса микроЭВМ) положительного импульса, которым обрасываеся по входу R соответствующий триггер (74, 75 или 76) первого блока 31 формирования сигналов готовности.Таким образом,обеспечивается считывание в вычислитель 30 тактового сдвига величин Ci, C2 и Сз с выходов соответствующих накопителей 27, 28 и 29 один раз за N тактов.

Второе плечо устройства, состоящее из второго блока 32 формирования сигналов готовности, второго дешифратора 33, пятого 34, шестого 35, седьмого 36 и восьмого 37 интеграторов, третьеп 38 и четвертого 39 переключателей, четвертого 40, пятого 41 и шестого 42 накопителей, шестого 43, седьмого 44 и восьмого 45 сумматоров, седьмого 46, восьмого 47, девятого 48, десятого 49, одиннадцатого 50 и двенадцатого 51 квадраторов, девятого 52 и десятого 53 сумматоров, третьего 54 и четвертого 5Ь блоков памяти, аналогично формирует величины Si, Sa и 5з с тем различием, что сигналы на выходе первого 21 и второго 33 дешифраторов сдвинуты друг относительно друга на время Т/2. Указанный сдвиг возникает вследствие того, что старший разряд параллельного кода с выхода делителя 20 частоты, поступающий на вход второго дешифратора, инвертируется инвертором 56, а это при коэффициенте деления К 21 означает сдвиг на половину периода.

После ввода всех шести величин d, €2, Сз, Si, 82, Зз микроЭВМ вычислителя 30 тактового сдвига по формуле

, ,,Nr - 2С2 + 4С3 ,

(Ч| mod К.

2МГ -4(С2 -С3 -Ci)J еглиСз +01 - С2 S3 + S2 - Si

г .

I -..-2

2МГ l(S2 -83 -Si)

| mod К

5

иначе вычисляет тактовый сдвиг Д где Е энергия сигнала По окончании вычислений микроЭВМ анализирует состояние строби- рующего входа вычислителя 30 тактового сдвига (шина Требование Б выходного интерфейса микроЭВМ) Присутствие на этом

5 входе высокого логического уровня свидетельствует о том что блок 19 добавления и вычитания импульсов готов к приему очередного значения А, В этом случае микро- ЭВМ помещает значение Д на шины

0 информационного выхода вычислителя 30 тактового сдвига а также формирует положительный импульс на выходе готовности вычислителя 30 тактового сдвига (шина Вывод данных выходного интерфейса микро5 ЭВМ). Этот импульс, поступая на входы сброса накопителей 27-29, 40-42 обнуляет в каждом из них второй регистр 72 и, кроме того, устанавливает в единичное состояние триггер 58 и своим задним фронтом записы0 вает величину Ав реверсивный счетчик 57, который имеет I log2K разрядов.

Если старший разряд величины тактового сдвига равен нулю, то тактовые метки приемника опережают тактовые метки пе5 редатчика и, следовательно, из гребенки импульсов с выхода генератора 18 тактовых импульсов следует вычесть Димпульсов. Если старший разряд величины тактового сдвига равен 1, то тактовые метки приемни0 ка отстают от тактовых меток передатчика. Необходимо добавить К-Димпульсов. Такого рода коррекция осуществляется следующим образом.

Пусть старший разряд величины Д равен 1. В этом случае импульс с выхода готовности вычислителя 30 тактового сдвига, пройдя через открытый первый элемент И 60, установит второй триггер 59 в единичное состояние. Тем самым четвертый элемент И

® 63 открывается для прохождения импульсов с генератора 64 импульсов блока 19 добавления и вычитания импульсов. Указанные импульсы поступают через элемент ИЛИ 66 на информационный выход блока 19 добавления и вычитания, а также на вход сложения реверсивного счетчика 57. При его обнулении на выходе дешифратора 65 нулевой комбинации появится положительный перепад, который сбросит первый 58 и второй 59 триггеры При этом четвертый эле- мг нт И 63 закроется, а третий элемент И 62 откроется. Таким образом, поскольку счетчик 57 имеет емкость К, к импульсам генератора 18 тактовых импульсов добавится пачка из К- Л импульсов с.выхоДа генератора 64 импульсов. Высокий, логический уровень на стробирующем выходе блока 19 добавления и вычитания импульсов свидетельствует о том, что указанный блок готов к приему очередного значения А.

В случае нулевого старшего разряда величины, Д второй триггер 59 останется в нулевом состоянии, а первый триггер 58 установится в единичное состояние сом с управляющего входа блока 19 добавления и вычитанид импульсов. При этом второй элемент И 61 будет открыт для прохождения импульсов с генератора 18 тактовых импульсов на вход вычитания реверсивною счетчика 57. При обнулении реверсивного счетчика 57 на выходе дешифратора 65 нулевой комбинации сформирует- ся положительный фронт, которым сбросится первый триггер 58, в результате чего откроется третий элемент И 62. таким образом, vs гребенки импульсов генератора 18 будет вычтено Дммяульсов.

С выхода делителя 20 частоты парал- код поступает на вход первого дешифратора 21, импульсы на выходе которого представляют собой выходные тактовые импульсы устройства.

Формула изобретения Устройство для тактовой синхронизации, содержащее первый и второй перемножители, первые входы которых объединены и являются информационным входом устройства, а также генератор гармонических колебаний, первый и второй входы которого подключены к вторым входам соответственно первого и второго перемножителей, выходы которых подключены к информационным входам первого и второго переключателей, при этом первый и второй выходы первого переключателя подсоединены к информационным входам соответственно первого и второго интеграторов, к входам сброса которых, а также к входам сЗроса третьего и четвертого интеграторов и к управляющим входам первого и второго переключателей подключен выход первого дешифратора, а первый и второй выходы второго переключателя подключены к информационным входам соответственно третьего и четвертого интеграторов, причем выход первого интегратора через первый квадратор подключен к первому входу первого сумматора, выход второго интегратора через последовательно соединенные первый блок памяти и второй квадратор подключен к первому входу второго сумматора,

выход третьего интегратора через третий квадратор подключен к второму входу первого сумматора, а выход четвертого интегратора через последовательно соединенные второй блок памяти и чет0 вертый квадратор подключен к второму входу второго сумматора, при этом выход генератора тактовых импульсов подключен к тактовому входу блока добавления и вычитания, выход которого подключен к счетно5 му входу делителя частоты, группа выходов которого подклюиена к группе входов пер- аого дешифратора, а также третий сумматор и инвертор, отличающееся тем, что. с целью повышения точности синхронизации,

0 введены четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый сумматоры, пятый, шестой, седьмой восьмой, девятый, десятый, одиннадцатый и двенадцатый квадратооы, третий и четвертый перед

5 ключатели, пятый, шестой, седьмой и восьмой интеграторы, второй дешифратор, третий v четвертый блоки памяти, первый, еторой, третий, четвертый, пятый и шестой накопители, первый и второй блоки рования сигналов готовности и вычислитель тактового сдвига, к стробирующему входу которого подключен стробирующий выход добавления п вычитания, к группе информационных входов которого подключе5 на группа информационных выходов вычислителя тактового сдвига, выход готовности которого подключен к управляющему зходу блока добавления и вычитания и входам сброса первого, втооого, третьего, чет0 вертого, пятого и шестого накопителей, при этом выходы интегратора и первого блока памяти подключены к первому и второму третьрго сумматора4, а выход третьего интегратора it второго блока памя5 ти подключены к первому и второму входам четвертого сумматора, причем выходы третьего и четвертого сумматоров соответственно через пятый и шестой квадраторы подключены к первому и второму входам

0 пятого сумматора, а выходы перво о, пятого и второго сумматоров подключены к информационным входам соответственно первого, второго и третьего накопителей, к синхровходам которых и информационному

5 входу первого блока формирования сигналов готовности подключен выход первого дешифратора, являющийся выходом устройства, а выходы первого, второго и третьего накопителей подключены к первому, второму и третьему информационным входам вычислителя тактового сдвига, первая и вторая группы выходов стробирующих импульсов которого подключены к группам входов сброса соответственно первого и второго блоков формирования сигналов го- товности, группы выходов которых подключены соответственно к первой и второй группам входов готовности вычислителя тактового сдвига, к четвертому, пятому и шестому информационным входам которо- го подключены выходы соответственно четвертого, пятого и шестого накопителей, к синхровходам которых, информационному входу второго блока формирования сигналов готовности, входам сброса пятого, шее- того, седьмого и восьмого интеграторов, управляющим входам третьего и четвертого переключателей подключен выход второго дешифратора, к разрядным входам которого, кроме старшего разрядного входа, под- ключены соответственно выходы разрядов делителя частоты, выход старшего разряда которого через инвертор подключен к старшему разрядному входу второго дешифратора, при этом выходы первого и второго перемножителей подключены к информационным входам соответственно третьего и четвертого переключателей, причем первыг- и второй выходы третьего переключателя подсоединены к информационным входам соответственно пятого и шестого интеграторов, а первый и второй выходы четвертого переключателя подсоединены к информационным входам соответствен но седьмого и восьмого интеграторов, при этом выход пятого интегратора подключен к первому входу девятого сумматора и через седьмой квадратор к первому входу шестого сумматора, выход которого подключен к информационному входу четвертого-накопителя, выход шестого интегратора чеоез третий блок памяти подключен к второму входу девятого квадратора и к второму входу девятого сумматора, выход которого через восьмой квадратор подключен к первому входу седьмого сумматора, выход которого подключен к информационному входу пятого накопителя, выход седьмого интегратора подключен к первому входу десятого сумматора и через десятый квадратор к второму входу шестого сумматора, а выход восьмого интегратора через четвертый блок памяти подключен к входу двенадцатого квадратора и второму входу десятого сумматора, выход которого через одиннадцатый квадратор подключен к второму входу седьмого сумматора, при этом выходы девятого и двенадцатого квадраторов подключены соответственно к первому и второму входам восьмого сумматора, выход которого подключен к информационному входу шестого накопителя.

о ю см т

СО

Qoxg

s

со «чэ

Ц1

O

g

I

мационныи

Синхроёход

ФигЗ

Вход сброса

дь/xol

Вход сброса

г Выход

| Устройство для тактовой синхронизации | 1984 |

|

SU1305885A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-04-15—Публикация

1989-06-08—Подача