(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СКОЛЬЗЯЩЕГО СРЕДНЕЮ СЛУЧАЙНЫХ ПРОЦЕССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения свертки двух функций | 1984 |

|

SU1218397A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для определения момента разладки случайных процессов | 1985 |

|

SU1260973A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Многоканальное устройство для вычисления модульной функции | 1982 |

|

SU1115062A1 |

| Устройство для формирования информативных признаков при распознавании образов | 1986 |

|

SU1361592A1 |

| Устройство для возведения в квадрат чисел, представленных в унитарном коде | 1980 |

|

SU920715A1 |

1

-1- .

Изобретение относится к вычислитепьной технике и может быть испопьзовано для обработки случайных процессов путем их скользящего сглаживания в реальном масштабе бремени.

Известно устройство дпя опредёпения скользящего среднего случайного процесса, содержащее входной блок, ключи, схемы ИЛИ, генератор импульсов, реверсив- ю ный счетчик, счетчик разности, счетчик делитель и триггер .

Недостатком данного устройства явпя- ется низкое быстродействие, обусловленное наличием реверсивного счетчика, ра- ботаюшего дважды на интервале одного измерения. Кроме того, известное устройство характеризуется сло;1.постью и громоздкостью конструкции..

Наиболее близким по техническому ре-20 шению является устройство для определения скользящего среднего случайного про- цесса, содержащее формирователь унитарных сигналов L2j,

Известные устройства характеризуются низким быстродействием вычисления , скользящего среднего, что не позволяет сглаживать случайные процессы в реальном масштабе времени. Это обусловлено наличием реверсивного счетчика, работающего дважды на один цикл вычисления, что приводит к снижению быстродействия вычисления скользящего среднего. При этом быстродействие, определяемое суммарным временем переключений, производимых в счетчике над унитарными кодами текущих отсчетов на один такт вычисления скользящего сред-, него, равно 2- 2 t j где t - время переключения элемента счетчика; k - разрядность - двоичного кода, представляющего результат иа лерения входных отсчетов.:

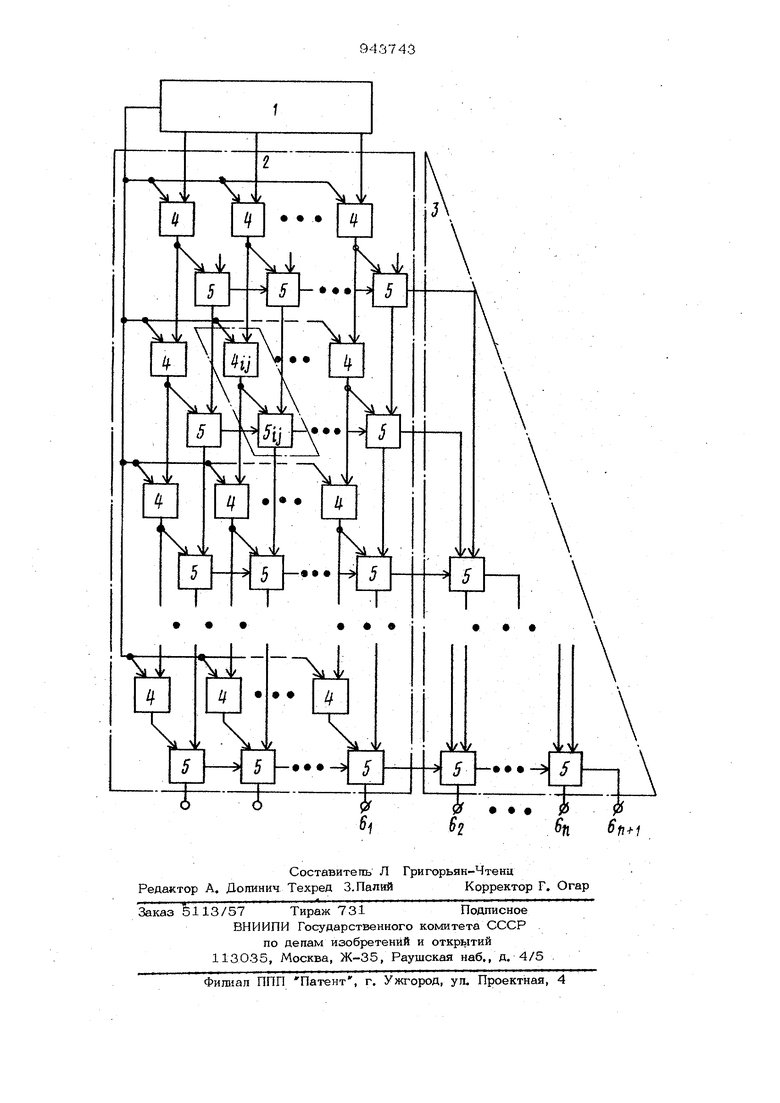

Кроме того, известные устройства характеризуются неоднородностью структуры, что усложняет технологию его изготовления в кще микроэлектронной схемы. Цепью изобретения является повышение б)ыстродействия и однородности струк туры устройства. Поставпенная цепь достигается тем, что в устройство для определения скопь зящего среднего случайных процессов введены однородная вычислительная среда и многоканапьный преобразователь унитарных сигналов в двоичный код, выходы которого совместно с выходами вычислительной среды являются выходами устройства, а входы преобразователя пора; ядно подключены к соответствующим выходам вычислительной среды, тактовый вход которой подключен к первому выходу формирователя унитарных сигналов, другие выхсяы которого поразрядно подключены к соответствующим информацион ным входам вычислительной среды, причем каждый ( i, )-й элемент (-( 2,3, ..., j S 2, 3, ..., k ) однородной вычислительной среды содержит полный дво ичный сумматор, тактируемый R S -триггер, 5 - вход которого подключен к пря мому выходу триггера ( -1, j )-го эле мента среды, С-вход соединен с первым выходом формирователяунитарных сигналов, первый вход сумматора подключен к выходу состояния сумматора (-i-l, j )-го элемента среды, второй вход подключен к прямому выходу триггера (-ij )-го элемента среды, третий вход подключен к выходу переноса сумматора (н,5-1)го элемента среды, а выход состояния сумматора подключен к первому входу сумматора (1 4- 1,1 )-го элемента среды. Кроме того, с целью упрощения операции деления однородная вычислительна среда содержит 2 (П 2, 3, ...) рядов элементов, а выходами устройства являются выходы элементов 2 -го ряда вычислительной среды, начиная с k -го разряда и выходы многоканального прео разователя унитарных сигналов в двоичный код. Функциональная схема устройства представлена на чертеже. Устройство содержит формирователь унитарных сигналов 1, однородную вычис лительную среду 2, многоканальный преобразователь унитарных сигналов в двоичный код 3, тактируемые RS-триггера 4, полные двоичные сумматоры 5. Устройство работает следующим образом. Обработка результатов измерений путем определения скользящего среднего происходит за один такт работы устройства. В начале каждого такта работы на первом выходе входного устройства формируется короткий импульс, по фронту нарастания которого происходит сдвиг информации, хранимой в вычислительной среде 2, т.е. двоичные состояния триггеров 4 каждого ()i )-го элемента вычислительной среды 2 присваиваются R 5 -триггеру 4 соответствующего (-i + 1, j )-го элемента среды. Пт. этом в элементы 4 вычислительной среды 2 первого ряда (-( 1, ) заносятся результаты текущего измерения с выходов входного устройства 1, а состояние триггеров 4 элементов вычислительной среды 2 (2 , j ) ряда стирается. Таким образом, после выполнения операций сдвига в вычислительной соеде 2 на выходах устройства / являющихся выходами многоканального преобразователя унитарных сигналов в двоичный код 3 и выходами элементов последнего 2 -го ряда вычислительной среды 2 (начиная с k -го разряда), получаем код скользящего среднего. Число рядов вычислительной среды целесообразно выбирать равным 2, что позволяет упростить операцию деления и реализовать ее путем отбрасывания всех разрядов последнего ряда вычислительной среды, включая k -1 разряд. Многоканальный преобразователь унитарных сигналов в двоичный код построен на полных двоичных сумматорах и имеет однородную структуру, что вместе с вычислительной средой, которая также имеет однородную структуру, повышает однородность структуры устройства. Устройство по сравнению с другими известными устройствами, содержащими реверсивный счетчик, позволяет на интервале времени одного такта работы входного устройства (например, выполняющего операцию измерения и аналого-цифрового преобразования сигналов) получ ть двоичный код текущего среднего с высоким быстродействием. Формула изобретения Устройство для определения скользящего среднего случайных процессов, содержащее формирователь унитарных сигналов, отличающееся тем, что, с целью повыщения быстродействия и однородности структуры устройства, оно содержит однородную вычислительную среду и многоканальный преобразователь унитарных сигналов в двоичный код, при этом входы преобразоватепя унитарных сигналов в двоичный код поразрядно подключены к соответствующим выходами вычислительной среды, управпя ющий вход которой подключен к первому выходу формиромтеля унитарных сигналов, другие выходы которого поразрядно подключены к соответствующим информационным входам вычислительной среды, причем каждый (,1 )-4 элемент (-(«2, 3, ..., , } гч2, 3,..., k ) однородной нычис1штепьной среды содержит полный двоичный сумматор и тактируемый RSтриггер, S - выход которого подключен к прямому выходу триггера {л -1, j )-го элемента среды, С г входы триггеров объединены и являются управляющим входом вычислительной среды, 5 -входы триггеров первого ряда являются информациоНными входами вычислительной среды, первый вход сумматора (4,5 )-го элемента среды подключен к выходу суммы сумматора ( -1 j )-го элемента средыi второй вход сумматора подключен к прямому выходу Tj irrepa(i,j )-го элемента вычислительной срелы, третий вход сумматора (л,, i )-го э лемента вычиспительной среды подключен к выхооу переноса сумматора (1) 3 -1 )-го элемента вычислительной срерзл, выходами устройства являются выходы элементов ряда ш 1числительнсЛ среды начиная с k -го разряда и выхода многоканального преобразоватепя унитарных сигналов в двоичный код.

Источники информации, принятые во внимание при экспертизе

N9 438016, кп. Q Об Р 15/36, 1974.

Авторы

Даты

1982-07-15—Публикация

1978-08-15—Подача