Изобретение откосится к измеритель ной технике и может использоваться для преобразования одиночных аналоговых сигналов последовательно-парйл- лельным методом и .большого числа аналоговых сигналов методом поразрядного уравновешивания с цифровой коммутацией каналов.

Целью изобретения является расширение функциональных возможностей за счет увеличения числа преобразуемых сигналов.

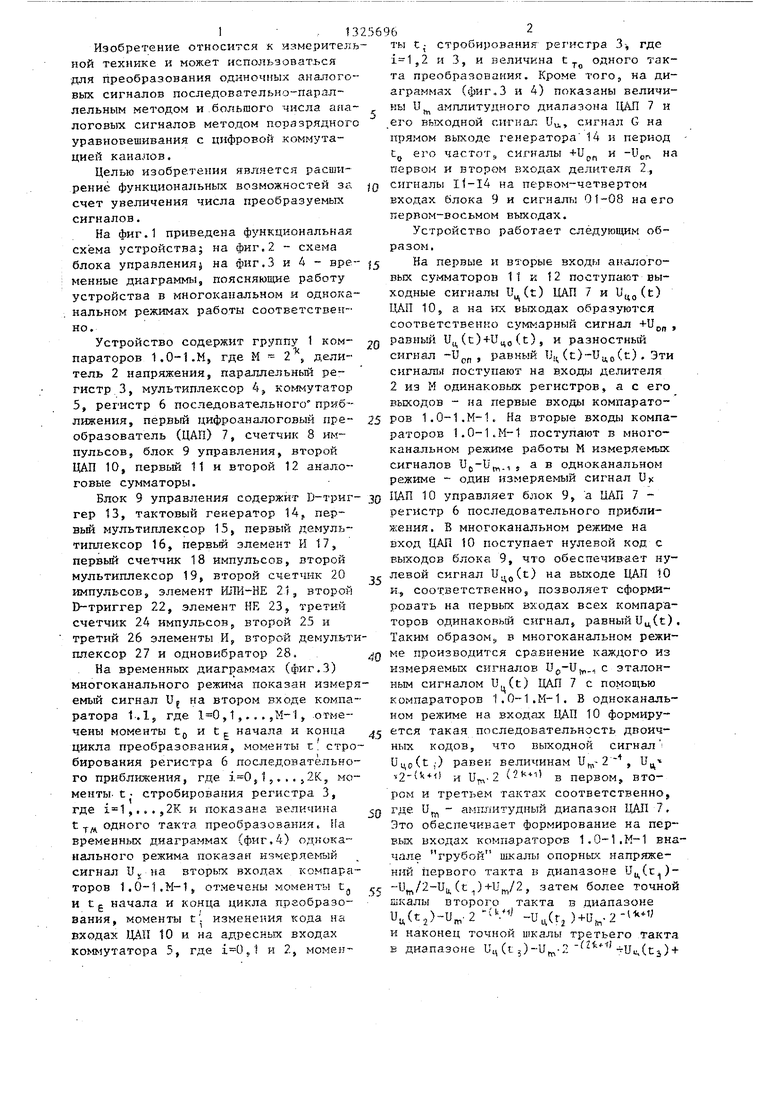

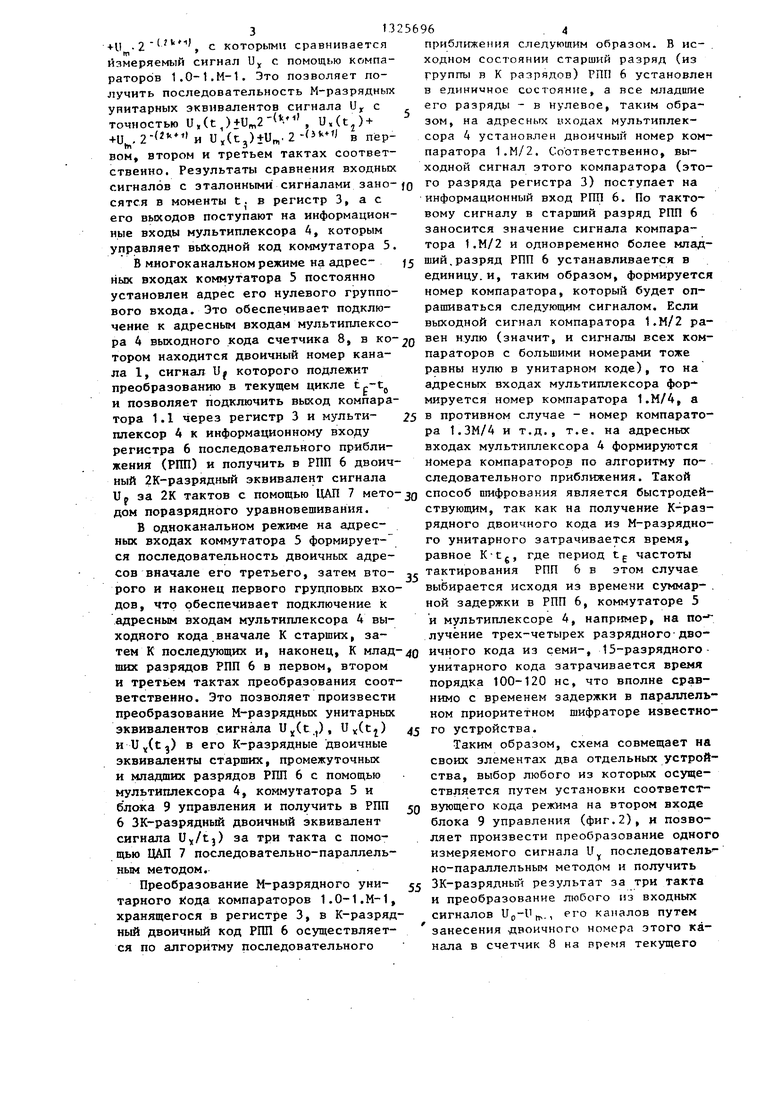

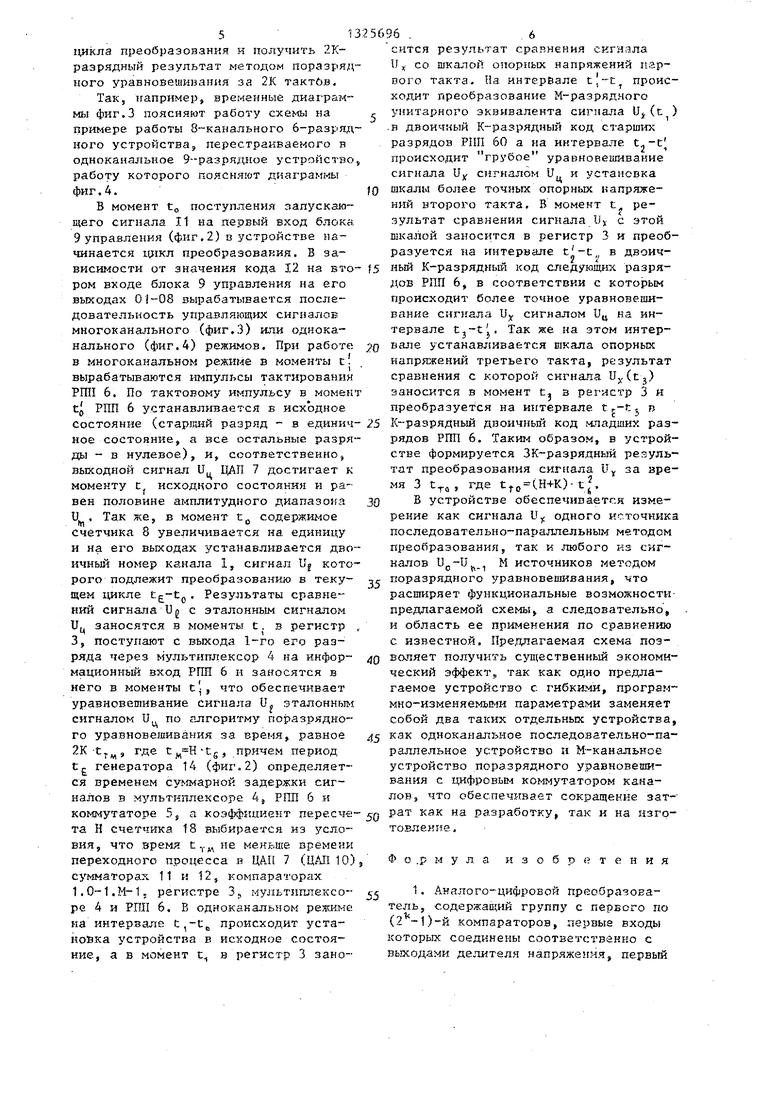

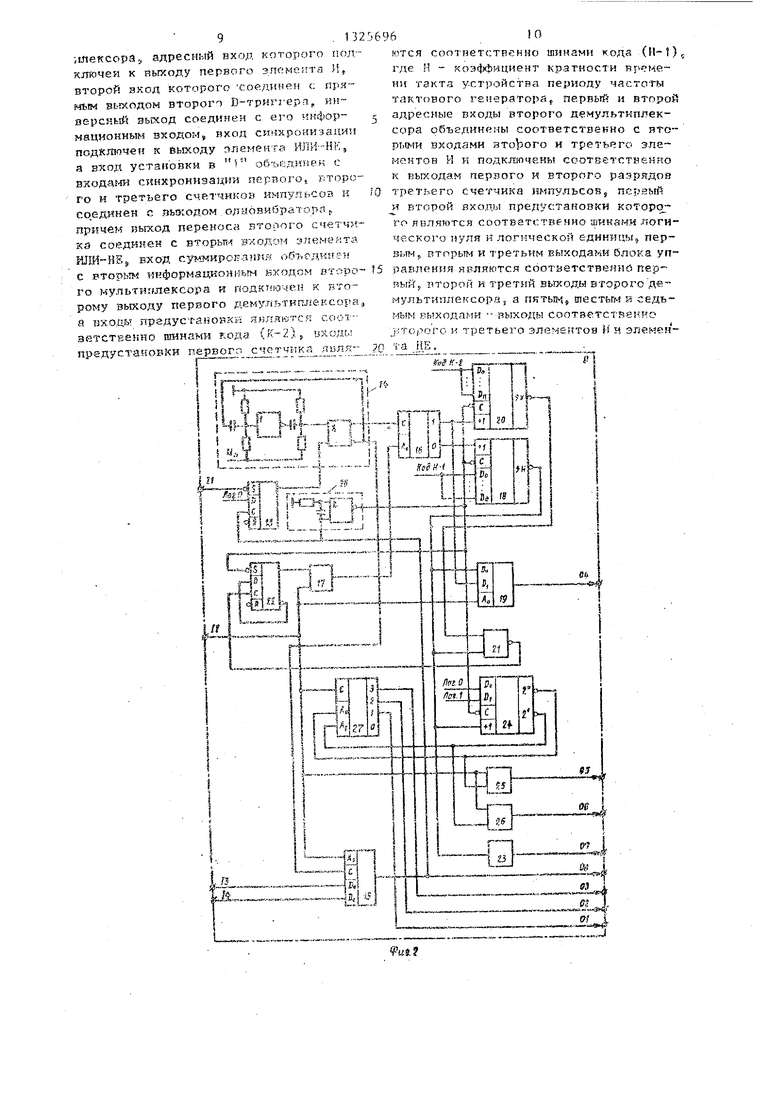

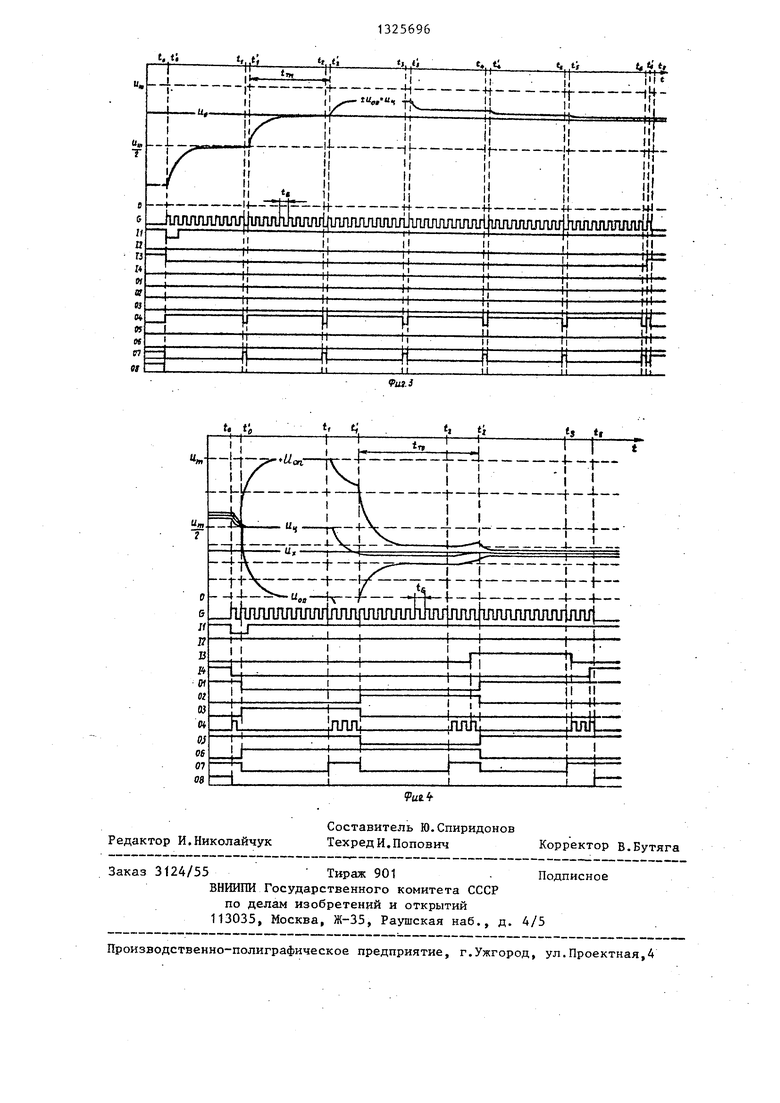

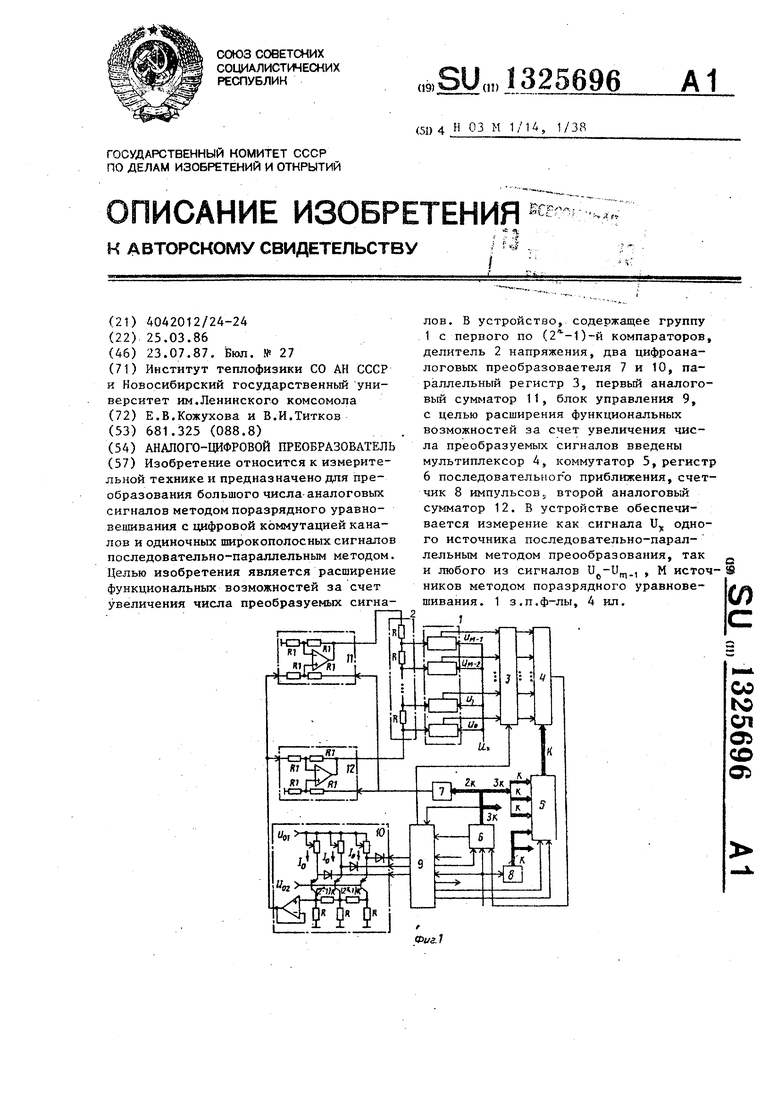

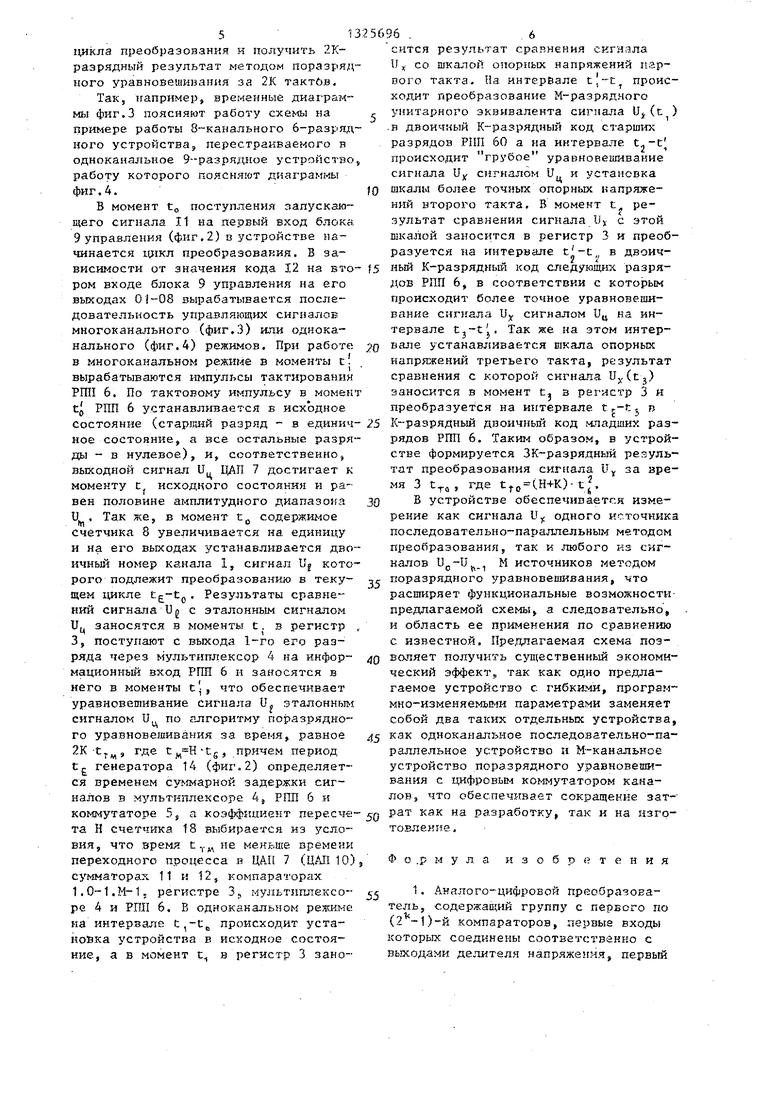

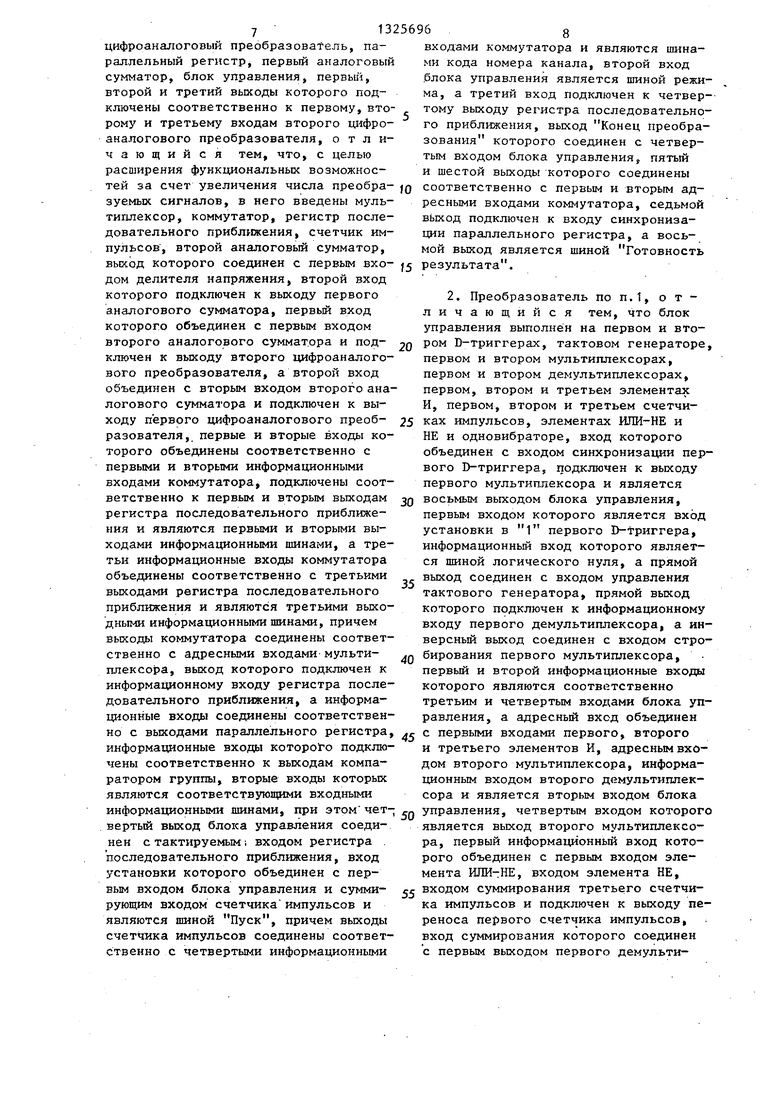

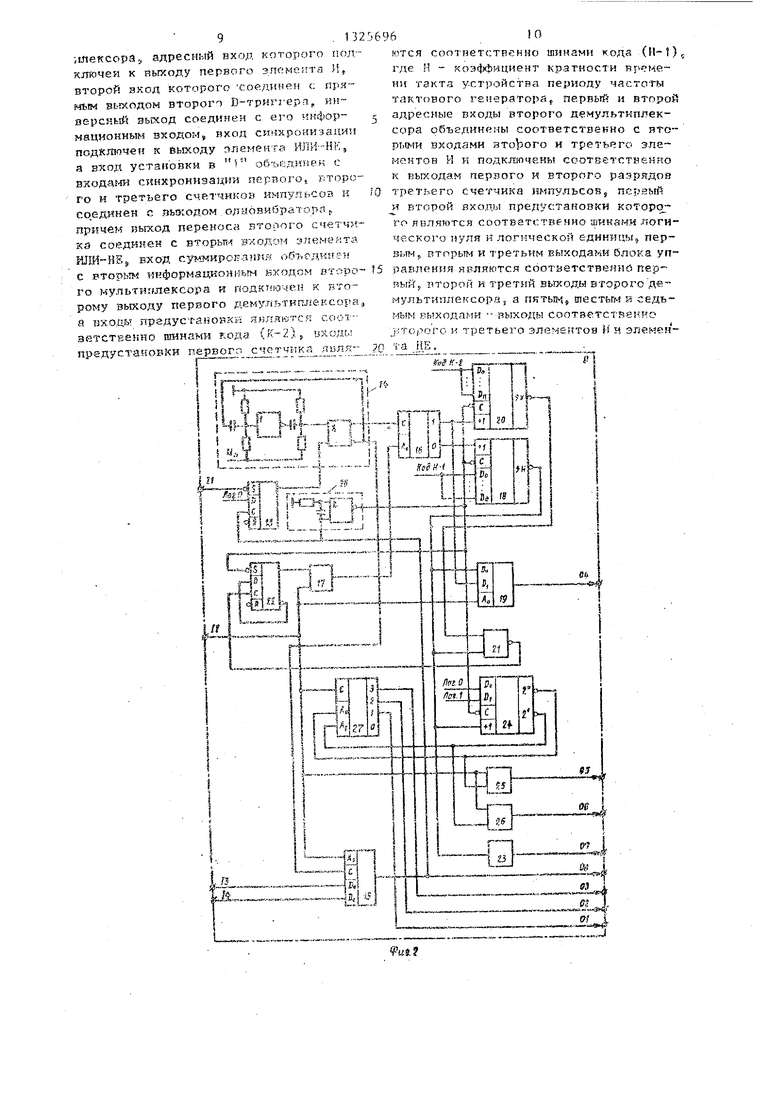

На фиг.1 приведена функциональная схема устройства; на фиг.2 - схема блока управления} на фиг.З и 4 - временные диаграммы, поясняющие работу устройства в многоканальном и однока- нальном режимах работы соответственно.

Устройство содержит группу 1 компараторов 1,0-1.М, где М 2 делитель 2 напряжения, паратшельный регистр 3, мультиплексор 4, ко даутатор 5, регистр 6 последовательного приближения

ты t- стробирования регистра 3-, где ,2 и 3, и величина t одного такта преобразования. Кроме того, на диаграммах (фиг„3 и 4) показаны величи- J, кы Uj амплитудного диапазона ЦАП 7 и его выходной сигнал U-, сигнал G на прямом выходе генератора 14 и период 1 его частот,, сигналы Upf, и -Uor, на первом и втором входах делителя 2.,

JQ сигналы 11-14 на первом-четвертом входах блока 9 и сигналы 01-08 на его первом-восьмом выходах.

Устройство работает следующим образом.

15 На первые и вторые входы аналоговых сумматоров 11 к 12 поступают выходные сигналы U(t) ЦАП 7 и (t) ЦАП 10, а на их выходах образуются соответственно суммарный сигнал ,

2Q равный и (t)-f-Uno (t), и разностный сигнал -Upn , равный Ъ ц (t)(t). Эти сигналы поступают на входгл делителя 2 из М одинаковых регистров, а с его выходов - на первые входы компарато, первый цифроаналоговый пре-25 Ро 1.0-1.М-1. На вторые входы компа- образователь (ЦАП) 7, счетчик 8 им- раторов 1.0-1.,М-1 поступают в много- пульсов, блок 9 управления, второй канальном режиме работы М измеряемых ЦАП 10, первый 11 и второй 12 анало- сигналов ,„., , а в одноканальном говые сумматоры. режиме - один измеряемъш сигнал Ux

Блок 9 управления содержит D-триг-JQ ЦАП 10 управляет блок 9, а ЦАЛ 7 - гер 13, тактовый генератор 14, пер- регистр 6 последовательного прибли- вьй мультиплексор 15, перзый демуль- жения. В многоканальном режиме на

типлексор 16, первьй элемент И 17, первый счетчик 18 импульсов, второй

вход ЦАП 10 поступает нулевой код с выходов блока 9, что обеспечив-ает нумультиплексор 19, второй счетчик 20 левой сигнал (t) на выходе ЦАП 10 импульсов, элемент ШШ-НЕ 21., второй и., соответственно, позволяет сформи- D-триггер 22, элемент НЕ 23, третий ровать на первых входах всех компар а- счетчик 24 импульсов, второй 25 и торов одинаковьм сигнал, равный ЦцСс). третий 26 элементы И, второй демульти- Таким образом,, в многоканальном режи- плексор 27 и одновибратор 28. , Q ме производится сравнение каждого из - На временных диаграммах (фиг.З) измеряемых сигналов ,., с эталон- многоканального режима показан измеря- ным сигналом U|(t) ЦАП 7 с помощью емый сигнал Uj на втором входе компа- компараторов 1.0-1.М-1. В одноканаль- ратора l-.l, где ,1,.. . ,М-1, отме- ном режиме на входах иДП 10 формиру- чены моменты tg и t р начала и конца ется такая последовательность двоич- цикла преобразования, моменты t стро- ных кодов, что выходной сигнал бирования регистра 6 последовательного приближения, где ,,..jZK, моменты- t стробирования регистра 3, где ,,..,2К н показана величина t одного такта преобразования, ila временных диаграммах (фиг,4) однока- иального режима показан измеряемый сигнал Uj, на вторых входах компараторов 1.0-1.М-1, отмечены моменты t и t g начала и конца цикла пргобразо-+

и.

вания, моменты t . изменения кода на входах ЦА.П 10 и на адресных входах коммутатора 5, где .1 и 2, моменUu,o(t;) равен величинам , 2- и и,.,. 2 в первом, вторам и третьем тактах соответственно,

J50 где Uj - амплитудный диапазон ЦАП 7. Это обеспечивает формирование на первых входах компараторов 1..М-1 вначале грубой шкалы опорных напряжений первого такта в диапазоне иц(с;|)55 и,„/2-иц (t ), затем более точной шкалы второго такта в диапазоне Ujt,)-U,.2 ,)4.ц.2- и наконец точной шкалы третьего такта в диапазоне Ь ц (t з)-и.2 ,(t2,) +

ты t- стробирования регистра 3-, где ,2 и 3, и величина t одного такта преобразования. Кроме того, на диаграммах (фиг„3 и 4) показаны величи- кы Uj амплитудного диапазона ЦАП 7 и его выходной сигнал U-, сигнал G на прямом выходе генератора 14 и период 1 его частот,, сигналы Upf, и -Uor, на первом и втором входах делителя 2.,

сигналы 11-14 на первом-четвертом входах блока 9 и сигналы 01-08 на его первом-восьмом выходах.

Устройство работает следующим образом.

На первые и вторые входы аналоговых сумматоров 11 к 12 поступают выходные сигналы U(t) ЦАП 7 и (t) ЦАП 10, а на их выходах образуются соответственно суммарный сигнал ,

равный и (t)-f-Uno (t), и разностный сигнал -Upn , равный Ъ ц (t)(t). Эти сигналы поступают на входгл делителя 2 из М одинаковых регистров, а с его выходов - на первые входы компаратовход ЦАП 10 поступает нулевой код с выходов блока 9, что обеспечив-ает нулевой сигнал (t) на выходе ЦАП 10 и., соответственно, позволяет сформи- ровать на первых входах всех компар а- торов одинаковьм сигнал, равный ЦцСс). Таким образом,, в многоканальном режи- ме производится сравнение каждого из измеряемых сигналов ,., с эталон- ным сигналом U|(t) ЦАП 7 с помощью компараторов 1.0-1.М-1. В одноканаль- ном режиме на входах иДП 10 формиру- ется такая последовательность двоич- ных кодов, что выходной сигнал

-+

и.

Uu,o(t;) равен величинам , 2- и и,.,. 2 в первом, вторам и третьем тактах соответственно,

где Uj - амплитудный диапазон ЦАП 7. Это обеспечивает формирование на первых входах компараторов 1..М-1 вначале грубой шкалы опорных напряжений первого такта в диапазоне иц(с;|),„/2-иц (t ), затем более точной шкалы второго такта в диапазоне Ujt,)-U,.2 ,)4.ц.2- и наконец точной шкалы третьего такта в диапазоне Ь ц (t з)-и.2 ,(t2,) +

-2

-(.)

313

, с которыми сравнивается измеряемый сигнал U с помощью компараторов 1.0-1.М-1. Это позволяет получить последовательность М-разрядных унитарных эквивалентов сигнала U с точностью U,(t,)(V , U,(tj) + fU, и и,(Гз)+и„. 2- i« в первом, втором и третьем тактах соответственно. Результаты сравнения входных сигналов с эталонными сигналами заносятся в моменты t. в регистр 3, а с его выходов поступают на информационные входы мультиплексора А, которым управляет выходной код коммутатора 5

В многоканальном режиме на адресных входах коммутатора 5 постоянно установлен адрес его нулевого группового входа. Это обеспечивает подключение к адресным входам мультиплексора 4 выходного кода счетчика 8, в котором находится двоичный номер канала 1, сигнал U| которого подлежит преобразованию в текущем цикле и позволяет подключить выход компаратора 1.1 через регистр 3 и мультиплексор 4 к информационному входу регистра 6 последовательного приближения (РПП) и получить в РПП 6 двоичный 2К-разрядный эквивалент сигнала Up за 2К тактов с помощью ЦАП 7 методом поразрядного уравновешивания.

В одноканальном режиме на адресных входах коммутатора 5 формируется последовательность двоичных адресов вначале его третьего, затем второго и наконец первого груцповых входов, что обеспечивает подключение к адресным входам мультиплексора 4 выходного кода вначале К старших, затем К последующих и, наконец, К младших разрядов РПП 6 в первом, втором и тр1етьем тактах преобразования соответственно. Это позволяет произвести преобразование М-разрядных унитарных эквивалентов сигнала U(t,), ) и U(t) в его К-разрядные двоичные эквиваленты старщих, промежуточных и младщих разрядов РПП 6 с помощью мультиплексора 4, коммутатора 5 и блока 9 управления и получить в РПП 6 ЗК-разрядный двоичный эквивалент сигнала ) за три такта с помощью ЦАП 7 последовательно-параллельным методом.

Преобразование М-разрядного унитарного Кода компараторов 1.0-1.М-1, хранящегося в регистре 3, в К-разряд ный двоичный код РПП 6 осуществляется по алгоритму последовательного

5696. 4

приближения следующим образом. В исходном состоянии старший разряд (из группы в К разрядов) РПП 6 установлен в единичное состояние, а все младшие его разряды - в нулевое, таким образом, на адресных иходах мультиплексора 4 установлен двоичный номер компаратора 1.М/2. Соответственно, выходной сигнал этого компаратора (этоQ го разряда регистра 3) поступает на информационный вход РПП 6. По тактовому сигналу в старший разряд РПП 6 заносится значение сигнала компаратора 1.М/2 и одновременно более млад5 ший.разряд РПП 6 устанавливается в единицу, и, таким образом, формируется номер компаратора, который будет оп рашиваться следующим сигналом. Если выходной сигнал компаратора 1.М/2 ра0 вен нулю (значит, и сигналы всех компараторов с большими номерами тоже равны нулю в унитарном коде), то на адресных входах мультиплексора фор- мируется номер компаратора 1.М/4, а

5 в противном случае - номер компаратора 1.3М/4 и т.д., т.е. на адресных входах мультиплексора 4 формируются Номера компараторо в по алгоритму последовательного приближения. Такой

0 способ шифрования является быстродействующим, так как на получение К-раз- рядного двоичного кода из М-разрядного унитарного затрачивается время, равное K-tg, где период t частоты тактирования РПП 6 в этом случае выбирается исходя иэ времени суммар- , ной задержки в РПП 6, коммутаторе 5 и мультиплексоре 4, например, на по- лучение трех-четырех разрядного-дво0 ичного кода из семи-, 15-разрядного- унитарного кода затрачивается время порядка 100-120 не, что вполне сравнимо с временем задержки в параллельном приоритетном шифраторе известно5 го устройства.

Таким образом, схема совмещает на своих элементах два отдельных устройства, выбор любого иэ которых осуществляется путем установки соответстQ вующего кода режима на втором входе блока 9 управления (фиг.2), и позволяет произвести преобразование одного измеряемого сигнала U последователь - но-параллельным методом и получить

5 ЗК-раэрядный результат за три такта и преобразование любого из входных сигналов Up-U., его каналов путем занесения двоичного номера этого канала в счетчик 8 на время текущего

5

Ю

гщкла преобразования и получить 2К- разрядный результат методом поразрядного уравновешшзания за 2К тактов.

Так, например, временные диаграммы фиг.З поясняют работу схеь-ш на примере работы 8-канального 6-разрядного устройства, перестраиваемого в одноканальное 9-разрядное устройство, работу которого поясняют днаграмг- ы фиг.4.

В момент to поступления запускающего сигнала 11 на первый вход блока 9 управления (фиг.2) в устройстве начинается цикл преобразовакия. В зависимости от значения кода 12 на вто- f5 ный К-разрядный код сггедующ х разря- ром входе блока 9 управления на его дов РПП 6, в соответствии с которым

происходит более точное уравновешивание сигнала U,f сигналом Иц на интервале tj-t . Так же на этом интервале устанавливается шкала опорных напряжений третьего такта, результат сравнения с KOTopoi f сигнапа ) заносится в момент t, в регистр 3 и преобразуется на интервале tr-tj в

сится результат сравнения сигнала и,- со шкалой опорных напряжений пар- вого такта. На интервале t,--t происходит преобразование М-разрядного - унитарного эквивалента сигнала Uj, (t ) .в двоичный К-разрядный код старших разрядов РПП 60 а на интервале tj-t происходит грубое уравновешивание сигнала U сигналом U и установка шкалы более точиьпс опорных напряжений HTopoi -o такта. В момент с результат сравнения сигнала Uj, с этой шкалой заносится в регистр 3 и преобразуется на интервале t -с„ в двоичвыходах 01-08 вырабатывается последовательность управляющих сигналов многоканального (фиг.З) или однока- нального (фиг.4) режимов. При работе в многоканальном режиме в моменты с вырабатываются импульсы тактирования РШ1 6. По тактовому импульсу в момент tl РПП 6 устанавливается в исходное

20

состояние (стар1пий разряд - в единич- 25 К разрядный дноичньш код младших разное состояние, а все остальные разря- рядов РПП 6. Таким образом, в устрой- ды - в нулевое), и, соответственно, стве формируется ЗК разряднь Й резульвыходной сигнал U ИДИ 7 достигает к

тат преобразования сигнала

..2

моменту t исходного состояния и ра- мя 3 t,- , где t|(j (H+K)-t

В устройстве обеспечива рение как сигнала Uj: одног последовательно-параллельн преобразования, так и любо налов Ug-Uj М источников 1- поразрядного уравновешиван распдфяет функциональные в предлагаемой схемы а след и область ее применения по с известной. Предлагаемая

вен половине амплитудного диапазона и , Так же, в момент t содержимое счетчика 8 увеличивается на единицу и на его выходах устанавливается дво- ичньй номер канала 1, сигнал Uj которого подлежит преобразованию в текущем цикле , Результаты сравнений сигнала и с эталонным сигналом U заносятся в моменты t. в регистр 3, поступают с выхода 1-го его раз

ряда через мультиплексор 4 на инфор- 0 воляет получить суп(ественный экономи- мационньш вход РПП 6 и заносятся в ческий эффект,, так как одно предла- него в моменты t , что обеспечивает уравновешивание сигнала U. эталонным

сигналом и., по алгоритму поразрядноЦ

гаемое устройство с гибкими, программно-изменяемыми параметрами заменяет собой два таких отдельных устройства, 45 как одноканальиое последовательно-параллельное устройство и М-канальное устройство поразрядного уравновешивания с цифровым коммутатором каналов, что обеспечивает сокращение заткоммутаторе 5, а коэффициент пересче- JQ рат как на разработку, так и на нзгота Н счетчика 18 выбирается из уело- товление.

ВИЯ, что время , не меньше времени

переходного процесса в ЦА.Г1 7 (UMIIO),

с мнаторах 11 и 12, компараторах

1.0-1.М-1. регистре 3, мультпплексо-

го уравновешивания за время, равное 2K-tj, где , причем период t генератора 14 (фиг.2) определяется временем суммарной задержки сигналов в мультиплексоре 4j РПП 6 и

ре 4 и РПЛ 6. В одноканальном режике на интерзале t,-t: происходит установка устройства в исходное состояние, а в момент t, в регистр 3 заноФо.рмула изобретения

1. Аналого-цифровой преобразователь, содержащий группу с первого по (2 -1)-й компараторов, первые входы которых соединены соответственно с выкодами делителя напряжения, первый

ный К-разрядный код сггедующ х разря- дов РПП 6, в соответствии с которым

сится результат сравнения сигнала и,- со шкалой опорных напряжений пар- вого такта. На интервале t,--t происходит преобразование М-разрядного унитарного эквивалента сигнала Uj, (t ) .в двоичный К-разрядный код старших разрядов РПП 60 а на интервале tj-t происходит грубое уравновешивание сигнала U сигналом U и установка шкалы более точиьпс опорных напряжений HTopoi -o такта. В момент с результат сравнения сигнала Uj, с этой шкалой заносится в регистр 3 и преобразуется на интервале t -с„ в двоичтат преобразования сигнала U, за зре..2

мя 3 t,- , где t|(j (H+K)-t

мя 3 t,- , где t|(j (H+K)-t

В устройстве обеспечивается измерение как сигнала Uj: одного источника последовательно-параллельным методом преобразования, так и любого из сигналов Ug-Uj М источников методом поразрядного уравновешивания, что распдфяет функциональные возможности- предлагаемой схемы а следовательно, и область ее применения по сравнению с известной. Предлагаемая схема позФо.рмула изобретения

1. Аналого-цифровой преобразователь, содержащий группу с первого по (2 -1)-й компараторов, первые входы которых соединены соответственно с выкодами делителя напряжения, первый

цифроаналоговый преобразователь, параллельный регистр, первый аналоговый сумматор, блок управления, первьй, второй и третий выходы которого подключены соответственно к первому, второму и TpeTbeNfy входам второго цифро- аналогового преобразователя, отличающийся тем, что, с целью расширения функциональных возможнос20

тей за счет увеличения числа преобра- JQ соответственно с первым и вторым ад- зуемых сигналов, в него введены мультиплексор, коммутатор, регистр последовательного прибл гжения, счетчик импульсов, второй аналоговый сумматор, выход которого соединен с первым вхо- j результата дом делителя напряжения, второй вход которого подключен к выходу первого аналогового сумматора, первый вход которого объединен с первым входом второго аналогового сумматора и подключен к выходу второго цифроаналого- вого преобразователя, а второй вход объединен с вторым входом второго аналогового сумматора и подключен к выходу первого цифроаналогового преоб- 25 разователя, первые и вторые входы которого объединены соответственно с первыми и вторыми информационными входами коммутатора, подключены соответственно к первым и вторым выходам регистра последовательного приближения и являются первыми и вторыми выходами информационными шинами, а третьи информационные входы коммутатора объединены соответственно с третьими выходами регистра последовательного приближения и являются третьими выходными информационными шинами, причем выходы коммутатора соединены соответственно с адресными входами мультиплексора, выход которого подключен к информационному входу регистра последовательного приближения, а информационные входы соединены соответственно с выходами параллельного регистра, - информационные входы которо1 о подключены соответственно к выходам компаратором группы, вторые входы которых являются соответствующими входными информационными шинами, при этом четвертый выход блока управления соединен с тактируемым , входом регистра . последовательного приближения, вход установки которого объединен с первым входом блока управления и рующим входом счетчика импульсов и являются шиной Пуск, причем выходы счетч:ика импульсов соединены соответственно с четвертыми информационными

ресными входами коммутатора, седьмой вькод подключен к входу синхронизации параллельного регистра, а восьмой выход является шиной Готовность

2. Преобразователь по п.1, отличающийся тем, что блок управления выполнен на первом и втором D-триггерах, тактовом генераторе, первом и втором мультиплексорах, первом и втором демультиплексорах, первом, втором и третьем элементах И, первом, втором и третьем счетчиках импульсов, элементах ИЛИ-НЕ и НЕ и одновибраторе, вход которого объединен с входом синхронизации первого D-триггера, подключен к выходу первого мультиплексора и является

30 восьмым выходом блока управления, первым входом которого является вход установки в 1 первого В-триггера, информационный вход которого является шиной логического нуля, а прямой выход соединен с входом управления тактового генератора, прямой выход которого подключен к информационному входу первого демультиплексора, а инверсный выход соединен с входом стро- бирования первого мультиплексора, первый и второй информационные входы которого являются соответственно третьим и четвертым входами блока управления, а адресный вход объединен с первыми входами первого, второго и третьего элементов И, адресным входом второго мультиплексора, информационным входом второго демультиплексора и является вторым входом блока

50 управления, четвертым входом которого является выход второго мультиплексора, первый информационный вход которого объединен с первым входом элемента ИЛИ-НЕ, входом элемента НЕ,

сг входом суммирования третьего счетчика импульсов и подключен к выходу переноса первого счетчика импульсов, вход суммирования которого соединен с первым выходом первого демульти-

35

40

входами коммутатора и являются шинами кода номера канала, второй вход .блока управления является шиной режима, а третий вход подключен к четвертому выходу регистра последовательного приближения, выход Конец преобразования которого соединен с четвертым входом блока управления,, пятый и шестой выходы которого соединены

соответственно с первым и вторым ад- результата

ресными входами коммутатора, седьмой вькод подключен к входу синхронизации параллельного регистра, а восьмой выход является шиной Готовность

соответственно с первым и вторым ад- результата

2. Преобразователь по п.1, отличающийся тем, что блок управления выполнен на первом и втором D-триггерах, тактовом генераторе, первом и втором мультиплексорах, первом и втором демультиплексорах, первом, втором и третьем элементах И, первом, втором и третьем счетчиках импульсов, элементах ИЛИ-НЕ и НЕ и одновибраторе, вход которого объединен с входом синхронизации первого D-триггера, подключен к выходу первого мультиплексора и является

восьмым выходом блока управления, первым входом которого является вход установки в 1 первого В-триггера, информационный вход которого является шиной логического нуля, а прямой выход соединен с входом управления тактового генератора, прямой выход которого подключен к информационному входу первого демультиплексора, а инверсный выход соединен с входом стро- бирования первого мультиплексора, первый и второй информационные входы которого являются соответственно третьим и четвертым входами блока управления, а адресный вход объединен с первыми входами первого, второго и третьего элементов И, адресным входом второго мультиплексора, информационным входом второго демультиплексора и является вторым входом блока

управления, четвертым входом которого является выход второго мультиплексора, первый информационный вход которого объединен с первым входом элемента ИЛИ-НЕ, входом элемента НЕ,

входом суммирования третьего счетчика импульсов и подключен к выходу переноса первого счетчика импульсов, вход суммирования которого соединен с первым выходом первого демульти-

д

;0

ллексора,,, адресный вход которого пол,- ключей к выходу первого эпсмеита И второй вход Которого соединен с прямым зьжодом второго D-триггера, ин- верскьй выход соединен с ег о информационным входом вход синхронизации подключен к 6ЫХОДУ алемеита ИЛИ-НК, а зкод уетанЬйки в о6-ьед1 5ен с Екодги-ш сннхрокизацни первого, вторе го и третьего счетчиков имлупьсоа и соединен с вьзюдом .одабвибраторя (, причем выход переноса второго счетчика соединен с вторьт -- входам эпемента Ш1И-ИЕ, вход суммирог. объединен с вторые информационкьпч входом второ- 5 го мультигшексора и подктоочен к второму вьосоду первого дему.гвьтиплексора,, а входу пргдус гаковки янллвтся соот-- зетствеино шннами кода (),, иходы предустановки п е PJB о го с ч е г ч и к а л ц л я - 7Q

1325696 0

ются соотиетственно шинами кода (M-t), где Н - коэ|}х5)иднент кратности вр.7ме ИИ такта у.стройства периоду частоты тактового геиераторй первый я второй адресные входы второго яемульткплек- сора объединены соответственно с иго- рыми входами и третьего зле- мектов И и подключены соответстненио к выходам первого и второго разрядов третьего счетчика нмпульсоВд псраьгй и второй входы предустановки KOTopq - го являются соотватственяо шиками логического пуля к логической еднняцы, первым, вторым и третьим выходами блока управления являются соотаетственно первый,, рторон и третий выходы второго де мультиплексора, а пятьп,, шестым к седьмым выходами --выходы соответствекио j-iToporo к третьего эленентон И н элемен- .л НЕ.

равления являются соотаетственно первый,, рторон и третий выходы второго де мультиплексора, а пятьп,, шестым к седьмым выходами --выходы соответствекио j-iToporo к третьего эленентон И н элемен- .л НЕ.

. i

/.л;

..«;

«j. ,t

t « t

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Генератор гармонических сигналов | 1989 |

|

SU1626379A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1499495A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

Изобретение относится к измерительной технике и предназначено для преобразования большого числа аналоговых сигналов методом поразрядного уравновешивания с цифровой коммутацией каналов и одиночных широкополосных сигналов последовательно-параллельным методом. Целью изобретения является расширение функциональных возможностей за счет увеличения числа преобразуемых сигналов. в устройство, содержащее группу 1 с первого по ()-й компараторов, делитель 2 напряжения, два цифроана- логовых преобразоваетеля 7 и 10, параллельный регистр 3, первый аналоговый сумматор 11, блок управления 9, с целью расширения функциональных возможностей за счет увеличения числа преобразуемых сигналов введены мультиплексор 4, коммутатор 5, регистр 6 последовательногЪ приближения, счетчик 8 импульсов„ второй аналоговый сумматор 12. В устройстве обеспечивается измерение как сигнала U одного источника последовательно-параллельным методом преообразования, так и любого из сигналов ., , М источ-S НИКОВ методом поразрядного уравновешивания. 1 з.п.ф-лы, 4 ил. (Л с со 1C ел Oi со о:

t t:,

-j -J:-I.-d -

ГЛЛ

Редактор И.Николайчук

9ui f

Составитель Ю.Спиридонов Техред И. Попович

Заказ 3124/55 Тираж 901- Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор В.Бутяга

Авторы

Даты

1987-07-23—Публикация

1986-03-25—Подача