Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения системы передачи и обработки дискретной информации.

Известно устройство для подсчета числа единиц двоичного кода по модулю К, содержащее генератор тактовых импульсов, многоканальный преобразователь параллельного кода в последовательность импульсов, триггер, элементы ИЛИ, счетчик по модулю К, группу блоков подсчета единиц по модулю К, группу элементов И, группу элементов ИЛИ, элемент И и делитель [1].

Устройство позволяет формировать остаток двоичного кода по модулю К. Его недостатком является низкое быстродействие, обусловленное тем, что пересчет результатов частичной обработки групп разрядов входного кода с учетом их весов производится путем деления тактовой частоты на величину остатка по модулю К весов соответственных разрядов входного кода.

Наиболее близким по технической сущности и функциональным возможностям к заявленному является устройство для подсчета числа единиц двоичного кода по модулю К, содержащее генератор тактовых импульсов, выход которого соединен с тактовым входом многоканального преобразователя параллельного кода в последовательность импульсов, р групп информационных входов которого являются соответствующими входами устройства, причем с первого по (р-2)-й выходы многоканального преобразователя параллельного кода в последовательность импульсов подключены к первому входу первого элемента ИЛИ и суммирующим входам с первого по (р-1)-й блоков подсчета единиц по модулю К, первый выход каждого из которых соединен с первым входом одноименного элемента И, выход которого подключен к вычитающему входу одноименного блока подсчета единиц по модулю К, выход первого элемента ИЛИ соединен с входом счетчика по модулю К, выходы которого являются информационными выходами устройства, управляющий выход многоканального преобразователя параллельного кода в последовательность импульсов соединен с входом триггера, выход которого подключен к вторым входам с первого по (р-1)-й элементов И и первому входу р-го элемента И, второй выход i-го блока подсчета единиц по модулю К (i = 1,..., р-1) подключен к (i+2)-у входу j-го элемента И, i < j ≅ р, и (i+1)-у входу р-го элемента И, выход которого является контрольным выходом устройства, запрещающий вход элемента ЗАПРЕТ подключен к выходу р-го элемента И, выход элемента ЗАПРЕТ соединен с вторым входом первого элемента ИЛИ, с первого по (р-1)-й входы второго элемента ИЛИ подключены к выходам соответственно с первого по (р-1)-й элементов И, выход второго элемента ИЛИ соединен с входом обнуления делителя частоты, тактовый вход и вход синхронизации которого объединены соответственно с первым и вторым разрешающими входами элемента ЗАПРЕТ и подключены к выходам соответственно генератора тактовых импульсов и триггера, первый выход делителя частоты подключен к (i+2)-у входу i-го элемента И, управляющий вход делителя частоты является управляющим входом устройства [2].

Устройство позволяет формировать остаток двоичного кода по модулю К. Его недостатком является низкое быстродействие, обусловленное тем, что пересчет результатов частичной обработки групп разрядов входного кода из блоков подсчета единиц по модулю К в счетчик по модулю К с учетом значений остатков весов разрядов входного кода по модулю К производится путем деления тактовой частоты на величину этого остатка.

Целью изобретения является повышение быстродействия устройства.

Цель достигается тем, что в устройство для контроля параллельного двоичного кода по модулю К, содержащее многоканальный преобразователь параллельного кода в последовательность импульсов, соединенный информационными входами с информационными шинами, тактовым входом с выходом генератора тактовых импульсов, а первым информационным выходом с входом элемента ИЛИ, выход которого соединен с первым входом счетчика по модулю К, выходы которого являются информационными выходами устройства, причем i-й накапливающий сумматор ((i= ) ) соединен первым входом с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а первым выходом с входом i-го элемента И, введены r-1 элементов ИЛИ и р групп по r-1 элементов И (r = ]log2K[), при этом i-й накапливающий сумматор соединен c j-м входом (j=

) ) соединен первым входом с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а первым выходом с входом i-го элемента И, введены r-1 элементов ИЛИ и р групп по r-1 элементов И (r = ]log2K[), при этом i-й накапливающий сумматор соединен c j-м входом (j= ) с соответствующим выходом многоканального преобразователя параллельного кода в последовательность импульсов, j-м выходом с первым входом (j-1)-го элемента И i-й группы, соединенного вторым входом с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с входом j-го элемента ИЛИ, соединенного входом с соответствующим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с j-м входом счетчика по модулю К, i-й элемент И соединен вторым входом с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с входом первого элемента ИЛИ, выход окончания работы многоканального преобразователя параллельного кода в последовательность импульсов является выходом окончания работы устройства.

) с соответствующим выходом многоканального преобразователя параллельного кода в последовательность импульсов, j-м выходом с первым входом (j-1)-го элемента И i-й группы, соединенного вторым входом с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с входом j-го элемента ИЛИ, соединенного входом с соответствующим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с j-м входом счетчика по модулю К, i-й элемент И соединен вторым входом с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, а выходом с входом первого элемента ИЛИ, выход окончания работы многоканального преобразователя параллельного кода в последовательность импульсов является выходом окончания работы устройства.

Введение дополнительных элементов ИЛИ, р групп элементов И и новых связей позволяет осуществлять на первом этапе работы устройства параллельную обработку каждым накапливающим сумматором и счетчиком по модулю К сигналов с r выходов многоканального преобразователя параллельного кода в последовательность импульсов, а на втором этапе пересчет результатов из каждого накапливающего сумматора в счетчик по модулю К за один такт, что и обеспечивает повышение быстродействия устройства.

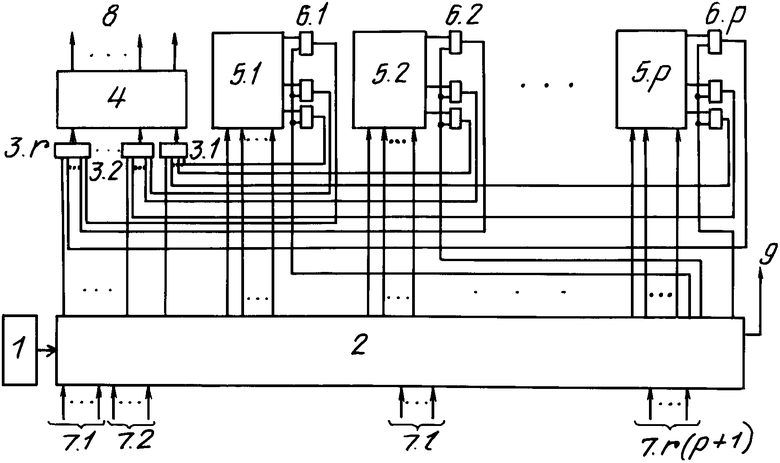

Структурная схема устройства представлена на чертеже.

Устройство для контроля параллельного двоичного кода по модулю К содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательность импульсов, элементы ИЛИ 3.1-3.r, счетчик 4 по модулю К, накапливающие сумматоры 5.1-5.р, группы из r элементов И 6.1-6.р, информационные входы 7, информационные выходы 8, выход 9 окончания работы устройства.

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов соединен группами информационных входов каналов с информационными шинами 7.i, выходами i-го канала (i = 1,...,r; r = ]log2K[) с первым входом элемента ИЛИ 3.i, соединенного выходом с i-м входом счетчика 4 по модулю К, имеющим вес 2i-1. Накапливающий сумматор 5.j (j = 1,...,р) соединен с i-м входом, имеющим вес 2i-1, с выходом (rj+i)-го канала многоканального преобразователя 2, i-м выходом с первым входом i-го элемента И группы 6.j, соединенного вторым входом с j-м управляющим выходом многоканального преобразователя 2, а выходом с (j+ 1)-м входом элемента ИЛИ 3.i. Многоканальный преобразователь 2 параллельного кода в последовательность импульсов соединен выходом окончания работы с выходом окончания работы устройства.

Устройство работает следующим образом.

В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательность импульсов, счетчик 4 по модулю К и накапливающие сумматоры 5 сброшены.

Входной код подан на входные информационные шины 7, причем на входы 7.i группы входных информационных шин подаются разряды входного кода с весами ωi такими, что ( ωi )modK = const, причем ( ωi )modK = 2 в степени (i - [ ]r - 1). Если разряд хj входного кода имеет вес ωjтакой, что (ωj)modK ≠ 2α , он соединен с входами групп входных информационных шин так, что сумма весов ( ωi) modK, поданных на входы данных групп, равна ( ωj)modK.

]r - 1). Если разряд хj входного кода имеет вес ωjтакой, что (ωj)modK ≠ 2α , он соединен с входами групп входных информационных шин так, что сумма весов ( ωi) modK, поданных на входы данных групп, равна ( ωj)modK.

Тактовые импульсы поступают на тактовый вход преобразователя 2, который преобразует единичные сигналы на группе входных информационных шин 7.i в соответствующее количество единичных импульсов на i-м информационном выходе. Импульсы с информационных выходов 1-r преобразователя 2 поступают через элементы ИЛИ 3.1-3.r на соответствующие входы счетчика 4 по модулю К, а с информационных выходов 1 + tr-(t+1)r - на входы t-го накапливающего сумматора 5.t. Счетчик 4 по модулю К и накапливающие сумматоры 5 работают в режиме модульных накапливающих сумматоров, прибавляя на каждом такте к своему содержимому код, поступающий с выходов преобразователя 2 (суммирование производится по модулю К). По окончании преобразования входного кода преобразователь 2 перестает формировать импульсы на информационных выходах, а на его управляющих выходах от первого до р-го последовательно появляются единичные импульсы. При появлении импульса на i-м управляющем выходе он поступает на входы элементов И группы 6.i, разрешая прохождение сигналов с выходов накапливающего сумматора 5.i на выходы элементов И группы 6.i, а с их выходов через элементы ИЛИ 3.1-3.r - на входы счетчика 4 по модулю К, к содержимому которого при этом прибавляется код с выходов накапливающего сумматора 5.i. После опроса всех накапливающих сумматоров, обеспечивающих пересчет результатов обработки соответствующих групп разрядов входного кода с их выходов в счетчик 4, преобразователь 2 самоблокируется, прекращая формирование импульсов на всех своих выходах, при этом на его выходе окончания работы появляется единичный сигнал, поступающий на выход 9 окончания работы устройства. Выходной код остатка по модулю К входного кода снимается с выходов 8 счетчика 4 по модулю К.

Таким образом, предложенное устройство обеспечивает повышение быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для обнаружения ошибок в параллельном коде | 1987 |

|

SU1564733A1 |

| Устройство для преобразования количества единиц двоичного кода в код по модулю К | 1987 |

|

SU1527714A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения систем передачи и обработки дискретной информации. Цель изобретения - повышение быстродействия устройства. Устройство для контроля параллельного двоичного кода по модулю K содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательность импульсов, r элементов ИЛИ 3, счетчик 4 по модулю K, p накапливающих сумматоров 5 и p групп из r элементов И 6, соединенные между собой функционально. 1 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K, содержащее генератор тактовых импульсов, выход которого соединен с тактовым входом многоканального преобразователя параллельного кода в последовательность импульсов, p+1 групп информационных входов которого являются соответствующими информационными входами устройства, первый информационный выход многоканального преобразователя параллельного кода в последовательность импульсов соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым информационным входом счетчика по модулю K, выходы которого являются информационными выходами устройства, i-й накапливающий сумматор (i=  ) соединен первым информационным входом с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а первый выход i-го накапливающего сумматора соединен с первым входом i-го элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены r-1 элементов ИЛИ и p групп по r-1 элементов И (r = ]log2K[) , причем j-й информационный вход (j=

) соединен первым информационным входом с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а первый выход i-го накапливающего сумматора соединен с первым входом i-го элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены r-1 элементов ИЛИ и p групп по r-1 элементов И (r = ]log2K[) , причем j-й информационный вход (j= ) накапливающего сумматора соединен с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а j-й выход i-го накапливающего сумматора соединен с первым входом (j-1) -го элемента И i-й группы, выходы (j-1)-х элементов И p групп соединены соответственно с j-ми входами элементов ИЛИ с второго по r-й, первые входы которых соединены с соответствующими информационными выходами многоканального преобразователя параллельного кода в последовательность импульсов, выход j-го элемента ИЛИ соединен с j-м информационным входом счетчика по модулю K, вторые входы r-1 элементов И i-й группы и второй вход i-го элемента И соединены с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, выход окончания работы которого является выходом окончания работы устройства.

) накапливающего сумматора соединен с соответствующим информационным выходом многоканального преобразователя параллельного кода в последовательность импульсов, а j-й выход i-го накапливающего сумматора соединен с первым входом (j-1) -го элемента И i-й группы, выходы (j-1)-х элементов И p групп соединены соответственно с j-ми входами элементов ИЛИ с второго по r-й, первые входы которых соединены с соответствующими информационными выходами многоканального преобразователя параллельного кода в последовательность импульсов, выход j-го элемента ИЛИ соединен с j-м информационным входом счетчика по модулю K, вторые входы r-1 элементов И i-й группы и второй вход i-го элемента И соединены с i-м управляющим выходом многоканального преобразователя параллельного кода в последовательность импульсов, выход окончания работы которого является выходом окончания работы устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-09-30—Публикация

1991-05-05—Подача