(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1983 |

|

SU1357960A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

Изобретение относится к автоматике и вычислительной технике. При использовании изобретения в системах передачи и переработки дискретной информации позволяет повысить быстродействие устройства. Это достигается благодаря организации новых соединений блоков подсчета единиц по модулю К с дополнительными суммирующими входами счетчика по модулю К, а также специальному выполнению этого счетчика. 1 з.п. ф-лы, 3 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении различных устройств передачи и переработки дискретной информации.

Цель изобретения - повышение быстродействия устройства.

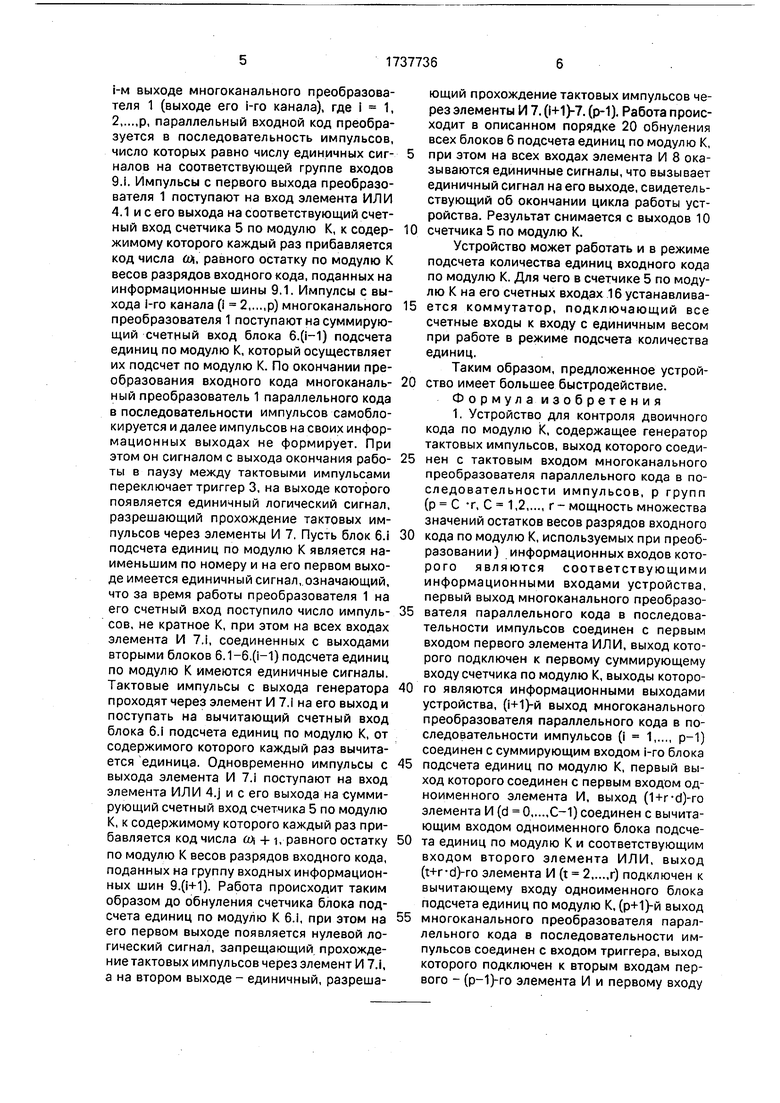

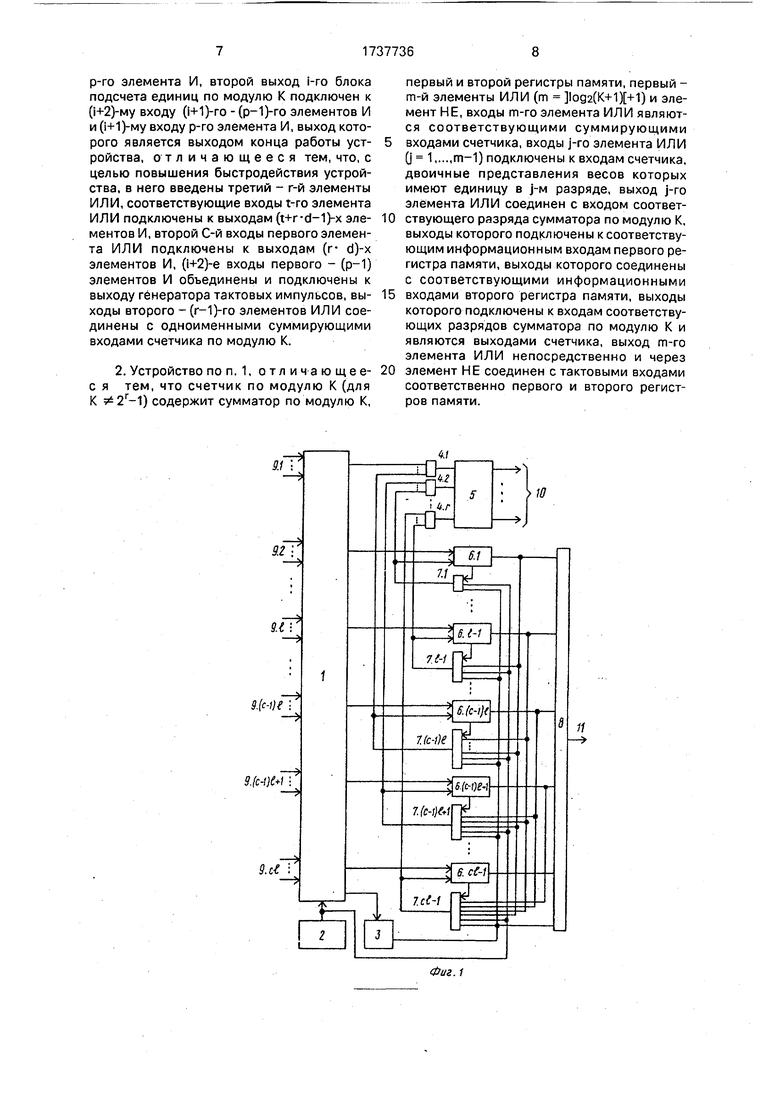

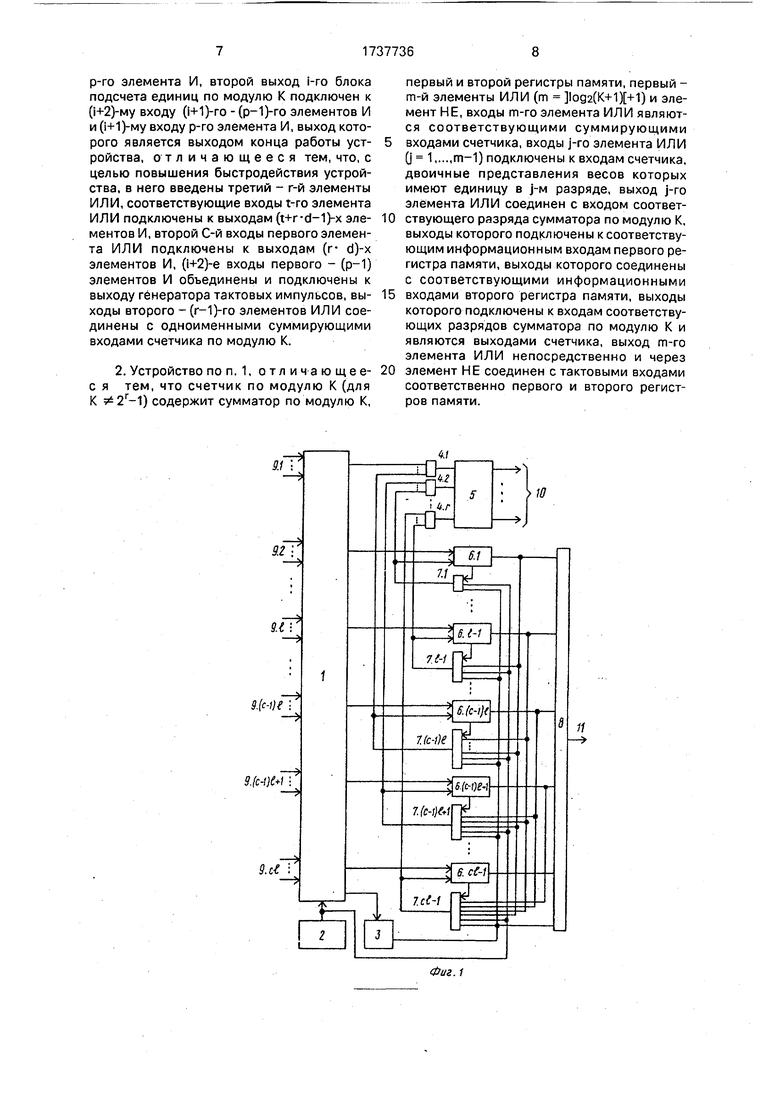

На фиг. 1 показана структурная схема устройства контроля двоичного кода по модулю К; на фиг. 2 - схема счетчика по модулю К 2П - 1 15; на фиг. 3 - схема счетчика по модулю К 2п-1 5.

Устройство контроля двоичного кода по модулю К содержит многоканальный преобразователь 1 параллельного кода в последо- вательности импульсов, генератор 2 тактовых импульсов, триггер 3, элементы ИЛИ 4.1 - 4.г, счетчик 5 по модулю К, блоки 6 подсчета единиц по модулю К, элементы И 7, элемент И 8, входные информационные шины 9, информационные выходы 10 и выход конца работы устройства 11. Многоканальный преобразователь .1 параллельного кода в последовательности импульсов соединен информационными входами с входными информационными шинами 9, тактовым входом - с выходом генератора 2 тактовых импульсов, выходом окончания работы - с входом триггера 3, первым информационным выходом (выходом первого канала) - с входом элемента ИЛИ 4.1, i-м информационным выходом - с суммирующим счетным входом (И)-го блока подсчета единиц по модулю К, 6.(Ы), первый выход которого соединен с первым входом (Ы)-го элемента И 7.(i-1) соединенного входами с выходом генератора 2 тактовых импульсов, выходом триггера 3 и вторыми выходами блоков 6 подсчета единиц по модулю К от первого до (i-2)-ro, а выходом - с вычитающим счетным входом (i-1)-ro блока 6.(i-1) подсчета количества единиц по модулю К,

VJ

CJ vj VI GO О

элемент И 8 соединен входами с вторыми выходами блоков 6 подсчета количества единиц по модулю К и выходом триггера 3, а выходом - с выходом 11 конца работы, счетчик 5 по модулю К соединен с j-м счет- ным входом с выходом j-ro элемента ИЛИ 4J, соединенного входами с выходами i-x элементов И 7.I таких, что для группы входных информационных шин 9.(i+1) значения остатков весов разрядов входного кода дан- ных групп одинаковы.

Количество элементов ИЛИ 4 выбирается равным либо г 1од2(К+1), либо мощности множества значений остатков весов разрядов входного кода по модулю К, т.е. достигать значения г К-1. При К 2r-1 r 1ода(К+1) I. В первом из рассмотренных случаев входная информационная шина Xj, для которой вес разряда входного кода O)j имеет в двоичном представлении значения его остатка по модулю К единичные разряды с номерами а, соединяется с группами входных информационных шин с весами, равными 2 м . Во втором случае разряд с весом щ входного кода соединяется с группой входных информационных шин, имею- щей веса входов, равные ( u)j)modK. На группу входных и информационных шин подаются разряды ходного кода с весами ш либдо имеющие в двоичном представлении числа (uJj)modK единицу в разряде с весом ш. Число С групп входных информационных шин выбирается равным С 1, 2,...,.

Многоканальный преобразователь параллельного кода в последовательности импульсов может быть выполнен, как и в устройстве-прототипе, в виде распределителя импульсов, выходы которого соединены с первыми входами элементов И р CI групп (р-число каналов преобразователя), вторые входы элементов И каждой группы являются входами соответствующего канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которого является выходом соответствующего канала преобразователя, тактовый вход распреде- лителя импульсов является тактовым входом преобразователя, а выход последнего разряда распределителя - выходом конца

работы преобразователя,

Блок подсчета единиц по модулю К выполнен в виде реверсивного счетчика по модулю К с двумя счетными входами, прямые выходы разрядов которого соединены с входами элемента ИЛИ, соединенного прямым выходом с первым выходом блока, а инверсным - с его вторым выходом.

0

5 0 5 0

0

0

5

5

Счетчик по модулю К 2г-1 содержит г счетных триггеров 12, г элементов ИЛИ 13, элемент И 14, элемент ИЛИ 15, счетные входы 16, вход 17 сброса, и выходы 18. Элемент ИЛИ 13.1 соединен первым входом с i-м счетным входом счетчика с весом , вторым входом - с выходом переноса (i-1)- го триггера, а выходом - со счетным входом i-ro триггера 12.i, элемент ИЛИ 13.1 соединен вторым входом с выходом переноса триггера 12.г. Прямые выходы триггеров 12 соединены с входами элемента И 14, соединенного выходом с первым входом элемента ИЛИ 15, второй вход которого соединен с входом сброса счетчика, а выход-с входами сброса триггеров 12.

В случае произвольного модуля К счетчик 5 содержит счетные входы 16, вход 17 сброса, выходы 18, группу элементов ИЛИ 19, элемент ИЛИ 20, сумматор 21 по модулю К, регистры 22 и 23 памяти, инвертор 24. i-й счетный вход счетчика по модулю К соединяется с входами элементов ИЛИ 19J таких, что в j-x разрядах двоичного представления числа (О имеется единица, элемент ИЛИ 20 соединен входами со счетными входами счетчика по модулю К, выход элемента ИЛИ 19.J соединен с первым входом j-ro разряда сумматора 21 по модулю К, выходы которого соединены с информационными входами регистра 22 памяти, соединенного входом разрешения записи с выходом элемента ИЛИ 20 и входом инвертора 24, а выходами

-с информационными входами регистра 23 памяти, соединенного входом разрешения записи с выходом инвертора 24, а выходами

-с второй группой входов сумматоров по модулю К 21 и выходами счетчика 18, входы сброса регистров 22 и 23 памяти соединены С входом сброса 17 счетчика по модулю К.

Устройство работает следующим образом.

В исходном состоянии счетчик 5, блоки 6 подсчета единиц по модулю К, триггер 3 и многоканальный преобразователь 1 параллельного кода в последовательности импульсов сброшены. При этом на выходах счетчика 5, счетчиков блоков 6 и триггера 3 имеются нулевые логические сигналы. На входы 9 устройства подается контролируемый код. При этом на входы каждой группы 9.i подаются разряды входного кода с одинаковыми значениями остатков их весов по модулю К.

Тактовые импульсы поступают на тактовый вход многоканального преобразователя 1 параллельного кода в последовательности импульсов с выхода генератора 2 тактовых импульсов. При этом на

i-м выходе многоканального преобразователя 1 (выходе его i-ro канала), где i 1, 2р, параллельный входной код преобразуется в последовательность импульсов, число которых равно числу единичных сигналов на соответствующей группе входов 9.I. Импульсы с первого выхода преобразователя 1 поступают на вход элемента ИЛИ 4.1 и с его выхода на соответствующий счетный вход счетчика 5 по модулю К, к содержимому которого каждый раз прибавляется код числа (О(, равного остатку по модулю К весов разрядов входного кода, поданных на информационные шины 9.1. Импулсы с выхода i-ro канала (i 2,...,р) многоканального преобразователя 1 поступают на суммирующий счетный вход блока 6.(Ы) подсчета единиц по модулю К, который осуществляет их подсчет по модулю К. По окончании преобразования входного кода многоканальный преобразователь 1 параллельного кода в последовательности импульсов самоблокируется и далее импульсов на своих информационных выходах не формирует. При этом он сигналом с выхода окончания работы в паузу между тактовыми импульсами переключает триггер 3, на выходе которого появляется единичный логический сигнал, разрешающий прохождение тактовых импульсов через элементы И 7. Пусть блок 6.i подсчета единиц по модулю К является наименьшим по номеру и на его первом выходе имеется единичный сигнал, означающий, что за время работы преобразователя 1 на его счетный вход поступило число импульсов, не кратное К, при этом на всех входах элемента И 7.i, соединенных с выходами вторыми блоков 6.1-6.(i-1) подсчета единиц по модулю К имеются единичные сигналы. Тактовые импульсы с выхода генератора проходят через элемент И 7.I на его выход и поступать на вычитающий счетный вход блока 6.i подсчета единиц по модулю К, от содержимого которого каждый раз вычитается единица. Одновременно импульсы с выхода элемента И 7.i поступают на вход элемента ИЛИ 4.J и с его выхода на суммирующий счетный вход счетчика 5 по модулю К, к содержимому которого каждый раз прибавляется код числа ей + 1, равного остатку по модулю К весов разрядов входного кода, поданных на группу входных информационных шин 9.(i+1). Работа происходит таким образом до обнуления счетчика блока подсчета единиц по модулю К 6.I, при этом на его первом выходе появляется нулевой логический сигнал, запрещающий прохождение тактовых импульсов через элемент И 7.I, а на втором выходе - единичный, разрешающий прохождение тактовых импульсов через элементы И 7. (i+1)-7. (р-1). Работа происходит в описанном порядке 20 обнуления всех блоков 6 подсчета единиц по модулю К,

при этом на всех входах элемента И 8 оказываются единичные сигналы, что вызывает единичный сигнал на его выходе, свидетельствующий об окончании цикла работы устройства. Результат снимается с выходов 10

счетчика 5 по модулю К.

Устройство может работать и в режиме подсчета количества единиц входного кода по модулю К. Для чего в счетчике 5 по модулю К на его счетных входах 16 устанавливается коммутатор, подключающий все счетные входы к входу с единичным весом при работе в режиме подсчета количества единиц.

Таким образом, предложенное устройство имеет большее быстродействие. Формула изобретения 1. Устройство для контроля двоичного кода по модулю К, содержащее генератор тактовых импульсов, выход которого соединен с тактовым входом многоканального преобразователя параллельного кода в последовательности импульсов, р групп

(р С т, С 1,2г - мощность множества

значений остатков весов разрядов входного

кода по модулю К, используемых при преобразовании) информационных входов которого являются соответствующими информационными входами устройства, первый выход многоканального преобразователя параллельного кода в последовательности импульсов соединен с первым входом первого элемента ИЛИ, выход которого подключен к первому суммирующему входу счетчика по модулю К, выходы которого являются информационными выходами устройства, (1+1)-й выход многоканального преобразователя параллельного кода в последовательности импульсов (i 1,..., р-1) соединен с суммирующим входом i-ro блока

подсчета единиц по модулю К, первый выход которого соединен с первым входом одноименного элемента И, выход (1+r-d)-ro элемента И (d 0С-1) соединен с вычитающим входом одноименного блока подсчета единиц по модулю К и соответствующим входом второго элемента ИЛИ, выход

(t+r-d)-ro элемента И (t 2г) подключен к

вычитающему входу одноименного блока подсчета единиц по модулю К, (р+1)-й выход

многоканального преобразователя параллельного кода в последовательности импульсов соединен с входом триггера, выход которого подключен к вторым входам первого - (р-1)-го элемента И и первому входу

р-го элемента И, второй выход 1-го блока подсчета единиц по модулю К подключен к 0+2)-му входу (i+1)-ro -(р-1)-го элементов И и (+1)-му входу р-го элемента И, выход которого является выходом конца работы устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены третий - r-й элементы ИЛИ, соответствующие входы t-ro элемента ИЛИ подключены к выходам (t+r-d-1)-x элементов И, второй С-й входы первого элемента ИЛИ подключены к выходам (г- d)-x элементов И, (i+2)-e входы первого - (р-1) элементов И объединены и подключены к выходу генератора тактовых импульсов, выходы второго - (г-1)-го элементов ИЛИ соединены с одноименными суммирующими входами счетчика по модулю К.

первый и второй регистры памяти, первый - m-й элементы ИЛИ (m log2(K+1)+1) и элемент НЕ, входы т-го элемента ИЛИ являются соответствующими суммирующими

входами счетчика, входы j-ro элемента ИЛИ

О 1т-1) подключены к входам счетчика,

двоичные представления весов которых имеют единицу в j-м разряде, выход j-ro элемента ИЛИ соединен с входом соответствующего разряда сумматора по модулю К, выходы которого подключены к соответствующим информационным входам первого регистра памяти, выходы которого соединены с соответствующими информационными

входами второго регистра памяти, выходы которого подключены к входам соответствующих разрядов сумматора по модулю К и являются выходами счетчика, выход т-го элемента ИЛИ непосредственно и через

элемент НЕ соединен с тактовыми входами соответственно первого и второго регистров памяти.

Л

VElH

Л

-4 I

Jr

«4j

t

r

«з1 К

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-30—Публикация

1990-05-29—Подача