() УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1981 |

|

SU955103A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Четырехквадрантный умножитель сигналов постоянного тока | 1982 |

|

SU1062725A1 |

| Четырехквадрантный умножитель сигналов постоянного тока | 1981 |

|

SU980104A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| Функциональный преобразователь | 1983 |

|

SU1109765A1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 1990 |

|

RU2007028C1 |

| Стабилизатор инфранизкочастотного сигнала | 1980 |

|

SU900271A1 |

| Следящий умножитель частоты | 1973 |

|

SU447721A1 |

1

Изобретение относится к автоматике и вычислительной технике и может найти применение, в частности для умножения частоты низко- и инфранизкочастотных сигналов.

Известен умножитель частоты, содержащий формирователь импульсов, генератор линейно-изменяющегося напряжения, разделительный конденсатор, ключ, пороговый блок и блок опорного напряжения f,

Недостатком устройства является пониженная точность умножения.

Известен также умножитель частоты, содержащий блок задержки, генератор импульсов, генератор линейноизменяющегося напряжения, запоминающий элемен т, компаратор, цифро-аналоговый преобразователь, счетчик и регистр кода коэффициента умножения .

Недостатком данного умножителя является дискретный характер изменения коэффициента умножения частоты.

Наиболее близким к предлагаемому является умножитель частоты, содержащий формирователь импульсов, под- , ключенный входом к входной шине умножения частоты, а выходом - к входу первого формирователя временных интервалов, выход которого соединен с управляющим входом первого ключа и с входом второго формирователя вре,Q менных интервалов, подключенного выходом к управляющему входу второго ключа, соединенного выходом с шиной нулевого потенциала, а сигнальным выходом - с выходом перврго ин,5 тегратора и сигнальным входом первого ключа, выход которого соединен с входом запоминающего элемента, второй интегратор, выход которого подключен к первому входу компаратора,

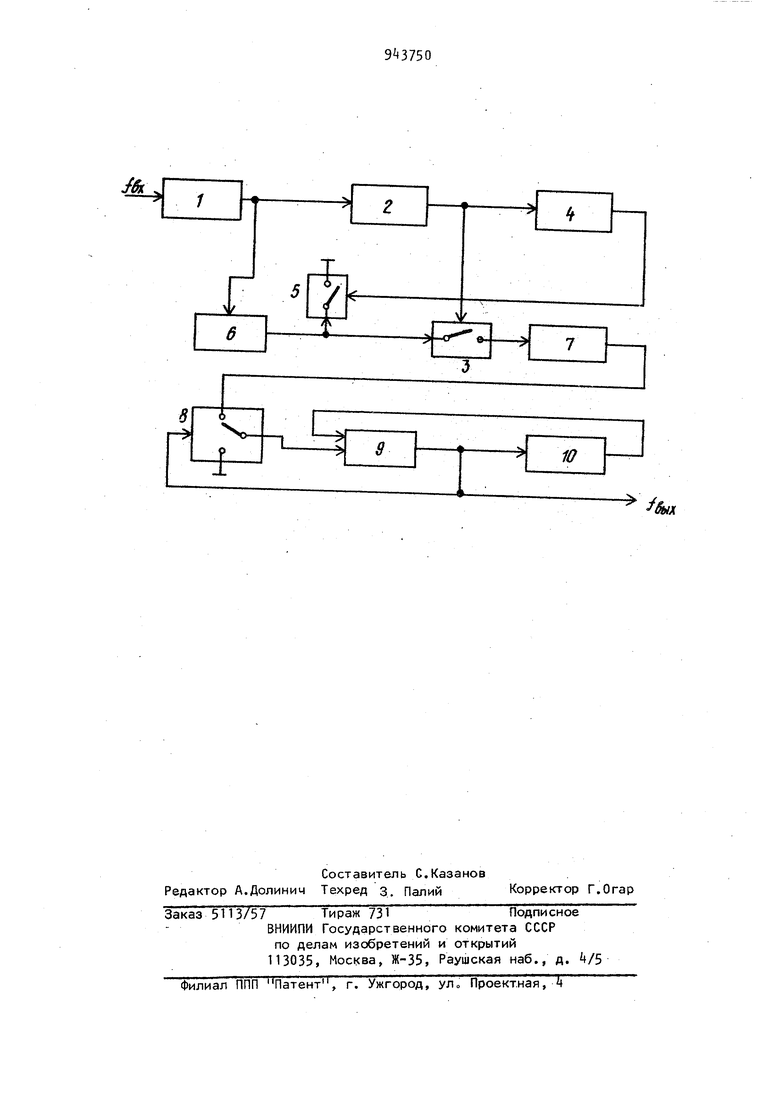

20 соединенного вторым входом с выходом запоминающего элемента, а выходом - с входом одновибратора, подключенного выходом к выходной шине умножителя частоты, входу обнуления второго интегратора и через делитель частоты - к первому входу триггера, соединенного вторым входом с выходом формирователя импульсов, а выходом - с входом блока управления крутизной, подключенного выходом к управляющему входу первого интегратора, соединенного сигнальным входом с сигнальным входом второго интегратора и с выходом блока управления, вход которого через последовательно соединенные функциональный преобразователь напряжения и преобразователь периода в напряжение подключен к выходу второго формирователя временных ИНТ ер валов 43. Недостатком устройства является сложность технической реализации Целью изобретения является упрощение умножителя частоты. Цель достигается тем, что умножитель частоты, содержащий формирователь импульсов, подключенный входом к входной шине умножителя частоты, а выходом - к входу первого формирователя временных интервалов, выход которого соединен с управляющим входом первого ключа и с входом второго формирователя временных интервалов, подключенного выходом к управляющему входу ВТ оро го ключа, соеди не нного выходом с шиной нулевого потенциала, а сигнальным входом - с выходом первого интегратора и сигнальным входом первого ключа, выход которого соединен с входом запоминающего элемент второй интегратор, выход которого подключен к первому входу компаратора, содержит управляемый переключатель, соединенный первым сигнальным входом с выходом запоминающего элемента, вторым сигнальным входом с шиной нулевого потенциала частоты выходом - со вторым входом компаратора, а управляющим входом - с выходом компаратора, входом второго интегратора и с выходной шиной умножителя частоты, причем вход первого интегратора подключен к выходу формирователя импульсов. На чертеже изображена блок-схема умножителя частоты. Устройство содержит формировател 1 импульсов, подключенный входом к входной шине умножителя частоты, а выходом - к входу первого формирователя 2 временных интервалов. Вход, формирователя 2 соединен с управляющим входом первого ключа 3 и с входом второго формирователя k временHfcix интервалов, подключенного выходом к управляющему входу второго ключа 5. Ключ 5 соединен выходом с шиной нулевого потенциала, а сигнальным входом - с выходом первого интегратора. 6 и сигнальным входом ключа 3. Выход ключа 3 подключен к входу запоминающего элемента 7, выход которого соединен с первым сигнальным входом управляемого переключателя 8. Переключатель 8 подключен вторым сигнальным входом к шине нулевого потенциала, а упраляющим входом - к выходу компаратора 9, входу второго интегратора 10 и к выходной шине умножителя частоты. Первый и второй входы компаратора соединены соответственно с выходом интегратора 10 и с выходом переключателя 8. Умножитель частоты работает следующим образомо Входной периодический сигнал поступает на формирователь 1, на выходе которого формируется последовательность импульров постоянной амплитуды UQ, длительность которых равна I ex где К - коэффициент пропорциональности;Т..,- текущий период входного сигнала. Выходные импульсы формирователя поступают на вход интегратора 6. В момент начала очередного импульса на выходе интегратора 6 напряжение равно нулю. К моменту его окончания напряжение на выходе интегратора 6 достигает значения где V постоянная времени инте:- ратора 6. Задний фронт импульса на выхсЯ-ie формирователя 1 запускает формирователь 2, вырабатывающий короткий импульс постоянной длительности, с помощью которого осуществляется замыкание ключа 3 и передача выходно го напряжения U интегратора 6 в запоминающий элемент 7. После этого задним фронтом выходного импульса формирователя 2 запускается формирователь . Формирователь вырабатывает короткий, импульс постоянной длительности, с помощью которого обнуляется интегратор 6 через ключ 5 5 (для обеспечения нормальной работы умножителя необходимо, чтобы сум ма выходных интервалов формирователей 2 и i не превышала паузы в выходной последовательности импульсов формирователя l). Напряжение с выхода запоминающего элемента 7i пропорциональное продолжительности окончившегося периода входного сигнала, поступает на первый сигнальный вход переключа теля 8о Если этот вход подключен к выходу переключателя 8, то на второ (инвертирующем) входе компаратора 9 будет напряжение, равное U. Поэтом в тот момент, когда интегратор 10 разряжен, напряжение на первом (неинвертирующем) входе компаратора 9 равно нулю, и на выходе компаратора 9напряжение равно отрицательному уровню ограничения - Е. Это напряжение действует на входе интегратор 10и на выходе последнего напряжени линейно растет до тех пор, пока не достигнет величины U. В этот момен компаратор 9 переключается, и напря жение на его выходе становится равным положительному уровню ограничения +Ер. Этот уровень переключает переключатель 8, соединяя со вторым входом компаратора 9 нулевую шину умножителя частоты. При этом состоя ние компаратора 9 не изменяется, а выходное напряжение интегратора 10 начинает линейно уменьшаться до нул вого уровня В момент времени пересечения нулевого уровня компаратор 9 переключается, и напряжение на его выходе становится равным -Ед. Переключатель 8 возвращается в исходное положение, подключая выход запоминающего элемента 7 к второму входу компаратора 9 и, аналогично описанно му, начинается формирование следующего периода выходного импульсного сигнала г енератора. Продолжительность его равна Т -J , ВЫХ Ч постоянная времени интегра тора 10. Учитывая пропорциональность периоду Tg, частота fgbix выходной шине умножителя будет связана с вхо ной частотой fg выражением вида i - k -f BblX- i BX) К А.Е il). 2ku, 0 Таким образом, предлагаемое устройство позволяет, по сравнению с известным.упростить техническую реализацию умножения частоты. Дополнительным преимуществом устройства является простота плавного изменения коэффициента умножения :путем изменения постоянных времени Интеграторов, Исследования показали работоспособность умножителя в диапазоне коэффициентов умножения К 10-200. При этом погрешность умножения для частот 0,1-100 Гц не превышает 0,2%. Формула изобретения Умножитель частоты, содержащий формирователь импульсов, подключенный входом к входной шине умножителя частоты, а выходом - к входу первого формирователя временных интервалов, выход которого соединен с управляющим входом первого ключа и с входом второго формирователя временных интервалов, подключенного выходом к управляющему входу второго ключа, соединенного выходом с шиной нулевого потенциала, а сигнальным входом - с выходом первого интегратора и сигнальным входом первого ключа, выход которого соединен с входом запоминающего элемента, второй интегратор, выход которого подключен к первому входу компаратора, о т л и ч а ю щ и и с я тем, что, с целью упрощения умножителя- частоты, он содержит управляемый переключатель, соединенный первым сигнальным входом с выходом запоминающего элементу, вторым сигнальным входом - с шиной нулевого потенциала частоты, выходом - со вторым входом компаратора, а управляющим входом - с выходом компаратора , входом второго интегратора и с выходной шиной умножителя частоты, причем вход первого интегратора подключен к выходу формирователя импульсов. Источники информации, принятые ас внимание при экспертизе 1.Авторское свидетельство СССР № 296215, кл. ;Н 03 В 19/00, 19б9. 2.Авторское свидетельство СССР № 657598, кл. Н 03 В 19/10, 1977. 3.Авторское свидетельство СССР ff 617803, кл. G Об F 7/52, 1976 (прототип).

Авторы

Даты

1982-07-15—Публикация

1979-09-20—Подача