ЧЕТЫРЕХКВАДРАНТНЫЙ УМНОЖИТЕЛЬ

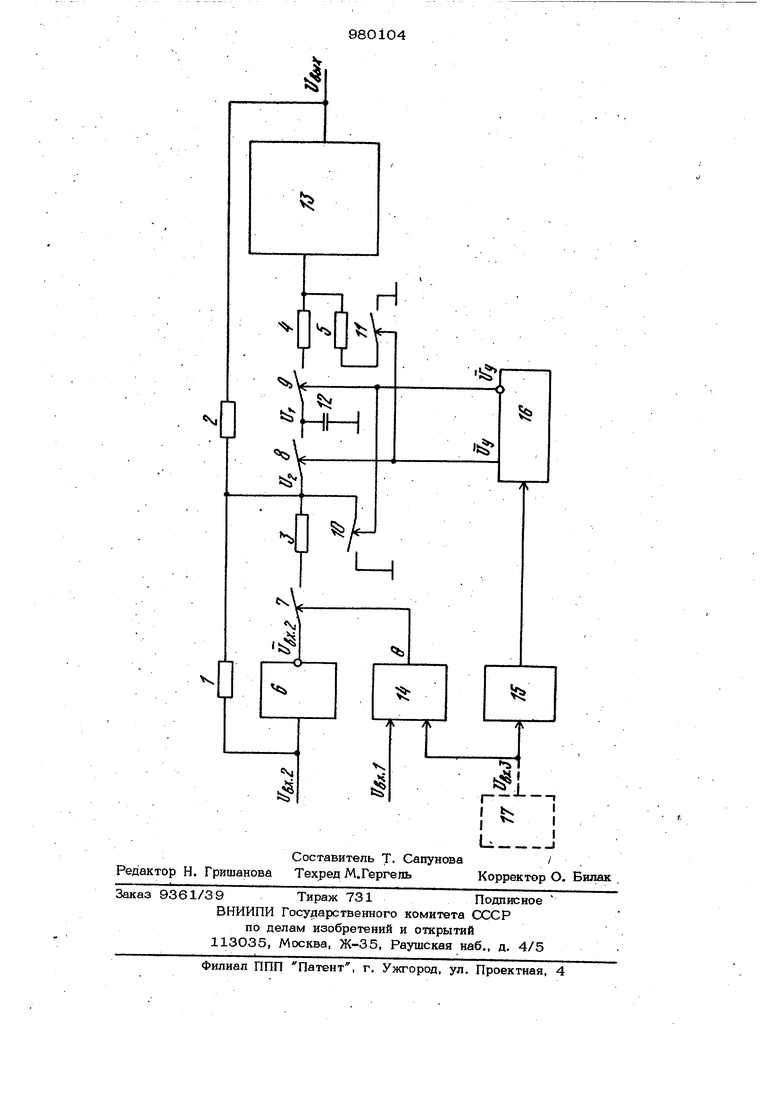

(54) СИГНАЛОВ ПОСТОЯННОГО ТОКА Изобретение относится к аналоговой вычислительной технике и может быть использовано при построении аналоговых и гибридных вычислительных устройств. Известны четырехкваярантные умно)(а1тели сигналов постоянного тока, использующие промежутрчное логарифмирование и содержащие стандартные блоки умножения (типа 525 ПС1), масйтабные резисторы, ключи L 1J . Эти умножители отличаю тся высоким быстродействием, но низкий точностью. Более высокую точность обеспечивают время-импульсные устройства перемножения. Наиболее близким техническим решением к предлагаемому является четырехквадрантный умножитель, содержащий интегратор, инвертор, первый, второй и тре тай масштабные резисторы, соединенные между собой одним из выводов, компаратор, ключ, управляющий вход которого соединен с выходом компаратора, а информадионный вход - с выходом инвертора и вторым выводом третьего масштабного резистора, второй вьгаод первого масштабного резистора соединен с входом инвертора и $тляется первым входом умножителя, второй вывод второго масштабного резистора соединен с выходом интегратора и является выходом умножителя, а первый и. второй выходы компаратора являются вторым и третьим входами умножителя. Умножитель позволяет по-, лучить высокую точность перемножения . сигналов постоянного тока 2J . Однако он имеет малое быстродействие при необходимости получения низкого уров ня пульсаций выходного напряжения, что является большим недостатком при построении быс троде йс ТВующих бычислител f ных устройств. Цель изобретения - повышение быстродействия. Поставленная пель достигается тем, что в известный четырехквадрантный умножитель сигналов постоянного тока, содержащий инвертор, вход которого является первым информационным входом умножите ля, первый ключ, информационный вход ко торого подключен к выходу инвертора, компаратор, входы которого являются соответственно вторым информационным и тактовым входами умножителя, а выход подключен к управляющему входу первого ключа, интегратор, выход которого является входом умножителя и три масштабных резистора, первые выводы которьгх объединены, второй вывод первого .масшта ного резистора подключен к входу инвертора, второй вывод второго масштабног резистора подключен к выходу интегратора, а второй вывод третьего масштабного резистора подключен к выходу первого ключа, введены последовательно соединен ные формирователь импульсов и триггер управления, четеертый и пятый масштабные резисторы, второй, третий, четвертый и пятый ключи и запбминающий конденсатор, вхйд формир(жателя импульсов подключен ко второму входу компаратора, первый выход триггера управления по/цслю чен к управляющим входам второго и пятого ключей, а второй выход триггера уп равления подключен к управляющим входа третьего и четвертого ключей, информационные входы второго и четвертого ключей объединешл и подключены к первому выводу третьего масштабного резистора, выход второго ключа и иаформаыионный вход третьего ключа об-ьедкиены и через запоминающий конденсатор подключены к шине нулевого потенциала первый вывод четвертого масштабного резистора подклю чен к вьусоду третьего ключа, а первый вывод пятого масштабного резистора под ключен к информационному входу пятого ключа, вторые выводы четвертого и пятого масштабных резисторов объединены и подключены к входу интегратора, выходы четвертого и пятого ключей подключе ны к шине нулевого потенциала. На чертеже приведена функ1шональная схема четырехквадрантного умножителя сигналов постоянного тока. Четырехквадрантный умнож итель содер жит масштабные резисторы 1 - 5, инвертор 6, ключи 7-11, запомианющий кон.денсатор 12, интегратор 13, компаратор 14, формирователь 15 импульсов,, триггер 16 управления, генератор треугольных импульсов, ; Четырехквадрантный умножитель сигналов постоянного тока работает еледующим образом. На третий вход умножителя от генератора 17 импульсов подаются импульсы, например треугольные. Следовательно, на выходе компаратора 14 формируются прямоугольные импульсы, относительная длительность которых пропорциональна сигналу постоянного TOKaUgy, т. е. & (,5, причем коэффициент К выбирается таким, чтобы . Частота прямоугольных импульсов на выходе триггера 16 управления, подаваемых на управляющие входы ключей 8-11, вдвое ниже частоты импульсов, поступающих от генератора 17., Длительность замкнутого состояния ключа 7 задается величиной 6. Рассмотрим процессы.в установившемся режиме. Предположим, что в первом такте работы ключи 8 и 11 замкнуты, ключи 9 и 10 разомкнуты, а напряжение в начале такта на запоминающем конденсаторе 12 равно нулю. До размыкания ключа 7, которое происходит внутри такта, напряжение на конденсаторе 12 изменяется под действием трех напряже- в момент размыкания ключа 7 напряжение и достиагает значения, которое приближено можно определить по формуле t-Цо ® - )к концу первого такта запоминающий конденсатор разряжается до нуля под действием ( ftbl X ключ 7 разомкнут U -VO V -® 5-UBb1xK4)Подставляя значение 0 в уравнение Ш1я и и решая уравнение относительно ОамуИмеем ;Тд Kg 1 Ка-Кг-Kg и„.и.--U. Г , К4 ГК2.-к,.-к5 -...U..;;. 4 t -« -- ,.-Кс К «1,1 . При условии -j rf-qj -0,5, что соответствует соотношению Ри(Ка) получаем и --0 Iilii5.f ВЫХ bX-l BXl где коэффициенты определяются параметрами схемы. Во втором такте замыкаются ключи 9 и 10 и размыкаются ключи 8 и 11. Поскольку напряжение на запоминающем конденсаторе 12 равно нулю, то выходное i

напряжение интегратора 13 не изменяется. Таким образом, в установившемся режиме пульсации на выходе напряжения отсутствуют. Ключи 10 и 11 исключают влияние конечного сопротивления ключей 8 и 9 н процесс в схеме, улучшая ее работу. В частности, в каждом такте обепечивается постоянное входное сопротивление интегратора. В переходном режиме умножитель представляется колебательны звеном, в котором коэффициент колебательности и постоянная времени определяются номиналами резисторов и конденсаторов. Выбором номиналов резисторов и конденсаторов достаточно просто при заданной точности выбрать минимальное время переходного процесса, которое может составлять величину, соизмеримую с временем такта.

Технико-экономическая эффективность предлагаемого технического решения закЙючается в повышении быстродействия .вьтолнения операции умножения в10 lOOO раз в зависимости от требуемой точности и независимо от скважности входнь1Х сигналов. Это определяется тем, что в предлагаемом умножителе время .переходного процесса может быть достигнуто 2-6 периодов ШИЛ сигнала пря практически нулевой пульсации выходного напряжения. В известных умножителях величина пульсаций зависит от псютоявной времени фильтра. Для достижения пульсации 1% выходного напряжения в прототипе, работающем с точностью 1%, постоянная времени фильтра Тф должна .быть равна 1ОО периодов ШИМ сигнала, тогда время переходного процесса при скачкообразном входном сигнале равно 60О периодов ШИМ сщгнала, т. е. 1ОО ЗООО раз и выше чем в предлагаемом умножителе. При необходимости получить уровень пульсаций 0,1% и точность 0,1% быстродействие сни :ается еще более, чем на порадок. Таким образом, чем точнее необходимо реализовать устройство умножения и чем ниже нужно получить уровен пульсаций выходного напряжения тем выше эффективность применения предлагаемого устройства.

формула изобретения

Четырехквадрантный.умножитель сигналов постоянного тока, содержащий Инвертор, вход которого является первым инфомационным входом умножителя, первый ключ, информационный вход которого подключен к выходу инвертора, компаратор, входы которого являются соответственно вторым информационным и тактовым входами умножителя, а выход подключен к управляющему входу первого ключа, интегратор, выход которого является выходом .умножителя и три масштабных резистора, первые выводы которых объединен второй вывод первого масштабного резистора подключен к входу инвертора, втор вьгеод второго масштабного резистора поключен к выходу интегратора, а второй вывод третьего масштабного резистора подключен к выходу первого ключа, о. т личаюшийся тем, что, с целью повышения его быстродейстия, в него введены последовательно соединенные формирователь импульсов и триггер управления, четвертый и тмтый масштабные резисторы, второй, третий,- четвертый и пятый ключи и запомвнающий конденсатор, вход формир жателя импульсов подключен к второму входу компаратора, первый выход триггера управления подключен к управляющим входам второго и пятого ключей, а второй выход триггера управления подключен к управляющим входам третьего и четвертого ключей, ниформационные входы второго и четвертого ключей объеаинены в пощслючены к первому выводу 1ретьего масштабного резистора, выход второго ключа и информашюнный вход третьего ключа объеанвены к через запоммнакхний коняенсатор, подключены к шине нулевого потенЦяала, первый вывоа четвертого масштабного резнстора подключен к выходу трет|зего клкма, а первый вывод пятого масштабного резистора под ключен к информаоиониому входу пятого ключа; вторые выводы четвертого н пятого масштабных резисторов объединены и подключены к входу интегратора, выхоzuj четвертого и пятого ключей подключены к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1.Аналоговые и цифровые интегральные схемы. Под ред. В. С. Якубовского, М., Сов. радио, 1979, с. 238-239.

2.Грэм Дж. Проектирование и применение операционных усилителей. М., Мир 1974, с. 196-298 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехквадрантный умножитель сигналов постоянного тока | 1982 |

|

SU1062725A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Множительно-делительное устройство широтно-модулированных сигналов | 1983 |

|

SU1095196A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Времяимпульсное множительно-делительное устройство | 1980 |

|

SU1277142A1 |

| Устройство для определения статистических моментов | 1978 |

|

SU723589A1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1644370A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Цифро-аналоговый преобразователь | 1982 |

|

SU1075398A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

Авторы

Даты

1982-12-07—Публикация

1981-06-24—Подача