(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ АЛГЕБРАИЧЕСКИХ ВЫРАЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство слежения за информационной дорожкой носителя оптической записи | 1988 |

|

SU1638724A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

| Широкополосный цифровой фазометр | 1990 |

|

SU1746325A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ ПЕРЕМЕННОГО ТОКА В КОД | 2001 |

|

RU2195767C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

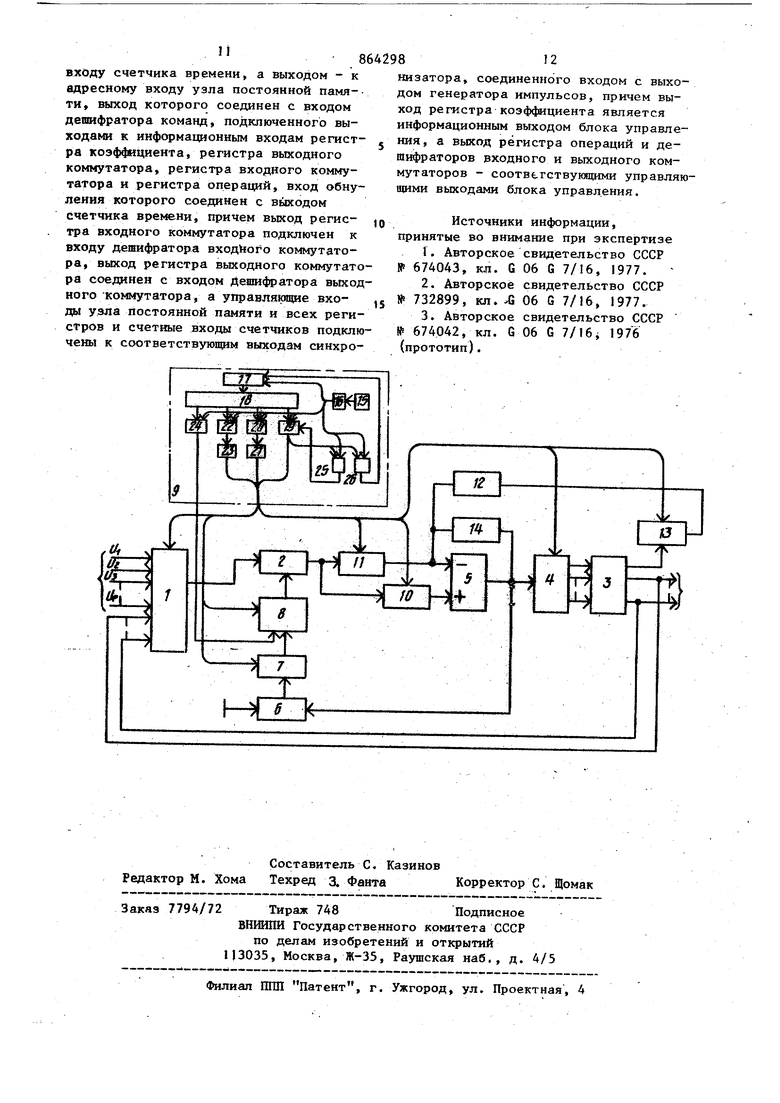

Изобретение относится к автоматик и вычислительной технике и может най применение для вычисления алгебраиче ких выражений, включакнцих в себя выполнение операций умножения, деления сложения и вычитания. Известно вычислительное устройство содержащее группу компараторов, интег раторы блок управления, ключ, управляемый делитель напряжения, умножители, блоки сложения и вычитания, переключатель и генератор опорного напр жения Г 1Известно также вычислительное устройство, содержащее входной коммутатор, интегратор, нуль-орган, группу компараторов, элементы И, блок управления, генератор экспоненциального напряжения и блок регистрации f2J. Недостатком этих устройств являются ограниченные функциональные возможности, так как они могут выполнять только множителЬно-делительные операции и не выполняют операции сложения и вычитания. Наиболее близким к гфедлагаемому является устройство для вычисления алгебраических В1фажений, содержащее входной коммутатор, первая группа сигнальных входов которого подключена к входам устройства, выход - к снгпальноку входу цифроуправляемого делителя напряжения, а вторая сигнальных входов - к выходам устройства и к основной группе выходов блока аналоговых запоминаиЦих ячеек, соединенного входами с выходашс выход- ного коммутатора, подключенного сигнальным входом к первому входу компаратора. Выход которого соединен с сигнальным входом блока преобразования в цифровой код, причем управляю щие входы входного и выходного коммутаторов и блока преобразования в цифровой код соединены с соответствующими управляющими выхода(«1 блока управления, а выход блока преобразования в цифровой код подключен к управляющему входу цифроуправлнемого делителя напряжения , выход которого подключен к первому входу компаратора, соединенного вторым входом с дополнительным выходом входного коммутатора З. Недостатком устройства являются его ограниченные функциональные возможности, не позволяющие выделять, сложные алгебраические выражения, ВКЛ чающие в себя кроме операций умноже ния - деления также операции и сложе ния - вычитания. Цель изобретения - расширение клас са вычисляемых алгебраических выражений, т. е. вычисление сложных алгебраических выражений, включаиицих как операции умножения и деления, так и операции сложения и вычитания. Для эстижения этой цели в устройство для вычисления алгебраических вы ражений, содержащеевходной коммутатор , первая группа сиглальных входов которого подключена к входам устройства, выход - к сигнальному входу ци(й)оуправляемого делителя напряжения, а вторая группа сигнальных входов - к выходам устройства и к основной группе выходов блока аналоговых запокмнакмцих ячеек, соединенного входами с выходами выходного комм5 татора, подключенного сигнальным входом к первому входу компаратора, выход которого соединен с сигнальным входом блока преобразования в цифровой код, причем управлянхцие .входы входного и выходного коммутаторов и блока преобразования в цифровой код соединены с соответствующими управляющими выходами блока управления, дополнительно введены ключи, операционный усилитель масштабные резисторы и мультиплексор цифровых кодов, соединенный первым информационным входом с выходом блока преобразования в цифровой код, вто рым информационным входом - с информационным выходом блока управле ния, I ВЫХОДОМ - с управляющим входом цифро управляемого делителя напряжения,под ключенного выходом к сигнальным входам двух ключей,выход первого из кот рых соединен с неинвертирующим входо операционного усилителя,подключенног i инвертирующим входом к выходу второго ключа и через первый масштабный резистор к выходу третьего ключа,соединенно го сигнальным входом с дополнительным выходом блока аналоговых запоминающи ячеек, а выход операционного усилите 8 ля подключен к первому входу компаратора, и через второй масштабный резистор - к инвертирунмцему входу операционного усилителя, причем второй вход компаратора соединен с шиной нулевого потенциала, а управляющие входы ключей и мультиплексора цифровых кодов подключены к соответствующим управляющим выходам блока управления . Блок управления содержит генератор импульсов, синхронизатор, узел постоянной Памяти, дешифратор команд, регистр операций, регистр и дешифратор входного коммутатора, регистр и дешифратор выходного коммутатора, регистр коэффициента, счетчик времени и счетчик команд, подключеиньш управляющим входом к выходу регистра операций и управляющему счетчика времени, а выходом - к адресному входу узла постоянной памяти, выход которого соединен с входом дешифратора команд, подключенного выходами к информационным входам регистра коэффициента, регистра выходного коммутатора, регистра входного коммутатора и регистра операций, вход обнуления которого соединен с выходом счетчика времени, причем выход регистра входного коммутатора подключен к входу дешифратора входного коммутатора, выход регистра выходного коммутатора соединен с входом дешифратора выходного коммутатора, а управляющие входы узла постоянной памяти и всех регистров и счетные входы счетчиков подключены к соответствующим выходам синхронизатора, соединенного входом с выходом генератора импульсов, причем выход регистра коэффициента является информационным выходом блока управления, а выходы регистра операций и дешифраторов входного и выходного коммутаторов соответствующими управляющими выходами блока управления. На чертеже изображ а блок-схема устройства для вычисления алгебраических выражений. Устройство содержит входной коммутатор I, первая группа сигнальных входов которого подключена к входам устройства, выход - к сигнальному входу цифроуправляемого делителя 2 напряжения, а вторая группа сигнальных входов - к выходам устройства и к основной группе выходов блока 3 аналоговых запомийающих ячеек. Входы блока 3 соединены с. выходами выходного комму татора 4, подключенного сигнальным входом к выходу операционного усилителя 5 и .к первому входу компаратора 6. Компаратор 6 соединен вторым входом с шиной нулевого потенциала, а выходом - с сигнальным входом блока преобразования в, цифровой код. Блок 7 подключен выходом к первому информационному входу мультиплексора 8 цифровых кодов, соединенного вторым информационным входом с информационным выходом блока 9 управления, а вы ходом - с управляющим входом цифроуп равляемого делителя напряжения 2. Вы ход делителя 2 подключен к сигнальным входам двух ключей 10 и П, выход клю ча 10 соединен с неинвертирующим входом операционного усилителя 5. Усилитель 5 подключен инвертирующим входом к выходу второго ключа II и через первьй масштабный резистор 12 - к вы ходу третьего ключа I3, соединенного сигнальным входом с дополнительным выходом блока 3 аналоговых запоминающих ячеек. Выход операционного усиг лителя 5 подключен через второй масш табный резистор 14 к инвертирующему входу усилителя 5. Управляющие входы коммутаторов I и 4, блока 7 преобразования в цифровой код, мультиппексора 8 и ключей 10, 11 и 13 соединены с соответствующими управляющими выходами блока 9 управления. Блок 9 управления может быть илпол нен, например, содержащим генератор 15 импульсов, синхронизатор 16, узел 17 постоянной памяти, дешифратор 18 команд, регистр 19 операций, регистр 20 и дешифратор 21 входного коммутатора, регистр 22 и дешифратор 23 выходного коммутатора, регистр 24 коэффициента, счетчик 25 времени и счетчик 26 команд. Счетчик 26 подключен управлякяцим входом к выходу регистра 19 и к управляющему входу счетчика 25, а выходом - к адресному входу узла 17 постоянной памяти. Выход узла 17 соединен с входом дешифратора 18. Выходы депшфратора 18 подключены к информационньм входам регистров 19, 20, 22 и 24, причем вход обнуления регистра 19 соединен с выходом счетчика 25,. Выход регистра 20 соединен с входом дешифратора 21, выход регист ра 22 - с входом дешифратора 23. Выход регистра 24 является информащюнным выходом блока 9 управления, а выходы регистра 19 и дешифраторов 21 -и .98 23 - управляющими выходами блока 9 управления. Устройство работает следующим образом. Пусть необходимо выполнить операцию вида J, где и и Uj- входные напряжения на первом и втором входах устройства соответственно;а . и а. - нормированные постоянные коэффициенты (а. 1 : . з) ; и - выходное напряжение устройства. Выполиение операции производится за два этапа. На первом этапе блок 9 вырабатывает управляющие и информационный сигналы, которые обеспечивают следующий режим: напряжение U с первого входа .устройства через коммутатор 1 подключается к сигнальному входу делителя 2; выход делителя 2 через ключ 11 подключается к инвертирующему входу усилителя 5; выход усилителя 5 через коммутатор 4 подключается к одной из .запоминающих ячеек,например первой, блока 3; код коэффициента информационного выхода блока 9 управления через мультиплексор 8 подается на управляющий вход делителя 2. В результате (при соответствуюш;им образом заданных соотношениях между коэффициентами d , Кодами, их представляющими , резисторами делителя 2 и резистором 14 в цепи обратной связи усилителя 5) на выходе усилителя 5 сформируется напряжение, равное ( Ц) Это напряжение в конце первого этапа запоминается в первой ячейке блока 3, На втором этапе блок 9 управлений вырабатывает сигналы, которые обеспечивают следующий режим: напряжение U с второго входа устройства через коммутатор I подается на сигнальный вход делителя 2; выход делителя 2 через ключ 10 подключается к неинвертирующему входу усилителя 5; выход усилителя 5 через коммусатор 4 подключается к другой, например второй, ячейке блока 3; выход пер- . вой ячейки через ключ 13 и резистор 12 подключается к инвертирующему входу силителя 5; с информационного выхода блока 9 код коэффициента а через мульиплексор 8 подается на управляющий 786 вход делителя 2. В результате с помощью делителя 2 и усилителя 5 формируется напряжение, равное ajU-, которое суммируется с обратным знаком (величины резисторов 12 и 14 выбраны одинаковыми) с выходным напряжением первой ячейки блока 3 аналоговых запоминающих ячеек, т. е. на вторую ячейку блока 3 с выхода усилителя 5 поступает напряжение, равное При выполнении операции вычисления типа ajU| - 3,112 работа устройства про текает аналогично за тем исключением, что на втором этапе выход делителя 2 подключается через ключ 11 к инвертирующему входу усилителя 5. Пусть необходимо выполнить операции умножения и деления, например операгшю вида и и , J л входные напряже1Шк на первом, втором и третьем входах устройства соответственно;а - нормированный постоянный коэффициент а XI . При выполнении этой операции работа устройства распадается вст времени на три этапа. Первый этап выполняется аналогично первому этапу при вьтолнении операции суммирования за тем исклю чением. Что выход цифроуправляемого делителя 2 напряжения подключается к неинвертирующему входу усилителя 5 че рез ключ 10. В этом случае на выходе первой ячейки блока 3 в конце первого этапа устанавливается напряжение, рав ное aU. Второй этап при выполнении операции умножения-деления вьиолняет - ся аналогично второму этапу при выпол нении Операции суммирования за тем ис ключением, что запрещается работа выходного коммутатора 4 и разрешается р бота блока 7 преобразования в цифрово код, выходной код N которого через мультиплексор 8 поступает на управляющий вход делителя 2. Компаратор 6 сравнигает выходной сигнал усилителя 5 с нулевым потенциалом, а блок 7 в соответствии с выходным сигналом компаратора 6 осуществляет подбор кода N таким образом, чтобы напряжение 1/2 со второго входа устройства скомпенси1 ов ло на усилителе 2 напряжения с выхода первой ячейки блока 3, равное aU . Тогда в конце второго этапа, при равенстве нулю выходного напряжения усилителя 5, коэффициент передачи W по напряжению от сигнального входа делителя 2 до выхода усилителя 5 станет равнымНа третьем этапе выполнения операции умножения-деления блок 9 управления вырабатывает управляющие сигналы, которые обеспечивают следующий режим: на сигнальный вход делителя 2-через коммутатор 1 подключается третий вход (напряжение Uj), ключи 10 и 11 остаются в том же положении-, которое было навтором этапе, ключ 13 размыкается, выход операционного усилителя 5 через выходной коммутатор 4 подключается к одной из ячеек блока 3, в блоке 7 сохраняется код N, полученньтй на втором этапе, который и на третьем этапе через мультиплексор 8 поступает на управляющий вход делителя 2. Тогда в конце третьего этапа на выходе операционного усилителя 5 и на выходе выбранной ячейки блока 3 будет напряжениеТак как в устройстве промежуточные результаты выполнения каждой операции запоминаются в ячейках блока 3. аналоговых запоминающих ячеек, выходы которого подключены к входам входного коммутатора данное устройство может производить автоматическое вычисление сложных рациональных алгебраических вьфажений, включающих последовательное выполнение ари я етических операций над входными аналоговыми сигналами и промежуточными результатами. В этом случае необходимая программа вычислений размещается в узле 17 постоянной памяти блока 9 в виде ци фовых кодов команд. Каждая команда соответствует одному шагу при выполнении той или иной операции, и следовательно, для выполнения операции сложения (вычитания) необходимо иметь две комавды, а для операции умножения-деления - три. Каждая команда содержит код операции, код адреса для входного коммутатора 1, код адреса для выходного коммутатора 4 и код постоянного коэффициента. Текущее содержание счетчика 26 ко манд (адрес команды) поступает в узел 17 постоянной памяти, из которого выбирается очередная команда. Продейгиф:рированный в дешифраторе 18 код операции записывается в регистр 19 опер ций,выходные сигналы которого в завис мости от кода операции) управляют работой ключей 10, 11, 13 мультиплесора 8 и блока 7 преобразования в цифровой код. Кроме того, одиг из сигналов регистра 19 операций управляет работой счетчика 26 команд и счетчика 25 времени. При выполнении длинной по време НИ команды (например, умножение-деление) этот сигнал блокирует изменение содержимого счетчиКа 26 команд и разрешает работу счетчика 25 времени, с помощью которого задается интервал времени, необходимый для вьтолиения длинной команды. По окончании этого интервала сигнал со счетчика 25 времени обнуляет регистр 19 операций и при этом снимается блокировка со счетчика 26 команд. Коды адресных частей команды за- raiCbraaioTCH соответственно в регистры 20 и 22 входного .и выходного KOMftyTaторов и после деши4фацни управляют работой соответственно входного 1 и выходного А кo iмyтaтopoв. Код постоянного коэффициента записывается а регистр 24 коэффициента, откуда посту пает иа второй информационный вход мультиплексора 8. Синхронизация работы всех узлов блока 9 управления осуществляется от синхронизатора 16, который вырабатывает последовательность тактирующих импульсов. ВыходwsiM сигналом для синхронизатора яв ляётся сигнал генератора 15 импуль- соа. Предлагаемое устройство позволяет вычислять более сложные алгебраически выражения, в частности выраже мя, содержа1191е операции деления, умножения, сложения и вычитания, т. е. обладает более широкими функциональными возмохНОСТЯК01, причем процесс перехода от одной вычислительной операции к другой при обработке кода входных иапряжений может быть автоматическим. Формула изобретения 1. Устройство для вычисления алгеб раических выражений, содержащее входной коммутатор, первая группа сигналь ных входов которого подключена к вхо8дам устройства, выход - к сигнальному входу цифроуправляемого делите;1я напряжения, а вторая группа сигнальных входов - к выходам устройства и к основной группе выходов блока аналоговых запоминающих ячеек, соединенного входами с выходами выходного коммутатора, подключенного сигнальным входом к первому входу компаратора, выход которого соединен с. сигнальным входом блока преобразования в цифровой код, причем управляющие входы входного и выходного коммутаторов и блока преобразования в цифровой код соединены с соответствующими управляющими выходами блока управления, отличающ е е С Я тем, что, с целью расвлирення класса вычисляемых алгебраических вьч)ажений, в устройство дополнительно введены ключи, операционный усилитель, масштабные резисторы и мультиплексор цифровых кодов, соединенный первым информационным входом с выходом блока преобразования в цифровой код, вторым информационным входом - с информационным выходом блока управления, а выхо- дом - с управляющим входом цифроуправляемого делителя напряжения, подключенного выходом к сигнальным входам двух ключей, выход первого из которьк соединен с неинвертирующим входом операционного усилителя, подключенного инвертирующим входом к выходу второго ключа и через первый масштабный резистор - к выходу третьего ключа, соединенного сигнальным входом с дополнительным выкодом блока аналоговых запоминающих ячеек, а выход операционного усилителя подключен к первому входу компаратора и через второй масЫтабный резистор - к инвертирующему входу операционного усилителя, щ)ичем второй вход компаратора соединен с шиной нулевого потенциала, а управлякхцие входа) ключей и мультиплексора цифровых кодов подключены к соответствующим управляющим выходам блока управления, 2. Устройство по п. 1, отличающееся тем, что блок управсодержит генератор импульсов. ения синхронизатор, узел постоянной памяти, дешифратор команд, регистр операций, регистр и дешифратор входного коьмутатора, регистр и дешифратор выодного коммутатора, регистр коэффнцинта, счетчик времени и счетчик команд одключенный управляющим входом к выхоу регистра операций и управляющему

входу счетчика времени, а выходом - к адресному входу узла постоянной памя- ти, выход которого соединен с входом дешифратора команд, подключенного выходами к информационным входам регистра коэф4ициента, регистра выходного коммутатора, регистра входного коммутатора и регистра операций, вход обнуления которого соединен с выходом счетчика времени, причем выход регистра входного коммутатора подключен к входу дешифратора входного коммутатора, выход регистра выходного коммутатора соединен с входом Дешифратора выходного коммутатора, а управляющие входы узла постоянной памяти и всех регистров и счетные входы счетчиков подключены к соответствующим выходам синхронизатора, соединенного входом с выходом генератора импульсов, причем выход регистра коэффициента является информационным выходом блока управления , а выход регистра операций и дешифраторов входного и выходного коммутаторов - соотвьгствующики управляющими выходами блока управления.

Источники информации, принятые во внимание при экспертизе

Г. Авторское свидетельство СССР № 674043, кл. G 06 G 7/16, 1977.

(прототип).

Авторы

Даты

1981-09-15—Публикация

1979-12-17—Подача