(54) СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий умножитель частоты | 1977 |

|

SU732866A1 |

| Преобразователь частоты импульсов в код | 1983 |

|

SU1156259A1 |

| Умножитель частоты импульсного сигнала | 1972 |

|

SU447823A1 |

| Умножитель частоты | 1983 |

|

SU1167692A2 |

| Преобразователь кода во временной интервал | 1986 |

|

SU1410279A2 |

| ПАССИВНЫЙ КВАНТОВЫЙ СТАНДАРТ ЧАСТОТЫ | 1984 |

|

SU1241959A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| ИЗМЕРИТЕЛЬ АМПЛИТУДНО-ЧАСТОТНЫХ И ФАЗО- ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЧЕТЫРЕХПОЛЮСНИКОВ | 1968 |

|

SU212362A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Телевизионное следящее устройство | 1982 |

|

SU1019672A2 |

I

Устройство относится к электроизмерительной и вычислительной технике. Известен умножитель частоты импульсов, выполненный в виде следящей системы с релейным управлением, содержащей фазовый компаратор, интегрирующий усилитель, генератор импульсов з равляемой частоты, делительчастоты, два клпбча и разн6 оляф яые источники опорного напряжения, подключаемые к входу интегратора в зависимости от знака разности фаз входного сиг яала обратной связи.

такой умножитель частоты характеризуется фазовой погрешностью, обусловленной нечувствительностью устройства к изменениям фазы входного сигнала в пределах 21Г и склсишостью к возникновению автсжолебаний,

Целью изобретения является повышение точности умножителя.

Это достигается тем, что в устройстве фазовый компаратор выполнен в виде реверсивного счетчика с ключами на входах, прячем управляющие входы этих ключей соединены с выходами схем ИЛИ, входа

которых подключены к соответствующим выходам Триггеров реверсивного счетчика.

Такое включение позволяет обеспечить ре.лейно-пропориисшальный режим работы умножнтеля частоты.

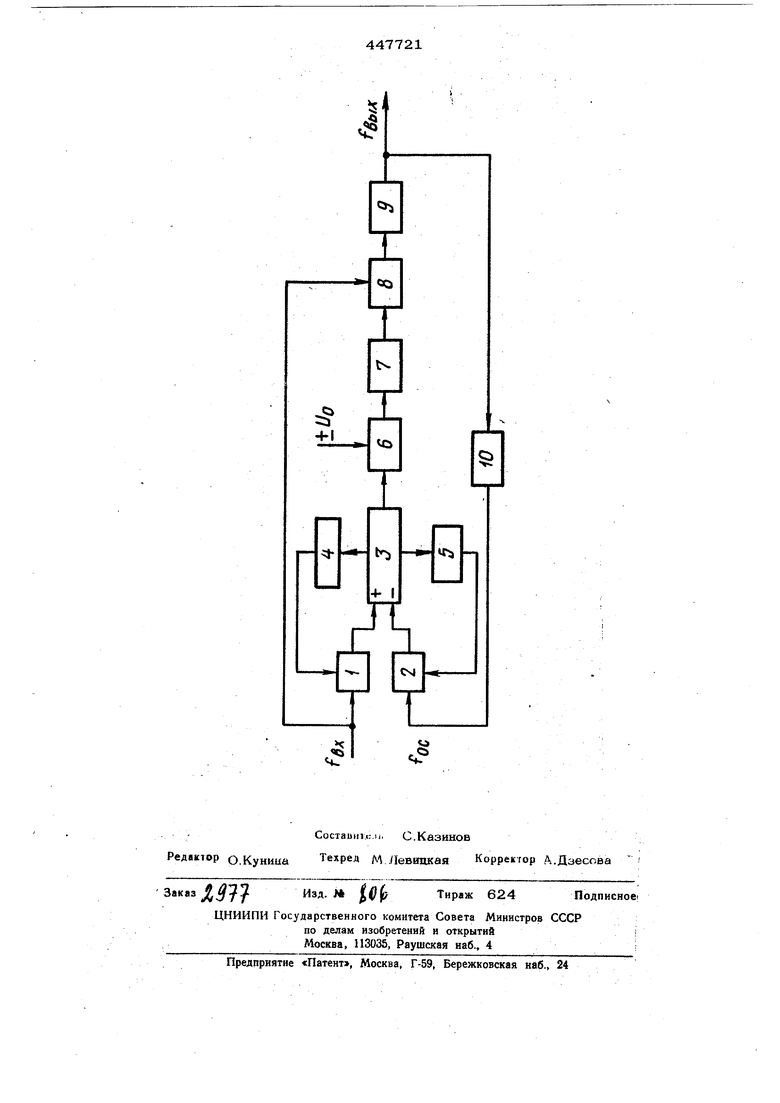

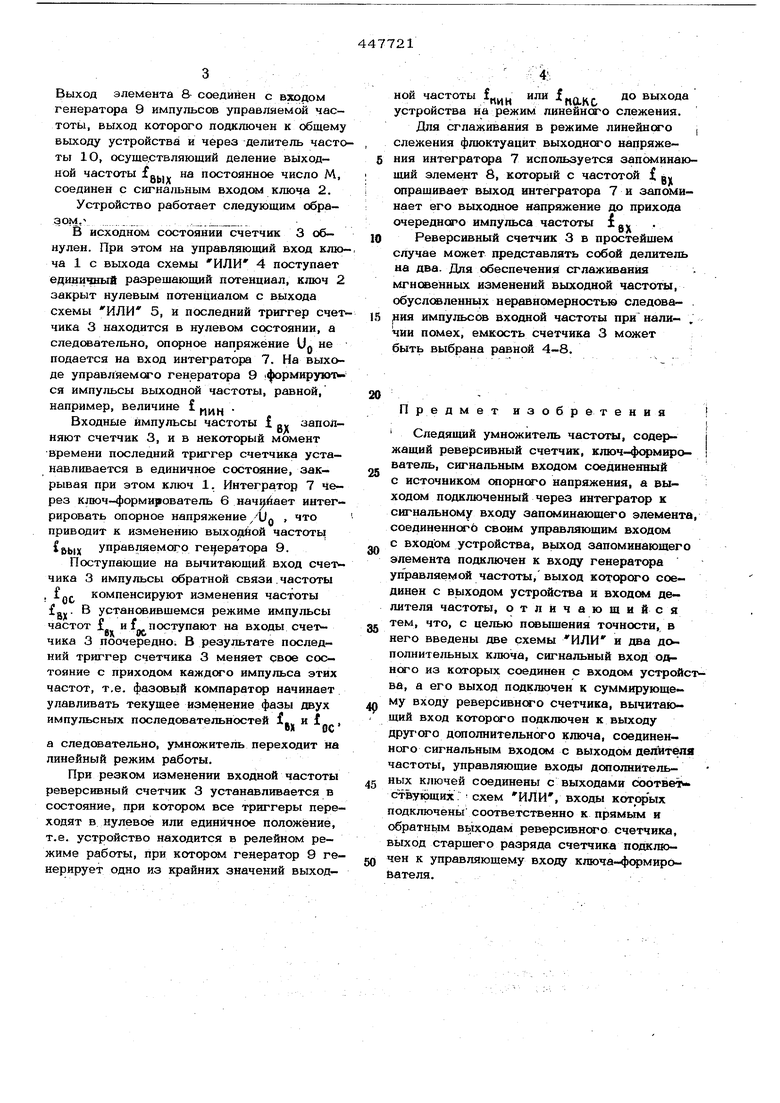

На чертеже изображена структурная

схема умножителя частоты.

Устройство содержит ключи 1, 2, выходы )ых соединены соответственно с суммнрующим и вычитающим входами реверсивнся о счетчика 3. Управляющие входы ключей 1, 2 соединены с выходами схем ИЛИ 4, 5, входы которых подключены соответственно к инверсным и прямым выходам триггере счетчика 3. Прямой выход последнего триггера счетчика 3 подключен также к управ/гающему входу ключа-формирсеателя 6, на сигнальный вход которого подается опорное напряжение - U j Выход ключа-формирователя 6 соединен с входом HHTerpaTcqia 7, выход которого подключен к сигнальному входу запсминаюшего элемента 8, соедивеннсго своим управляющнм вхояелл с общим входом уст ррйства в сигнальным ъкоаом ключа 1.

Выход элемента 8 соединен с входом генератора 9 импульсов управляемой частоты, выход которого подключен к общему выходу устройства и через -делитель частоты 1О, осуществляющий деление выходной частоты fai.iv на постоянное число М,

оых соединен с сигнальным входом ключа 2.

Устройство работает следующим образом, .,; .

В исходном состоянии счетчик 3 обнулен. При этом на управляющий вход клю ча 1 с выхода схемы ИЛИ 4 поступает единичный разрещающий потенциал, ключ 2 закрыт нулевым потенциалом с выхода схемы ИЛИ 5, и последний триггер счет чика 3 находится в нулевом состоянии, а следовательно, опорное напряжение U/j не подается на вход интегратора 7. На выходе управляемся о генератора 9 формирукэт ся импульсы выходной частоты, равной, например, величине y .

Входные импульсы частоты i gv заполняют счетчик 3, и в некоторый момент времени последний триггер счетчика устанавливается в единичное состояние, закрывая при этом ключ 1. Интегратор 7 через ключ-формирователь 6 начийает интегрировать опорное напряжение /UQ , что приводит к изменению выходйой частоть вых управляемого rei epaTOpa 9.

Поступающие на вычитающий вход счет чика 3 импульсы обратной связи. частоты . f-, компенсируют изменения частоты fg В установившемся режиме импульсы частот и f поступают на входы счетчика 3 поочередно. В результате последний триггер счетчика 3 меняет свое состояние с приходом каждсгО импульса этих частот, т.е. фазовый компаратор начинает улавливать текущее изменение фазы двух импульсных последс ательностей 1... и I ,

а следовательно, умножитель переходит на линейный режим работы.

При резком изменении входной частоты реверсивный счетчик 3 устанавливается в состояние, при котором все триггеры переходят в нулевое или единичное положение, т.е. устройство находится в релейном режиме работы, при которсйм генератор 9 генерирует одно из крайних значений выход..,- :. -.4:: ,

ной частоты или макс выхода устройства на режим линейного слежения.

Для сглаживания в режиме линейнсг о , слежения флюктуацит выходного напряжения интегратора 7 используется запоминающий элемент 8, который с частотой f gu опрашивает выход интегратора 7 и запоминает его выходное напряжение до прихода очередного импульса частоты Igv

Реверсивный счетчик 3 в простейшем случае может представлять собой делитель на два. Для обеспечения сглаживания мгновенных изменений выходной частоты, обусл жленнь1х неравнсмерностью следова- .

рия импульсе входной частоты при нали- , чии помех, емкость счетчика 3 может быть выбрана равной 4-8.

Предмет изобретения

Следящий умножитель частоты, содержащий реверсивный счетчик, ключ-ф фмирователь, сигнальным входом соединенный с источником опорнсго напряжения, а выходом подключенный через интегратор к сигнальному входу запоминающего элемента, соединенногб своим управляющим входом с входом устройства, вькод запоминающего

элемента подключен к входу генератора управляемой частоты, выход которото соединен с выходом устройства и входе делителя частоты, отличающийся

, тем, что, с целью повышения точности, в него введены две схемы ИЛИ и два дополнительных ключа, сигнальный вход одного из которых соединен с вход1ж устройства, а его выход подключен к суммирующеJ му входу реверсивного счетчика, вычитающий вход которого подключен к выходу другого дополнительного ключа, соединенного сигнальным входом с выходом делителя частоты, управляющие входы дсяолнительных ключей соединены с выходами соотве-Ь ствующих. схем ИЛИ, входы подключены соответственно к прямым и обратным выходам реверсивного счетчика, выход старшего разряда счетчика подключен к управляющему входу ключа-ф фмир6Вателя.

::S -Ы

Л

V

Авторы

Даты

1974-10-25—Публикация

1973-04-16—Подача