(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU843216A1 |

| Цифровой вольтметр | 1985 |

|

SU1337791A1 |

| Устройство для измерения фазового сдвига | 1984 |

|

SU1190294A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2326391C1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Вероятностный аналого-цифровой преобразователь | 1987 |

|

SU1531216A1 |

Изобретение относится к измерительной технике при преобразовании аналоговых величин в цифровые.

Известен аналого-цифровой преобразователь последовательного приближения, содержащий цифроаналоговый преобразователь, компаратор, входной усилитель и блок управления til

Недостатком этого устройства является сложность блокоуправления и ограниченные функциональные возможности, так как оно не позволяет получать значения преобразования в последовательном коде.

Наиболее близким по технической суш- ности к изобретению является аналогоцифровой преобразователь последовательного приближения, содержащий цифроана логовый преобразователь, триггерный регистр результата преобразования, компаратор, сдвиговый регистр, триггер и генератор тактовых сигналов. В сдвиговом регистре последовательно, начиная с первого такта, передвигается сигнал

1, устанавливающий триггеры регистра в состояние . С выходов тригт рного регистра код поступает на ивфроаналоговый преобразователь, триггеры остаются в состоянии 1, или переключаются в состояние .О, в зависимости от результата сравнения компаратором входного сигнала и сигнала с выхода цн чхюва- логового преобразователя в соответствующем такте. Таким образом, в триггерном регистре устанавливается код результата преобразования, который в параллельном виде поступает на выходы устройства Г2 .

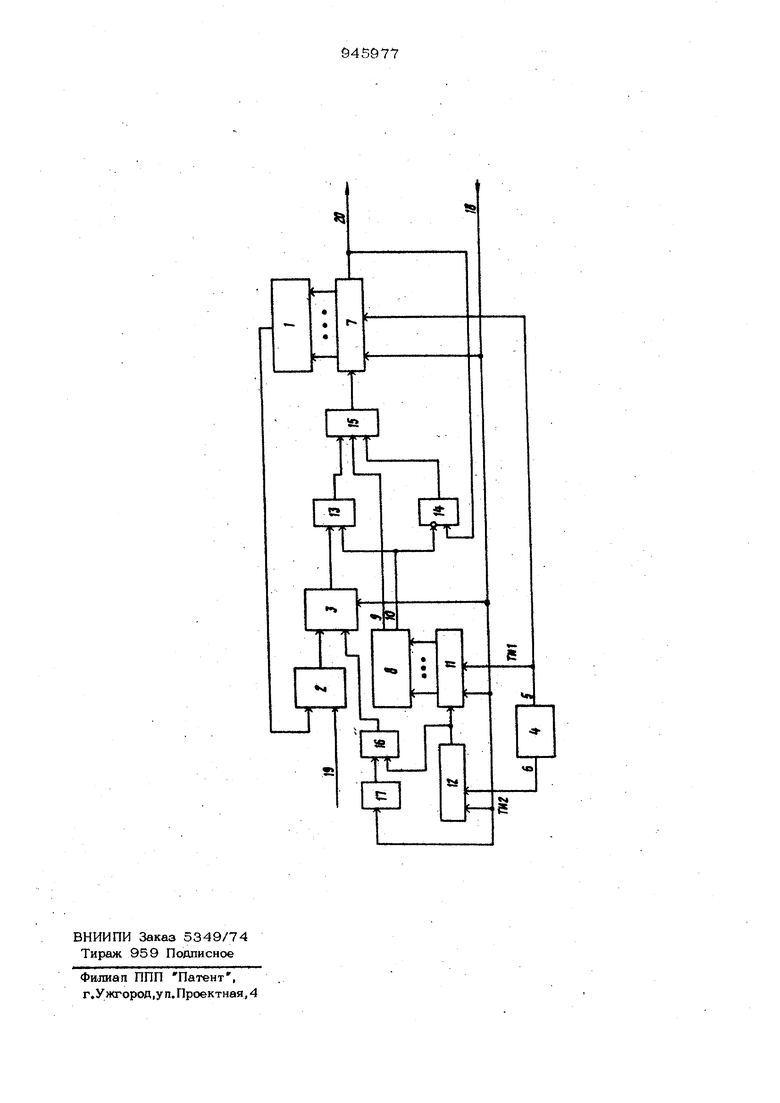

Недостатком этого устройства является сложность блока управления, требу кяце и триггерного регистра и сдвигового регистра, а также невозможность получения значения преобразования в последовательном коде, начиная с младшего разряда, что усложняет обработку результатов прео азования, напри}иер определение среднего значения, путем последовательного поразрядного сложения текущ отсчетов. Цель изобретения - расширение функц ональных возможностей. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий компаратор, первый,вход которого подключен к выходу цифроана- логового преобразователя, входами соеди ненного с выходами сдвигового регистра а выход подключен к первому входу триг гера, второй вход компаратора соединен с шиной входного сигнала, а первый выход генератора подключен к тактовому входу сдвигового регистра, управляющий вход которого подключен к второму вход триггера и к шине начальной установки, введены первый и второй, элементы ИЛИ, одновибратор, первый и второй элементы И, дешифратор, счетчик и делитель, причем выход первого элемента ИЛИ подклю чен к входу сдвигового регистра, выход второго элемента ИЛИ подключен к третьему входу триггера, выход которого соединен с первым входом элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а третий вход соединен с первым выходом дешифратора, второй выход которого подключен к инверсному входу второго элемента И и к второму входу элемента И, а выходы дешифратора подключены к выходам счетчика, управляющий вход которого подключен к управляющим входам сдвигового регистра, делителя и одновибратора, а тактовы вход счетчика подключен к первому выходу генератора, второй выход которого соединен с тактовым входом делителя, выход которого подключен к входу счетчика и к первому входу второго элемент ИЛИ, второй вход которого соединен с выходом одновибратора, причем выход сдвигового регистра соединен с вторым входом второго элемента И. На чертеже представлена структурная схема аналого-цифрового преобразовател Предлагаемый преобразователь содержит цифроаналоговый преофазователь 1 компаратоп 2, триггер 3, генератор 4 с выходами 5 и 6, сдвиговый регистр 7 дешифратор 8 с выходами 9 и 1О, счетчик 11, делитель 12, элементы И 13 и 14, элементы ИЛИ 15 и 16, одновибратор 17, шину 18 начальной установки, шину 19 входного сигнала и шину 2 О выходных сигналов. Рассмотрим, работу устройства на конкретном примере десятиразрядного аналого-цифрового преобразователя. Импульс начальной установки (НУ), поступающий на шину 18 начальной установки, устанавливает триггер 3, счетчик 11 и делитель 12 в нулевое состояние. Сдвиговый регистр 7 также устанавливается этим и myльcoм в начал1 ное положение - в старшем разряде 1, а в остальных разрядах О..Этот код поступает на входы цифроаналогового преобразователя 1 и превращается в аналоговый эквивалент, который сравнивается с входным I сигналом. Результат сравнения (I, если входной сигнал больше, либо О, если входной сигнал меньше сигнала с выхода цифроаналогового преобразователя 1) импульсом с одновибратора 17, запускаемого зад- ним фронтом импульса начальной установки, через элемент ИЛИ 16 записывается в триггер 3. Тактовые импульсы с выхода 5 генератора 4, образу юцие последовательность тактовых импульсов, поступают на тактовый вход сдвигового регистра 7. С каждым таким импульсом 1 , записанная в начальный момент в старший разряд, сдвигается на одну позицию в сторону младших разрядов. До тех пор, пока на выходах 9 и 10 дешифратора 8 присутствуют , информация с выхода сдвигового регистра (младший разряд) переписывается на его же вход (старший разряд) через открытый элемент И 14 и элемент ИЛИ 1 5. Счетчик 11 считает по модулю Р, где Р - число разрядов преобразования, а значит и разрядность сдвигового регистра 7, и для данного случая равно 10. В момент, когда счетчик 11 находится в состоянии 8 (Р-2), на выходе .9 дешифратора 8 появляется 1 , которая поступает на вход сдвигового регистра 7 через элемент ИЛИ 15. Эта единица заносится в старший разряд сдвигового регистра 7 следующим девятым тактовым импульсом, приводящим счетчик 11 в состояние 9 (Р-1). Это состояние также фиксируется дешифратором 8 и на его выходе 10 появляется 1, котопая запирает элемент И 14 и подключеет к входу сдвигового регистра 7 через открытый элемент И 13 и элемент ИЛИ 15 выход триггера 3. Следующим десятым тактовым импульсом результат сравнения, хранящийся в триггере 3, записывается в старший разряд сдвигового регистра 7. Таким образом, в сдвиговом регистре 7 к этому моменту времени в старшем 10-ом разряде находится результат сравнения входного сигнала с аналоговым 9талоно 1 двоичного кода с 1 в старшем разряде, а в 9-ом разряде записана . На выходе пифроаналогового преоб разователя присутствует аналоговый эквивалент этого состояния сдвигового регистра 7. Одновременно с тактовыми импульсами ТИ 1генератор 4 генерирует последовательность ТИ 2, поступающую на вход делителя 12 по модуЛю Р(1О). На его выходе появляется и шyльc с запаздыванием на поппериода после десятого импульса ТИ 1. Этот импульс поступает на тактовый вход триггера 3 и заносит результат сравнения присутствующего на выходе цифроаналогового преобразова теля 1 с входным напряжением. Кроме того, этот икоту лье поступает на вход счетчика 11 и изменяет его состояние на единицу. Таким образом, следукнцее состояние 8(Р-2) счетчика 11 позволит занести 1 в восьмой разряд сдвигового регистра 7, а состояние 9(P-i счетчика 11 - в результат сравнения, хранящийся в триггере 3. Дальнейшая работа устройства происходит аналогичным образом до тех пор, пока все разряды сдвигового регистра 7 не будут заполнены соответствующими результатами сравнения, т.е. пока не будет получен десятиразрядный результат преобразования. После этого следующие десять тактовых и тульсов ТИ 1 выдают на выход 2О устройства последовательны код результата. В предлагаемом устройстве сдвиговый регистр объединяет функции многоразрядного триггерного регистра результата и многоразрядного сдвигового регистра известного устройства, что эдачительно упрощает аналого-цифровой преобразователь и снижает аппаратурные затраты на его изготовление. Кроме того, изобретение позволяет получить результат в последовательном двоичном коде, начиная с млад щего разряда без применения дополнитель ного оборудования. Такая функциональная возможность позволяет легко производить операции усреднения измеряемых величин Использование предлагаемого устройства в цифровом зонде Океан и в автономном цифровом измерителе температуры и течения ЦИТТ 4 позволяет сократить аппаратурные затраты и снизить энергопотребление приборов и их стоимость. Формула изобретения Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого подключен к выходу цифроаналогового преобразователя, входами соединенного с выходами сдвигового регистра, а выход подключен к первому входу триггера, второй вход компаратора соединен с щиной входного сигнала, а первый выход генератора подключен к тактовому входу сдвигового регистра, управляющий вход которого подключен к второму входу триггера и к шине начальной .установки, отличающийся тем, что, с целью расширения 4ункциональных возможностей, введены первый и второй элементы ИЛИ, одновибратор, первый н второй элементы И, дещифратор, счетчик и делитель, причем выход первого элемента ИЛИ подключен к входу сдвигового регистра, выход второго элемента ИЛИ подключен к третьему входу триггера, выход которого соединен с первым входом элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а третий вход соединен с первым выходом дешифратора, второй выход которого подключен к инверсному входу второго элемента И и к второму входу первого элемента И, а выходы дещифратора подключены к выходам счетчика, управляющий вход которого подключен к управляющим входам сдвигового регистра, делителя и одновибратора, а тактовый вход счетчика подключен к первому выходу генератора, второй выход которого соединен с тактовым входом делителя, выход которого подклю чен к входу счетчика и к первому входу BTOpojTO элемента ИЛИ, второй вход которого соединен с выходом одновибратора, причем выход сдвигового регистра сое динен с вторым входом второго элемента И. Источники информации, принятые во внимание при экспертизе 1.Шило В. Л. Линейные интегральвые схилы.М., Советское радио , 1979, с. 339-340. 2.Балакай В. Г. и др. Интегральные схемы АЦП и ЦАП. М., Энергия, 1978 с. 45-47 (прототип).

Авторы

Даты

1982-07-23—Публикация

1981-01-09—Подача