Заявляемое изобретение относится к информационно-измерительной и вычислительной технике и может использоваться при оцифровке и сборе аналоговой информации в многоканальных системах различного назначения.

Хорошо известны многоканальные аналого- цифровые преобразователи (АЦП), в которых в течение одного цикла преобразования осуществляется оцифровка всего ансамбля входных сигналов [1,2,3]. Происходит это путём одновременного сравнения всех входных сигналов со ступенчато нарастающим уравновешивающим напряжением. При пересечении уравновешивающим сигналом уровня входного сигнала какого-либо из каналов происходит фиксация соответствующего канального кода. По сравнению с преобразователями, осуществляющими последовательную обработку сигналов, данные структуры, при прочих равных условиях, обладают более высоким быстродействием.

Наиболее близким по технической сущности к заявляемому устройству является многоканальный аналого- цифровой преобразователь [4], состоящий из нескольких ступеней, число которых равно числу обслуживаемых каналов, и общей для всего преобразователя управляющей части, содержащей генератор тактовых импульсов, выход которого через элемент И соединён со счётным входом двоичного счётчика уравновешивающего сигнала, подключенного выходами к информационным входам цифроаналогового преобразователя, соединённого выходом с одним из входов вычитающего устройства, каждая канальная ступень содержит устройство выборки- хранения, компаратор, формирователь импульсов, одновибратор, регистр фиксации выходного кода канала, набор двухвходовых элементов И.

Недостатком преобразователя является большое время, затрачиваемое на получение цифровых отсчётов по всем каналам. Полный цикл преобразования составляет в этом преобразователе 2n тактов, где n- число разрядов выходных кодов.

Целью изобретения является повышение быстродействия преобразователя.

Указанная цель достигается тем, что в известный многоканальный аналого- цифровой преобразователь, состоящий из нескольких канальных ступеней, число которых равно числу обслуживаемых каналов, и общей для всего преобразователя управляющей части, содержащей генератор тактовых импульсов, R-S триггер режима, счётчик старших разрядов уравновешивающего сигнала, цифроаналоговый преобразователь, вычитающее устройство, буферный регистр, два элемента И, двухвходовой элемент ИЛИ, первый выход генератора тактовых импульсов подключён к первым входам элементов И, второй вход первого элемента И соединён с клеммой запуска преобразователя, а выход, через двухвходовой элемент ИЛИ – с S- входом R-S триггера режима, выход которого подключён к второму входу второго элемента И, подключённого выходом к счётному входу старших разрядов счётчика уравновешивающего сигнала, соединённого выходами с информационными входами цифроаналогового преобразователя, выход которого подключён к одному из входов вычитающего устройства, соединённого другим входом с клеммой, на которую подаётся напряжение смещения, каждая канальная ступень преобразователя состоит из устройства выборки-хранения, компаратора, счётчика старших разрядов канального кода, одновибратора, элемента И, трёхвходового элемента ИЛИ, выход трёхвходового элемента ИЛИ через одновибратор соединён с управляющим входом устройства выборки- хранения, выход которого подключён к первому входу компаратора, вторым входом подключённого к выходу цифроаналогового преобразователя, а выходом- к первому входу двухвходового элемента И, соединённого выходом со счётным входом счётчика старших разрядов канального кода, выходы которого соединены с соответствующими входами буферного регистра, выходы которого являются информационными выходами преобразователя, в управляющую часть дополнительно введены второй R-S триггер режима, счётчик младших разрядов кода уравновешивающего сигнала, третий, четвёртый и пятый элементы И, а в каждую канальную ступень - вычитающее устройство, два аналоговых ключа, компарформирователь импульсов, второй, третий и четвёртый элементы И, выход вычитающего устройства управляющей части через первый аналоговый ключ соединён с первым входом вычитающего устройства и выходом второго аналогового ключа, подключённого входом к выходу цифроаналогового преобразователя, второй, вход канального вычитающего устройства подключён к входной клемме соответствующего канала, а выход соединён со входом устройства выборки- хранения, выход компаратора подключён к первым входам второго и третьего элементов И, входу формирователя импульсов, соединённого выходом с первым входом четвертого двухвходового элемента И канальной ступени, выход второго элемента И канальной ступени подключён к счётному входу счётчика младших разрядов канального кода, подключённого выходами к соответствующим входам буферного регистра, выход третьего элемента И каждого канала соединён с первым входом трёхвходового элемента ИЛИ и через второй одновибратор- с управляющим входом второго аналогового ключа соответствующей канальной ступени, выход четвёртого элемента И соединён с вторым входом трёхвходового элемента ИЛИ и через третий одновибратор с управляющим входом первого аналогового ключа соответствующей ступени, S- вход первого R-S триггера режима соединён с третьими входами трёхвходовых элементов ИЛИ канальных ступеней, а выход- с вторыми входами четвёртых элементов И канальных ступеней и первым входом четвёртого элемента И управляющей части, S- вход второго R-S триггера режима объединён с R-входом первого триггера режима и подключён к выходу переполнения счётчика старших разрядов уравновешивающего сигнала и к вторым входам третьих элементов И канальных ступеней, выход второго R-S триггера режима соединён с первыми входами третьего и пятого элементов И управляющей части, вторые входы четвёртого и пятого элементов И управляющей части объединены и подключены к второму выходу генератора тактовых импульсов, выход четвёртого элемента И управляющей части подключён к вторым входам первых элементов И канальных ступеней, а выход пятого элемента И управляющей части соединён с вторыми входами вторых элементов И канальных ступеней, второй вход третьего элемента И управляющей части объединён с вторым входом второго элемента И, а выход соединён со счётным входом счётчика младших разрядов уравновешивающего сигнала, соединённого выходами с информационными входами младших разрядов цифроаналогового преобразователя, выход переполнения счётчика младших разрядов уравновешивающего сигнала подключён к второму входу элемента ИЛИ управляющей части, к R входу второго R-S триггера режима, к управляющему входу буферного регистра, входам обнуления счётчиков младших разрядов канальных кодов и управляющему выходу преобразователя.

Заявляемое устройство отличается наличием в управляющей части второго R-S триггера режима, счётчика младших разрядов управляющего слова, трёх дополнительных элементов И, а в канальных ступенях - двух аналоговых ключей, вычитающего устройства, счётчика младших разрядов канального кода, двух одновибраторов, трёх элементов И, формирователя импульсов и их связями с другими блоками преобразователя.

Анализ показывает, что введение указанных блоков позволяет существенно сократить длительность цикла преобразования.

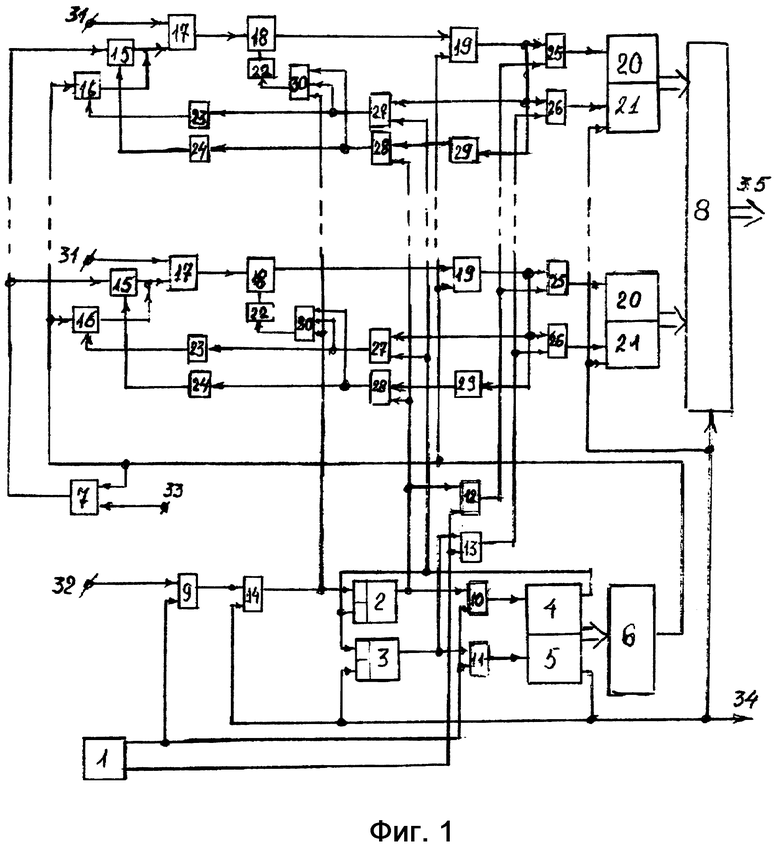

На фиг. 1 представлена блок-схема многоканального аналого- цифрового преобразователя, на фиг. 2- временная диаграмма, поясняющая работу преобразователя.

Многоканальный аналого- цифровой преобразователь состоит из управляющей части, содержащей генератор тактовых импульсов 1, первый 2 и второй 3 R-S триггеры режима, счётчик старших 4 и младших 5 разрядов уравновешивающего сигнала, цифроаналоговый преобразователь 6 (ЦАП), вычитающее устройство 7, буферный регистр 8, первый 9, второй 10, третий 11, четвёртый 12 и пятый 13 элементы И, элемент ИЛИ 14, а каждая канальная ступень содержит первый 15 и второй 16 аналоговые ключи, вычитающее устройство 17, устройство выборки- хранения 18, компаратор 19, счётчик старших 20 и младших 21 разрядов канального кода, первый 22, второй 23 и третий 24 одновибраторы, первый 25, второй 26, третий 27 и четвёртый 28 элементы И, формирователь импульсов 29, трёхвходовой элемент ИЛИ 30, входные клеммы канальных ступеней 31, клемма запуска преобразователя 32, клемма подключения напряжения смещения 33, управляющий выход преобразователя 34, выход буферного регистра 35.

Работу многоканального аналого- цифрового преобразователя (АЦП) рассмотрим на примере четырёхразрядного преобразователя фиг. 1 и 2.

В исходном состоянии триггеры режима, буферный регистр и все двоичные счётчики преобразователя находятся в нулевых состояниях. Входные клеммы подключены к источникам аналоговых сигналов, а на первом и втором выходах генератора тактовых импульсов (ГТИ) формируются периодические последовательности импульсов одинаковой частоты, сдвинутые друг относительно друга на половину периода. Все компараторы преобразователя находятся в единичных состояниях.

Стартовый импульс в момент t1, поступающий на клемму 32, выделяет на выходе первого элемента И 9 импульс ГТИ 1 с первого выхода, который через элемент ИЛИ 14 переводит первый R-S триггер режима 2 в единичное состояние. Одновременно, через трёхвходовой элемент ИЛИ запускаются одновибраторы 22 каждого канала, под действием которых в устройствах выборки- хранения фиксируются значения первых выборок входных сигналов, которые подаются на первые входы компараторов. При этом импульсы с первого выхода ГТИ через открытый элемент 10 начинают поступать на счётный вход счётчика старших разрядов 4 уравновешивающего сигнала, а импульсы со второго выхода ГТИ через открытый элемент И 12 и элементы И 25 канальных ступеней – на счётные входы счётчиков старших разрядов 20 канальных кодов. На выходе цифроаналогового преобразователя (ЦАП) 6 формируется ступенчато нарастающий уравновешивающий сигнал с шагом

q1 = 2n2 q,

где: q = Хmax/2n – вес младшего разряда преобразователя, а n2- число разрядов счётчиков младших разрядов уравновешивающего сигнала и канальных кодов. В нашем примере n2=2 и соответственно q1 = 4 q. Уравновешивающий сигнал с выхода ЦАП 6 подаётся на второй вход компараторов, на вход второго аналогового ключа и на первый вход вычитающего устройства 7 управляющей части, на второй вход которого с клеммы 33 в качестве вычитаемого подаётся напряжение q1. На выходе вычитающего устройства формируется сигнал, уровень которого соответствует уравновешивающему сигналу на предыдущем такте. Начинается первый этап цикла кодирования входных сигналов.

В момент пересечения уравновешивающим сигналом уровня очередной выборки входного сигнала компаратор 19 соответствующей ступени переходит в нулевое состояние, закрывая по первому входу элемент И 25 этого канала. Подсчёт импульсов счётчиком старших разрядов канального кода прекращается. В счётчике фиксируются старшие разряды выходного кода данного канала. На временной диаграмме в момент t2 уравновешивающий сигнал пересекает уровень выборки Х2.(t1). Компаратор этого канала переходит в нулевое состояние. В результате, в счётчике старших разрядов второго канала фиксируется один импульс, вес которого равен четырём квантам преобразователя. Одновременно на выходе формирователя импульсов 29 появляется сигнал, который обеспечивает подключение к первому входу вычитающего устройства канала задержанного значения уравновешивающего сигнала и фиксацию разности между кодируемой выборкой и значением уравновешивающего сигнала на предыдущем такте в устройстве выборки- хранения соответствующей канальной ступени. Компаратор соответствующей ступени при этом переходит в единичное состояние. Если же в течение первого этапа работы пересечения уровня кодируемой выборки не происходит, то по сигналу переполнения счётчика старших разрядов уравновешивающего сигнала через элемент И 27 соответствующей ступени осуществляется подключение к первому входу вычитающего устройства 17 уравновешивающего сигнала и в соответствующем устройстве выборки- хранения фиксируется разность межу кодируемой выборкой (в нашем примере Х1(t1)) и максимальным значением уравновешивающего сигнала на этом этапе (момент t4 на фиг. 2.). В этот момент осуществляется переход преобразователя ко второму этапу работы.

Импульс переполнения счётчика старших разрядов уравновешивающего сигнала переводит в нулевое состояние первый 2 и в единичное состояние второй 3 R-S триггеры режима. При этом закрывается элемент И 10 и открывается элемент И 11 управляющей части, обеспечивающий поступление тактовых импульсов с первого выхода ГТИ на счётный вход счётчика младших разрядов уравновешивающего сигнала 5. Одновременно тактовые импульсы со второго выхода ГТИ через элемент И 13 и элементы И 26 канальных ступеней подаются на счётные входы счётчиков младших разрядов канальных кодов 21. Фиксация кодов в счётчиках младших разрядов канальных кодов 21 происходит аналогично описанному. Так до срабатывания компаратора во втором канале (момент t7), на счётчик успевают пройти три импульса. В результате, общий код, зафиксированный в счётчике второго канала, оказывается равным числу 7 = 1х4 +3. (фиг. 2) . К концу цикла в счётчике первого канала оказывается зафиксировано число 13 = 3х4 + 1. Импульс переполнения счётчика младших разрядов уравновешивающего сигнала осуществляет перезапись полученных кодов в буферный регистр, обнуляет счётчики канальных кодов, запускает следующий цикл преобразования и передаёт сигнал в центральный процессор о готовности преобразователя к передаче полученных данных. Считывание данных из буферного регистра может осуществляться в течение всего следующего цикла преобразования.

Введённые изменения позволили в рассмотренном четырёхразрядном АЦП сократить длительность цикла преобразования в 2,75 раза. По мере увеличения разрядности преобразователей эффективность возрастает. Так для восьмиразрядного АЦП цикл сокращается в 8 раз, для 10- ти разрядного – в 16, а для 12- ти разрядного в 32 раза.

Использованные источники

1. Темников Ф.Е. Теоретические основы информационной техники. “Энергия”1979, с.116, рис.3-18.

2. Авторское свидетельство СССР № 153399, кл. H03К 13/20, 1962.

3. Авторское свидетельство СССР № 668 084, кл.Н03К 13/02, 1979.

4. Авторское свидетельство СССР № 1040599, кл.Н03К 13/02, 1983.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ и устройство аналого-цифрового преобразования | 2023 |

|

RU2805973C1 |

| Интегрирующий аналого-цифровой преобразователь | 2023 |

|

RU2802872C1 |

| Устройство для централизованного контроля параметров | 1991 |

|

SU1807451A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1748253A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Следящий аналого-цифровой преобразователь | 1978 |

|

SU780184A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Логарифмический преобразователь напряжения в код | 1979 |

|

SU917337A1 |

| УМНОЖИТЕЛЬ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2839987C1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

Изобретение относится к информационно-измерительной и вычислительной технике и может использоваться в многоканальных системах кодирования и сбора аналоговой информации. Технический результат состоит в увеличении быстродействия аналого-цифрового преобразователя. Предлагается многоканальный аналого-цифровой преобразователь, состоящий из нескольких канальных ступеней, число которых равно числу обслуживаемых каналов, и общей для всего преобразователя управляющей части, содержащей генератор тактовых импульсов, два R-S-триггера режима, счетчики старших и младших разрядов уравновешивающего сигнала, цифроаналоговый преобразователь, вычитающее устройство, буферный регистр, пять элементов И, элемент ИЛИ, а каждая канальная ступень состоит из двух аналоговых ключей, вычитающего устройства, устройства выборки-хранения, компаратора, счетчика старших и счетчика младших разрядов канального кода, трех одновибраторов, формирователя импульсов, четырех элементов И, трехвходового элемента ИЛИ и связей между ними. 2 ил.

Многоканальный аналого-цифровой преобразователь, состоящий из нескольких канальных ступеней, число которых равно числу обслуживаемых каналов, и общей для всего преобразователя управляющей части, содержащей генератор тактовых импульсов, первый R-S-триггер режима, счётчик старших разрядов уравновешивающего сигнала, цифроаналоговый преобразователь, вычитающее устройство, буферный регистр, первый и второй элементы И, элемент ИЛИ, первый выход генератора тактовых импульсов подключён к первым входам элементов И, второй вход первого элемента И соединён с клеммой запуска преобразователя, а выход, через двухвходовой элемент ИЛИ, – с S-входом первого R-S-триггера режима, выход которого подключён к второму входу второго элемента И, выход которого подключён к счётному входу счётчика старших разрядов уравновешивающего сигнала, соединённого выходами с информационными входами старших разрядов цифроаналогового преобразователя, выход которого подключён к одному из входов вычитающего устройства, другой вход которого соединён с входной клеммой напряжения смещения, каждая канальная ступень преобразователя состоит из устройства выборки-хранения, компаратора, счётчика старших разрядов канального кода, одновибратора, первого элемента И, трёхвходового элемента ИЛИ, выход трёхвходового элемента ИЛИ через одновибратор соединён с управляющим входом устройства выборки-хранения, выход которого подключён к первому входу компаратора, соединённого вторым входом с выходом цифроаналогового преобразователя, а выходом – с первым входом первого элемента И, подключённого выходом к счётному входу счётчика старших разрядов канального кода, выходы которого соединены с соответствующими входами буферного регистра, выходы которого являются информационными выходами преобразователя, в управляющую часть дополнительно введены второй R-S-триггер режима, счётчик младших разрядов уравновешивающего сигнала, третий, четвёртый и пятый элементы И, а в каждую канальную ступень - вычитающее устройство, два аналоговых ключа, счётчик младших разрядов канального кода, второй и третий одновибраторы, формирователь импульсов, второй, третий и четвёртый элементы И, выход вычитающего устройства управляющей части через первый аналоговый ключ соединён с первым входом вычитающего устройства и выходом второго аналогового ключа, подключённого входом к выходу цифроаналогового преобразователя, второй вход канального вычитающего устройства подключён к входной клемме соответствующего канала, а выход соединён со входом устройства выборки-хранения, выход компаратора подключён к первым входам второго и третьего элементов И, входу формирователя импульсов, соединённого выходом с первым входом четвёртого элемента И канальной ступени, выход второго элемента И канальной ступени подключён к счётному входу счётчика младших разрядов канального кода, соединённого выходами с соответствующими входами буферного регистра, выход третьего элемента И соединён с первым входом трёхвходового элемента ИЛИ и, через второй одновибратор, - с управляющим входом второго аналогового ключа соответствующей канальной ступени, выход четвёртого элемента И соединён с вторым входом трёхвходового элемента ИЛИ и, через третий одновибратор, - с управляющим входом первого аналогового ключа соответствующей канальной ступени, S-вход первого R-S-триггера режима соединён с третьими входами трёхвходовых элементов ИЛИ канальных ступеней, а выход - с вторыми входами четвёртых элементов И канальных ступеней и с первым входом четвёртого элемента И управляющей части, S-вход второго и R-вход первого R-S-триггеров режима объединены и подключены к выходу переполнения счётчика старших разрядов уравновешивающего сигнала и к вторым входам третьих элементов И канальных ступеней, выход второго R-S-триггера режима соединён с первыми входами третьего и пятого элементов И управляющей части, вторые входы четвёртого и пятого элементов И управляющей части объединены и подключены к второму выходу генератора тактовых импульсов, выход четвёртого элемента И управляющей части подключён к вторым входам первых элементов И канальных ступеней, а выход пятого элемента И управляющей части соединён с вторыми входами вторых элементов И канальных ступеней, вторые входы второго и третьего элементов И управляющей части объединены и соединены с первым выходом генератора тактовых импульсов, выход третьего элемента И управляющей части соединён со счётным входом счётчика младших разрядов уравновешивающего сигнала, подключённого выходами к информационным входам младших разрядов цифроаналогового преобразователя, выход переполнения счётчика младших разрядов уравновешивающего сигнала соединён с вторым входом элемента ИЛИ управляющей части, с R-входом второго R-S-триггера режима, с управляющим входом записи буферного регистра, с входами обнуления счётчиков младших разрядов канальных кодов и с выходом сигнала готовности преобразователя к передаче данных.

| Вибрационная мельница | 1983 |

|

SU1151303A1 |

| ДВУХКАМЕРНАЯ ИНДУКЦИОННАЯ КАНАЛЬНАЯ ПЕЧЬ | 1993 |

|

RU2079080C1 |

| Бегуны | 1943 |

|

SU68143A1 |

| Стальной поршень для двигателей внутреннего сгорания | 1946 |

|

SU70734A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

Авторы

Даты

2024-03-12—Публикация

2023-05-24—Подача